交换机时钟电路的制作方法

1.本发明涉及时钟技术领域,尤其涉及一种交换机时钟电路。

背景技术:

2.交换机的数字系统在处理信号时是按节拍一步一步地进行的,系统各部分也是按节拍做的,要使电路的各部分统一节拍就需要一个“时钟信号”,产生这个时钟信号的电路就是时钟电路。

3.传统的交换机原始的每一组时钟采用一个单独的时钟源,当应用在高端交换机产品线,因为高端交换机的网口比较多,用到的参考时钟会比较多,导致精度不高,且每一组的联系性也不好。

4.因此,有必要提供一种交换机时钟电路以解决上述问题。

技术实现要素:

5.本发明的目的在于提供一种时钟精确性高、信号稳定的交换机时钟电路以解决上述技术问题。

6.为实现上述目的,本发明采用如下技术方案:

7.一种交换机时钟电路,包括集成电路芯片单元、与所述集成电路芯片单元连接的时钟输入电路单元和滤波稳压电路单元,所述集成电路芯片单元包括芯片,所述时钟输入电路单元设有钟振x1,所述钟振x1为芯片提供一个既定波动频率的有源钟振,所述滤波稳压电路单元包括均与所述芯片连接的隔离元件和滤波组件,所述芯片u1连接有耦合隔直路电路单元,所述耦合隔直路电路单元输出多路lvds差分时钟电路,还包括同步时钟输入单元,用于对输出的时钟偏差进行调整。

8.作为本发明进一步改进的技术方案,所述芯片u1的8脚与所述钟振x1的3脚连接,所述时钟输入电路单元还包括电阻r13、电阻(r14),所述电阻r13、所述电阻r14依次串联的连接在所述钟振x1的3脚与所述芯片u1的8脚之间。

9.作为本发明进一步改进的技术方案,所述时钟输入电路单元还包括磁珠l1、电容c12、电容c13,所述磁珠l1与所述钟振x1的4脚连接,所述电容c12、所述电容c13并联后的一端连接在所述磁珠l1和所述钟振x1的4脚之间,另一端接地。

10.作为本发明进一步改进的技术方案,所述时钟输入电路单元(20)还包括电容c10、电容c14,所述电容c10、所述电容c14一端连接于所述电阻r14与所述芯片u1的8脚之间,所述电容c14的另一端接地。

11.作为本发明进一步改进的技术方案,所述隔离元件包括磁珠l2、磁珠l9、磁珠l11,所述磁珠l2、l9、l11为95ohm-145ohm的磁珠。

12.作为本发明进一步改进的技术方案,所述磁珠l2与所述芯片u1的13脚连接,所述磁珠l9、所述磁珠l11并联后与所述芯片u1的46脚、60脚连接。

13.作为本发明进一步改进的技术方案,所述滤波组件选择电感滤波l-c,包括磁珠

l3、磁珠l4、磁珠l5、磁珠l6、磁珠l7、磁珠l8、磁珠l10、磁珠l12、磁珠l13、磁珠l14,所述磁珠为480ohm-720ohm的高阻抗磁珠。

14.作为本发明进一步改进的技术方案,所述芯片u1是型号为au5315的可编程时钟芯片。

15.作为本发明进一步改进的技术方案,所述的交换机时钟电路,还包括与所述集成电路芯片单元连接的控制单元,所述控制单元为通讯接口,所述芯片u1通过内部外围i2c或者spi总线接口进行编程,所述控制单元通过i2c或者spi总线接口,进行配置或者进行输出不同时钟。

16.作为本发明进一步改进的技术方案,所述的交换机时钟电路,还包括与所述集成电路芯片单元连接的外围配置电路单元。

17.相较于现有技术,本发明的有益效果在于:

18.1、采用一颗高精度且可编程时钟芯片芯片u1驱动后端负载的电路,通过单一精准的外围钟振x1提供时钟源给这颗时钟芯片u1,可以输出8路不同形式的差分时钟给到负载端,内部精准倍频,该时钟走线不长,产生的信号不容易震荡,产品稳定;

19.2、共用一颗外围钟振x1来倍频,不用每一路都加钟振,每一路时钟误差较小、节省电路空间钟振;

20.3、所述差分时钟电路可以给到后端cpu负载进行工作,电路信号具有伏值低、抗干扰强、精度高等等特点,可以保证后端有近25gbps的速率传输能力。

附图说明

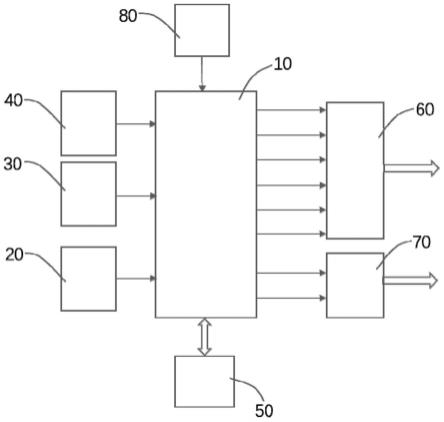

21.图1是本发明交换机时钟电路的框图;

22.图2是图1的电路图;

23.图3是图2中时钟输入电路单元的电路图;

24.图4是图2中滤波稳压电路单元的电路图;

25.图5是图2中外围配置电路单元的电路图;

26.图6是图2中耦合隔直路电路单元的电路图;

27.图7是图2中同步时钟输入单元的电路图。

具体实施方式

28.下面将结合附图详细地对本发明示例性具体实施方式进行说明。如果存在若干具体实施方式,在不冲突的情况下,这些实施方式中的特征可以相互组合。当描述涉及附图时,除非另有说明,不同附图中相同的数字表示相同或相似的要素。以下示例性具体实施方式中所描述的内容并不代表与本发明相一致的所有实施方式;相反,它们仅是与本发明的权利要求书中所记载的、与本发明的一些方面相一致的装置、产品和/或方法的例子。

29.在本发明中使用的术语是仅仅出于描述具体实施方式的目的,而非旨在限制本发明的保护范围。在本发明的说明书和权利要求书中所使用的单数形式的“一种”、“所述”或“该”也旨在包括多数形式,除非上下文清楚地表示其他含义。

30.应当理解,本发明的说明书以及权利要求书中所使用的,例如“第一”、“第二”以及类似的词语,并不表示任何顺序、数量或者重要性,而只是用来区分特征的命名。同样,“一

个”或者“一”等类似词语也不表示数量限制,而是表示存在至少一个。除非另行指出,本发明中出现的“前”、“后”、“上”、“下”等类似词语只是为了便于说明,而并非限于某一特定位置或者一种空间定向。“包括”或者“包含”等类似词语是一种开放式的表述方式,意指出现在“包括”或者“包含”前面的元件涵盖出现在“包括”或者“包含”后面的元件及其等同物,这并不排除出现在“包括”或者“包含”前面的元件还可以包含其他元件。本发明中如果出现“若干”,其含义是指两个以及两个以上。

31.参见图1至图7,本发明揭示一种交换机时钟电路,包括集成电路芯片单元10、与集成电路芯片单元10连接的时钟输入电路单元20和控制单元50。

32.集成电路芯片单元10包括型号为au5315的芯片u1,所述芯片u1是一款可编程时钟芯片,工作之前需要连接电源。具体的,芯片u1的13脚、46脚、60脚为控制电源输入管脚,在保证3.3v的输入下产品能够简单的工作,外部总线接口可以工作。

33.参见图2和图4,芯片u1的13脚、46脚、60脚与滤波稳压电路单元30连接。而滤波稳压电路单元30为电源滤波电路,电源电压为3.3v,采用隔离组件进行隔离,优选的,隔离组件包括的磁珠l2、磁珠l9、磁珠l11,所述磁珠l2、l9、l11为95ohm-145ohm之间(约20%的tolerance)的磁珠,作为优选方式,磁珠l2、l9、l11采用在100mhz频率下120ohm阻抗的磁珠,避免有噪声引入,有效防止因高频噪声串扰到电源端。输出的时钟电路稳定性高,在高速速率在工作时不会产生丢包甚至不连接问题。

34.滤波稳压电路单元30采用滤波组件进行滤波,如图4所示,滤波组件采用电感滤波l-c,提高电源的干净度,此部分电感滤波l-c包括的磁珠l3、磁珠l4、磁珠l5、磁珠l6、磁珠l7、磁珠l8、磁珠l10、磁珠l12、磁珠l13、磁珠l14,具体的,磁珠l3、l4、l5、l6、l7、l8、l10、l12、l13、l14选择480ohm-720ohm之间(约20%的tolerance)的高抗磁珠。作为优选方式,磁珠l3、l4、l5、l6、l7、l8、l10、l12、l13、l14采用在100mhz频率下有600ohm阻抗的磁珠,有效防止因高频噪声串扰到电源端。

35.芯片u1的7脚、8脚、9脚、10脚为外部时钟输入管脚,芯片u1的8脚、9脚与时钟输入电路单元20连接。

36.参见图2和图3,时钟输入电路单元20设有钟振x1,钟振x1为芯片u1提供一个48.0012mhz有源钟振,以保证时钟的精确性,芯片u1通过内部外围i2c(inter-integrated circuit)或者全双工同步串行spi总线接口进行编程。

37.具体的,如图3所示,钟振x1的3脚与芯片u1的8脚连接,时钟输入电路单元20包括电阻r13、电阻r14,电阻r13、电阻r14依次串联的连接在钟振x1的3脚与芯片u1的8脚之间,电阻r13与钟振x1的3脚连接,电阻r14与芯片u1的8脚连接。

38.继续参见图3,时钟输入电路单元20还包括磁珠l1、电容c12、电容c13、电容c10、电容c14,具体的,磁珠l1一端与电源连接,另一端与钟振x1的4脚连接,电容c12、电容c13并联后一端连接在磁珠l1和钟振x1的4脚之间,另一端接地。钟振x1的1脚与时钟输入电路单元20包括的电阻r16连接,电阻r16另一端与电源连接。钟振x1的2脚接地。优选的,磁珠l1选择120ohm进行隔离,经过后端过滤且电容耦合后给到芯片u1作为基准时钟。

39.钟振x1采用有源钟振,保证至少有20ppm的频偏,可以满足有较好的频偏相应,为芯片u1提供一个外部的基准时钟,满足内部分频。

40.电容c10、电容c14连接在电阻r14与芯片u1的8脚之间,电容c14另一端接地。时钟

输入电路单元20包括的电阻r15、电容c17串联后一端连接在电阻r14和电容c10之间,另一端接地。

41.时钟输入电路单元20用于输入一个纯净的时钟源给到芯片u1集成电路工作,通过输入一个稳定纯净时钟后内部在进行分频等电路来达到满足需求输出。

42.芯片u1的13脚与滤波稳压电路单元30的磁珠l2连接,磁珠l2的另一端与电源连接。滤波稳压电路单元30的磁珠l9、磁珠l11并联后与芯片u1的46脚、60脚连接。

43.芯片u1的22脚、57脚、52脚、49脚、43脚、40脚、36脚、33脚、29脚、26脚为内部时钟电路电源管脚,如图4所示,滤波稳压电路单元30包括的磁珠l3、电容c23与芯片u1的26脚连接,电容c23另一端接地,磁珠l3的另一端与电源连接;包括的磁珠l4、电容c26与芯片u1的29脚连接,电容c26另一端接地,磁珠l4的另一端与电源连接;包括的磁珠l5、电容c27与芯片u1的33脚连接,电容c27另一端接地,磁珠l5的另一端与电源连接;包括的磁珠l6、电容c28与芯片u1的36脚连接,电容c28另一端接地,磁珠l6的另一端与电源连接;包括的磁珠l7、电容c29与芯片u1的40脚连接,电容c29另一端接地,磁珠l7的另一端与电源连接;包括的磁珠l8、电容c30与芯片u1的43脚连接,电容c30另一端接地,磁珠l8的另一端与电源连接;包括的磁珠l10、电容c31与芯片u1的49脚连接,电容c31另一端接地,磁珠l10的另一端与电源连接;包括的磁珠l12、电容c32与芯片u1的52脚连接,电容c32另一端接地,磁珠l12的另一端与电源连接;包括的磁珠l13、电容c33与芯片u1的57脚连接,电容c33另一端接地,磁珠l13的另一端与电源连接;包括的磁珠l14、电容c37与芯片u1的22脚连接,电容c37另一端接地,磁珠l14的另一端与电源连接。其中,芯片u1的65脚接地。

44.继续参见图4,滤波稳压电路单元30包括的电容c24、电容c25并联后一端连接在磁珠l2和芯片u1的13脚之间,另一端接地。滤波稳压电路单元30包括的电容c34、电容c35、电容c36一端与芯片u1的46脚和60脚连接,另一端接地。

45.芯片u1的16脚、17脚、18脚、19脚、39脚为接口电路管脚,该接口电路分别是spi或者i2c总线,用于连接前端mcu。具体的,mcu接到spi或者i2c总线,给到芯片u1进行烧录,烧录作用主要是为了让这颗可编辑时钟电路输出不同频率要求,满足不同产品应用,其中包括156.25mhz、125mhz、50mhz的lvds时钟信号。

46.芯片u1的17脚、19脚、39脚与外围配置电路单元40连接。具体的,参见图2和图5,外围配置电路单元40为配置电路,外围可以灵活配置高、低电平,其包括四个配置电路,第一个配置电路为dpll_in_sel0管脚和dpll_in_sel1管脚连接的外围电路,通过二进制设置成00、01、10、11,通过上拉、下拉来设置高低电平,进行输入时钟同步通道的选择。其中,上拉就是将不确定的信号通过一个电阻钳位在高电平,电阻同时起限流作用;下拉也是将不确定的信号通过一个电阻钳位在低电平。第二个配置电路为dpll_oeb管脚所接的外围电路,配置说明要求输出是允许还是关闭。第三个配置电路为dpll_lolb管脚连接的外围电路,用于设置是否要锁存,默认是要锁存的,也就是为高电平,芯片u1内部有上拉。第四个配置电路为dpll_i2caddr_a0和dpll_i2caddr_a1两个管脚连接的外围电路,根据二进制设置00、01、10、11。通常前端主控跟集成电路的芯片u1通过i2c进行通讯,作为从设备,需要有对应地址来接洽,dpll_i2caddr_a0、dpll_i2caddr_a1两个配置管脚用来对集成电路配置地址。

47.芯片u1的3脚、4脚主要为配置管脚,可以配置不同时钟比较。如图5所示,外围配置电路单元40包括电阻r20、电阻r21、电阻r26、电阻r27和电阻r28。其中,电阻r20一端与电源

连接,另一端与芯片u1的4脚连接;电阻r21一端与电源连接,另一端与芯片u1的3脚连接;电阻r26一端与芯片u1的17脚连接,另一端接地;电阻r27一端与芯片u1的19脚连接,另一端接地;外围配置电路单元40包括的电阻r28一端与电源连接,另一端与芯片u1的39脚。

48.芯片u1的6脚为可编程逻辑芯片的复位管脚,可以下拉保持10ms可以复位,满足在有些特殊状况下输出不正确进行简单的复位。

49.继续参见图5,外围配置电路单元40还包括电阻r22、电阻r24、电阻r25和电容c22,电阻r22一端与电源连接,另一端与芯片u1的6脚连接,电容c22串联设置在电阻r22和芯片u1的6脚之间。电阻r24一端与芯片u1的11脚连接,另一端接地。电阻r25一端与电源连接,另一端与芯片u1的12脚连接。

50.参见图2,控制单元50为通讯接口,此接口是cpu跟芯片u1进行通讯作用,通过i2c或者spi接口来控制输出不同时钟等,既可以进行配置,也可以进行输出。

51.控制单元50包括与芯片u1的16脚对应的dpll_i2c_scl接口、与芯片u1的17脚对应的dpll_i2caddr_a1接口、与芯片u1的18脚对应的dpll_i2c_sda接口、与芯片u1的19脚对应的dpll_i2caddr_a0接口、与芯片u1的39脚对应的dpll_i2c_sel接口。

52.集成电路芯片单元10连接有耦合隔直路电路单元,通过耦合隔直路电路单元输出10路lvds差分时钟电路,具体的,参见图2和图6,耦合隔直路电路单元包括第一耦合隔直路电路单元60和第二耦合隔直路电路单元70,第一耦合隔直路电路单元60连接第一负载端,第二耦合隔直路电路单元70连接第二负载端。

53.继续参见图6,芯片u1输出10路lvds差分时钟电路,本实施例的应用电路共用到6路156.25mhz lvds输出,1路125mhz lvds输出,1路50mhz lvds输出,共输出8组时钟,8组时钟给到后端交换芯片。交换芯片要有高速的传输,需要稳定的时钟作为参考,且交换芯片拥有较多光模块口,比如,1gbps、10gbps、25gbps、100gbps等,需要拥有较为稳定的时钟做参考才能有高的传输速率,而采用电容耦合,前后端的中心电压不会受到影响,它只是单纯作为lvds交流信号,满足lvds协议震荡幅度要求即可,如果后端需要变更中心电压,可以再采用上下拉电阻。

54.芯片u1输出10路lvds差分时钟电路,最大输出350mhz的时钟电路,可以满足最小lvds摆幅,对emi具有较好效果。所述差分时钟电路可以给到后端cpu负载进行工作,且此电路信号具有伏值低、抗干扰强、精度高等特点,可以保证后端可以有近25gbps的速率传输能力。

55.芯片u1给出8组时钟给到后端负载,每一路有相关联,做到精度更高,且可以形成闭环调节使用。

56.如图6所示,第一耦合隔直路电路单元60为输出156.25mhz的lvds差分时钟,给cpu内部的phy工作。第一耦合隔直路电路单元60包括的电容c1、电阻r1并联后与芯片u1的59脚连接;包括的电容c2、电阻r3并联后与芯片u1的58脚连接;包括的电容c3、电容c4与芯片u1的54脚、53脚连接;包括的电容c5、电容c6与芯片u1的51脚、50脚连接;包括的电容c7、电容c8与芯片u1的45脚、44脚连接;包括的电容c9、电容c11与芯片u1的42脚、41脚连接;包括的电容c15、电容c16与芯片u1的38脚、37脚连接;包括的电阻r17与芯片u1的35脚连接。

57.继续参见图6,第二耦合隔直路电路单元70为输出125m和50m的lvds差分时钟,给phy芯片工作。第二耦合隔直路电路单元70包括的电容c18、电容c19与芯片u1的28脚、27脚

连接;包括的电容c20、电容c21与芯片u1的24脚、23脚连接。

58.参见图2和图7,芯片u1的1脚、2脚、14脚、15脚、61脚、62脚、63脚、64脚与同步时钟输入单元80连接。

59.同步时钟输入单元80同步对集成电路输出的闭环,用于对输出的时钟偏差进行调整。

60.具体的,同步时钟输入单元80的输入是通过第一负载端、第二负载端反馈给到芯片u1,芯片u1收到第一负载端、第二负载端反馈的信号,以此信号基准来调节输出时钟,芯片u1可以对比第一负载端、第二负载端输出的信号进行调节,让整个输出可以保证较好的精度,满足很多us级别的应用场景,完成闭环。

61.参见图7,同步时钟输入单元80包括的电阻r4一端与u1的63脚连接,另一端接地;包括的电阻r7一端与u1的64脚连接,另一端接地;包括的电阻r8一端与u1的1脚连接,另一端接地;包括的电阻r9一端与u1的2脚连接,另一端接地;包括的电阻r6一端与u1的14脚连接,另一端接地;包括的电阻r10一端与u1的15脚连接,另一端接地;包括的电阻r11一端与u1的61脚连接,另一端接地;包括的电阻r12一端与u1的62脚连接,另一端接地;包括的电阻r2一端连接在电阻r4和芯片u1的63脚之间,另一端接地;包括的电阻r5一端连接在电阻r8和芯片u1的1脚之间,另一端接地。

62.综上所述,本发明的电路构成主要采用一颗高精度且可编程时钟芯片芯片u1驱动后端负载的电路,时钟输入电路单元20的钟振x1能够提供一个48.0012mhz有源钟振来保证时钟的精确性;芯片u1通过内部外围i2c或者spi总线接口进行编程,可以输出10路lvds差分电路,所述差分时钟电路可以给到后端cpu负载进行工作,电路信号具有伏值低、抗干扰强、精度高等等特点,可以保证后端有近25gbps的速率传输能力;此外,该时钟走线不长,产生的信号不容易震荡,产品稳定;通过单一精准的外围钟振x1提供时钟源给这颗时钟芯片u1,可以输出8路不同形式的差分时钟给到负载端,内部精准倍频,共用一颗外围钟振来倍频,不用每一路都加钟振,每一路时钟误差较小、节省电路空间。

63.以上实施例仅用于说明本发明而并非限制本发明所描述的技术方案,对本说明书的理解应该以所属技术领域的技术人员为基础,例如对“前”、“后”、“左”、“右”、“上”、“下”等方向性的描述,尽管本说明书参照上述的实施例对本发明已进行了详细的说明,但是,本领域的普通技术人员应当理解,所属技术领域的技术人员仍然可以对本发明进行修改或者等同替换,而一切不脱离本发明的精神和范围的技术方案及其改进,均应涵盖在本发明的权利要求范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1