用于DP接口的视频像素时钟恢复方法与结构与流程

用于dp接口的视频像素时钟恢复方法与结构

技术领域

1.本发明涉及dp视频信号技术领域,尤其涉及用于dp接口的视频像素时钟恢复方法与结构。

背景技术:

2.dp接口协议中,数据传输依赖于一至四条高速链路。每条链路的速率最小为1.62gbps。进行视频传输应用时,dp发送端对视频数据进行编码后发送。而dp接收端需要进行时钟恢复,以得到像素时钟,即视频像素传输频率,从而以像素为单位处理接收到的视频数据。根据dp协议规定,发送端需在数据流中发送一组m值和n值,这两个值的比值应与dp高速链路的速率与目标像素时钟速率的比值相等。dp接收端可以通过处理这两个值,使用数字pll进行时钟恢复,从而得到像素时钟的频率并产生像素时钟信号,用于内部视频数据处理。

3.在此前完全按照dp协议设计的电路中,数字电路使用从发送端解码的m值和n值从高速链路时钟生成像素时钟。但实际应用中发现生成像素时钟的过程中,由于发送端可能打开了扩频时钟ssc,高速链路时钟频率可能带有一定波动,又由于dp发送端发送m值和n值的频率较低、速度较慢,实时性比较差,因此在初始阶段内m值和n值可能无法精确对应高速链路时钟频率,dp接收端需要较长时间适应变化的高速链路时钟,即导致时钟恢复需要工作较长时间才能稳定。

技术实现要素:

4.本发明的技术问题是提供一种用于dp接口的视频像素时钟恢复方法与结构,不使用dp发送端发送的m值和n值,自行生成一组m值与n值参与目标像素时钟的恢复,提高目标像素时钟进入稳定状态的速度。

5.为实现上述目的,本发明采取的技术方案为:

6.用于dp接口的视频像素时钟恢复方法,包括以下步骤:dp解码获得目标信号;其中目标信号包括:每行视频数据发送产生的结束标志信号和每行视频数据的像素数;通过高速链路时钟对目标信号进行采样;基于相邻两个结束标志信号计算得到对应行的参考时钟计数;取像素数为m值,取参考时钟计数为n值,恢复对应行的视频数据中每一像素的目标像素时钟。本发明通过dp解码获得目标信号,根据目标信号自行生成另一组m值和n值进行目标像素时钟的恢复,不需要使用发送端解码的m、n值,克服了现有技术中发送端会打开ssc,造成高速链路时钟波动,导致m、n值无法精确对应高速链路时钟,使时钟恢复需要工作较长时间才能稳定的技术问题,可以快速且准确地进行时钟恢复,避免ssc带来的潜在误差。

7.进一步地,基于相邻两个结束标志信号计算得到对应行的参考时钟计数,包括:使用低速参考时钟记录相邻两个结束标志信号上升沿之间的时间,得到参考时钟计数。

8.进一步地,取像素数为m值,取参考时钟计数为n值,恢复目标像素时钟,包括:通过除法运算获得m值与n值的比值;通过调制器对比值的小数部分进行调制,输出调制整数值;

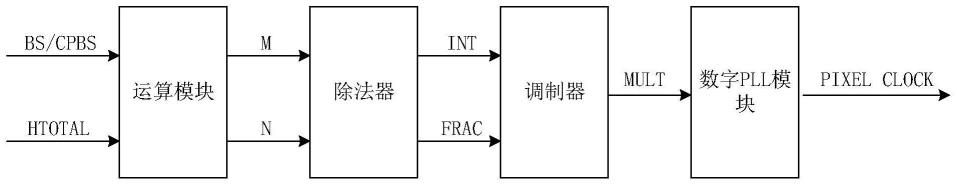

数字pll模块根据调制整数值计算恢复对应行的视频数据中每一像素的目标像素时钟。

9.用于dp接口的视频像素时钟恢复结构,包括dp发送端和dp接收端,dp发送端包括编码模块;dp接收端包括前级电路、运算模块、除法器、调制器和数字pll模块;前级电路的接收端连接编码模块的发送端,前级电路的发送端连接运算模块的接收端,运算模块的发送端连接除法器的接收端,除法器的发送端连接调制器的接收端,调制器的发送端连接数字pll模块的接收端;前级电路,用于获取目标信号,其中目标信号包括:每行视频数据发送产生的结束标志信号和每行视频数据的像素数;并基于结束标志信号获得参考时钟计数;运算模块,用于将视频数据的像素数赋值给m,将参考时钟计数赋值给n;除法器,用于通过除法运算获得m与n的比值的整数和小数部分;调制器,用于对m与n的比值的小数部分进行调制,输出调制整数值;数字pll模块,用于根据调制整数值计算恢复对应行的视频数据中每一像素的目标像素时钟。

10.进一步地,前级电路包括:解码模块和数字模块;解码模块,用于从dp发送端解码获得目标信号;数字模块,用于通过高速链路时钟对目标信号进行采样,并通过低速参考时钟记录相邻两个结束标志信号上升沿之间的时间,得到参考时钟计数。

附图说明

11.通过阅读参照以下附图对非限制性实施例所作的详细描述,本发明及其特征、外形和优点将会变得更加明显。在全部附图中相同的标记指示相同的部分。并未刻意按照比例绘制附图,重点在于示出本发明的主旨。

12.图1是本发明提供的用于dp接口的视频像素时钟恢复方法的流程图;

13.图2是本发明提供的用于dp接口的视频像素时钟恢复结构的示意图;

具体实施方式

14.下面结合附图和具体的实施例对本发明作进一步的说明,但是不作为本发明的限定。

15.现有技术中,数字电路普遍实用dp发送端解码的m值和n值从高速链路时钟生成目标像素时钟,dp协议的m、n值分别对应的是目标像素时钟速率和高速链路时钟速率,但在实际应用中发现,通过该方式生成目标像素时钟的过程中,发送端有可能会打开了扩频时钟ssc,由于从dp发送端获得的m、n值更新频率较慢,扩频时钟ssc又导致高速链路时钟带有一定波动,进而使得m、n值无法精准对应高速链路时钟的频率,从而导致时钟恢复需要工作较长时间才能稳定。

16.为了解决上述技术问题,本发明提供一种用于dp接口的视频像素时钟恢复方法,如图1所示,包括以下步骤:首先通过dp解码获得目标信号;其中目标信号包括:每行视频数据发送产生的结束标志信号和每行视频数据的像素数;每行视频数据发送产生的结束标志信号具体指bs信号或cpbs信号,实际是bs信号还是cpbs信号是由dp协议规定的,取决于dp视频传输是否打开hdcp模式,在hdcp模式下使用cpbs信号,否则使用bs信号,两者在各自模式下实现的功能是一样的。每行视频数据的像素数具体指htotal信号,由dp协议规定,视频格式中每行的像素数,即htotal应在msa数据包中以每帧发送一次的频率更新。

17.接着数字模块通过高速链路时钟对bs信号或cpbs信号进行采样,使用低速参考时

钟记录相邻两个bs信号或cpbs信号上升沿之间的时间,得到对应行的参考时钟计数ref_cnt,在该时间区间内,视频信号完成一行像素的传输,其像素数为htotal。

18.然后取像素数为m值,取参考时钟计数为n值,即本发明中的m、n值分别对应的是目标像素时钟速率和参考时钟速率,接着通过除法器进行除法运算获得m值与n值的比值的整数部分int与小数部分frac,再通过调制器delta-sigma对比值的小数部分进行调制,输出调制整数值mult,调制的作用是把m/n获得的小数部分转化成单一的整数并输出给数字pll模块,例如,若m/n=9.7,delta-sigma调制器会在70%的时间里输出10,30%的时间里输出9,这样平均下来数字pll模块获得的就是9.7,最后数字pll模块根据调制整数值mult计算恢复对应行的视频数据中每一像素的目标像素时钟pixel clock,具体公式参照(m/n)*参考时钟频率=目标时钟频率。

19.本发明还提供了用于dp接口的视频像素时钟恢复结构,如图2所示,包括dp发送端和dp接收端,dp发送端包括编码模块;dp接收端包括前级电路、运算模块、除法器、调制器和数字pll模块;前级电路的接收端连接编码模块的发送端,前级电路的发送端连接运算模块的接收端,运算模块的发送端连接除法器的接收端,除法器的发送端连接调制器的接收端,调制器的发送端连接数字pll模块的接收端;前级电路,用于获取目标信号,其中目标信号包括:每行视频数据发送产生的结束标志信号和每行视频数据的像素数;并基于结束标志信号获得参考时钟计数;前级电路包括:解码模块和数字模块;解码模块,用于从dp发送端解码获得目标信号;数字模块用于通过高速链路时钟对目标信号进行采样,并通过低速参考时钟记录相邻两个结束标志信号上升沿之间的时间,得到参考时钟计数。运算模块用于将视频数据的像素数赋值给m,将参考时钟计数赋值给n;除法器用于通过除法运算获得m与n的比值的整数和小数部分;调制器用于对m与n的比值的小数部分进行调制,输出调制整数值;数字pll模块用于根据调制整数值计算恢复对应行的视频数据中每一像素的目标像素时钟。

20.综上所述,本发明自行生成另一组m值和n值进行目标像素时钟的恢复,不需要使用发送端解码的m、n值,克服了现有技术中发送端会打开ssc,造成高速链路时钟波动,导致m、n值无法精确对应高速链路时钟,使时钟恢复需要工作较长时间才能稳定的技术问题,可以快速且准确地进行时钟恢复,避免ssc带来的潜在误差,同时减少dp接口从接入到视频信号输出的等待时间。此外,使从由晶振产生的低速参考时钟和整数pll模块生成目标像素时钟,能在简化电路设计难度的同时提高稳定性,进一步保证同时可以保证像素时钟频率在更短的时间内进入稳定状态,加快视频输出流程,提升用户体验。

21.以上对本发明的较佳实施例进行了描述;需要理解的是,本发明并不局限于上述特定实施方式,其中未尽详细描述的设备和结构应该理解为用本领域中的普通方式予以实施;任何熟悉本领域的技术人员,在不脱离本发明技术方案作出许多可能的变动和修饰,或修改为等同变化的等效实施例,这并不影响本发明的实质内容;因此,凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所做的任何简单修改、等同变化及修饰,均仍属于本发明技术方案保护的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1