基于CMOS图像传感器的光学可重构PUF装置

基于cmos图像传感器的光学可重构puf装置

技术领域

1.本发明涉及集成电路硬件安全的技术领域,尤其涉及一种基于cmos图像传感器的光学可重构puf装置。

背景技术:

2.物理不可克隆函数(physical unclonable function,puf)是一项新兴的硬件安全技术,不同于使用非易失性存储器来存储密码的算法,它可以基于半导体芯片在制造过程中不可避免的工艺误差(process variation)来产生特定的id,为每一块芯片提供唯一特定的身份认证,类似于人类的“指纹”且这个指纹存储在芯片工艺误差中的,它是不会丢失的不可克隆的。它具有紧凑和低功耗的特点,是一种廉价而有效的安全原语。

3.激励响应对是指对puf输入一个激励,对应其根据自身电路模块的先天不匹配输出一个不可预测的随机响应位。根据产生的激励响应对的多少,可以简单把puf分为弱puf和强puf。弱puf的crp(激励响应对,challenge respond pair)是有限的,它们一般用于随机数生成器或者给设备生成唯一密钥。强puf的crp是呈指数增长的,丰富的熵能带来身份验证上优势。

4.另外,众所周知,以cmos(互补金属氧化物半导体,complementary metal oxide semiconductor)图像传感器为代表的物联网设备得到了迅速的发展和广泛的应用。cmos传感器近年来已经成为摄影领域的主流,并广泛应用于移动端摄像头、安防监视器、无人机和自动驾驶汽车等多种场合。cmos图像传感器规模越来越大的同时,摄像头的可信赖性,数据流传输的信息安全就显得异常重要。但是,当前的图像传感器和终端服务器之间的识别认证系统存在很大的安全隐患,对于前端传感器节点,即使在最先进的通信协议下,它们也始终被认为是不安全的。如果没有对图像传感设备的可靠认证,记录的图像或视频可以很容易地被许多图像处理算法篡改。特别在现在盛行的人脸识别,人脸支付和监控领域。不法分子就能篡改图像而实现支付,解锁甚至更改安防监控的结果。要是有一款芯片,它有特定的密码库,在使用之前会对它进行身份验证。验证成功才能进行数据流的传输。这样图像安全就会得到很好的保证。因此一款能产生特定密钥,又能做图像传感器的可重构芯片是具有很高研究价值和实际应用价值。

5.现有技术方法中利用复位时产生的复位电压构造了弱puf,其基本原理就是用n管代替了传统架构中的复位管,改善设计稳定性和唯一性结果,但是弱puf只能产生少量的crp应用于设备生成唯一密钥,在身份验证上有明显的不足,导致抗机器学习攻击能力较弱、可靠性不高。此外,目前已有的强 puf芯片是设计特定的电路产生大量crp,无法复用传统电路并与已有的cmos偏振图像传感芯片进行结合使用。因此,现有技术方法具有无法将cmos图像传感芯片与传统电路结构进行结合使用以构造得到高可靠性的物理不可克隆函数装置的问题。

技术实现要素:

6.本发明实施例提供了一种基于cmos图像传感器的光学可重构puf装置,旨在解决现有技术方法中无法将cmos图像传感芯片与传统电路结构进行结合使用以构造得到高可靠性的物理不可克隆函数装置的问题。

7.第一方面,本发明实施例提供了一种基于cmos图像传感器的光学可重构puf装置,所述puf装置包括偏置调节电路、图像传感器、双模式行译码器、列选择器、读出电路及比较器;所述图像传感器为多个像素单元所组成的像素阵列,每一所述像素单元可进行独立感光以输出对应的光感输出电压; 所述偏置调节电路与所述图像传感器中每一列像素单元进行连接,以对每一列像素单元中输入电流的大小进行偏置调节;所述双模式行译码器与每一所述像素单元分别进行连接,用于依次导通每行像素单元或从所述图像传感器的多组像素单元中选择每一组的一行像素单元进行导通,其中每组所述像素单元由多行像素单元组成;所述列选择器通过所述读出电路与每一所述像素单元分别进行连接,所述比较器与所述读出电路进行连接,所述列选择器用于输入选择信号至所述读出电路;所述读出电路用于根据所述选择信号从导通的多行像素单元中选择其中多列像素单元的光感输出电压输出至比较器;所述比较器用于对相邻两列像素单元的光感输出电压进行比较,以根据比较结果输出二进制的随机序列信号。

8.所述的基于cmos图像传感器的光学可重构puf装置,其中,所述偏置调节电路包括尾电流源管及电流镜;所述尾电流源管及所述电流镜分别与一列像素单元中每一所述像素单元的电压输出端进行连接。

9.所述的基于cmos图像传感器的光学可重构puf装置,其中,所述尾电流源管的漏极与所述电流镜及所述像素单元相连接、其源极接地、其栅极用于输入基准电压。

10.所述的基于cmos图像传感器的光学可重构puf装置,其中,所述像素单元包括光电二极管、复位晶体管、源跟随晶体管及行选晶体管;所述复位晶体管的漏极与所述源跟随晶体管的漏极相连接、所述复位晶体管的源极与所述光电二极管的负极及所述源跟随晶体管的栅极相连接、所述源跟随晶体管的源极与所述行选晶体管的漏极相连接,所述光电二极管的正极接地,行选晶体管的栅极与所述双模式行译码器相连接,所述行选晶体管的源极作为所述像素单元的电压输出端。

11.所述的基于cmos图像传感器的光学可重构puf装置,其中,所述复位晶体管的栅极用于输入复位电压,所述复位晶体管的漏极与所述源跟随晶体管的漏极均用于输入稳压电压。

12.所述的基于cmos图像传感器的光学可重构puf装置,其中,调节所述电流镜的偏置电压为每一列像素单元提供稳定的饱和限流,以使所述图像传感器处于成像工作模式。

13.所述的基于cmos图像传感器的光学可重构puf装置,其中,调节所述尾电流源管的偏置电压使每一列像素单元中的源跟随晶体管处于亚阈值区,以使所述图像传感器处于物理不可克隆函数工作模式。

14.所述的基于cmos图像传感器的光学可重构puf装置,其中,所述图像传感器中像素单元的行数为8的倍数,所述图像传感器中共包含8组像素单元。

15.所述的基于cmos图像传感器的光学可重构puf装置,其中,所述图像传感器中像素单元的列数为8的倍数。

16.所述的基于cmos图像传感器的光学可重构puf装置,其中,所述图像传感器中像素单元的列数为8、16、32或64。

17.本发明实施例提供了一种基于cmos图像传感器的光学可重构puf装置,包括偏置调节电路、图像传感器、双模式行译码器、列选择器、读出电路及比较器,图像传感器为多个像素单元所组成的像素阵列,偏置调节电路与每一列像素单元进行连接,双模式行译码器与每一像素单元分别进行连接,列选择器通过读出电路与每一所述像素单元分别进行连接,比较器与读出电路进行连接。上述的puf装置,基于cmos图像传感器主流的aps架构,结合传统电路进行复用,即能满足成像需求又能利用物理不可克隆函数产生密钥,利用图像传感器中像素单元在制造过程中的工艺误差,得到非线性的随机序列信号中包含大量crp,从而得到可抗机器学习攻击的高可靠性强物理不可克隆函数装置。

附图说明

18.为了更清楚地说明本发明实施例技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

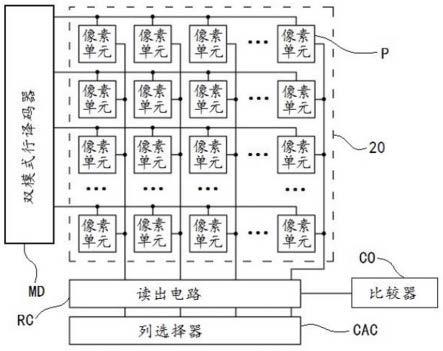

19.图1为本发明实施例提供的基于cmos图像传感器的光学可重构puf装置的整体电路结构图;图2为本发明实施例提供的基于cmos图像传感器的光学可重构puf装置的局部电路结构图;图3为本发明实施例提供的基于cmos图像传感器的光学可重构puf装置的局部单元结构图;图4为本发明实施例提供的基于cmos图像传感器的光学可重构puf装置的效果示意图;图5为本发明实施例提供的基于cmos图像传感器的光学可重构puf装置的另一效果示意图;图6为本发明实施例提供的基于cmos图像传感器的光学可重构puf装置的又一效果示意图;图7为本发明实施例提供的基于cmos图像传感器的光学可重构puf装置的再一效果示意图;图8为本发明实施例提供的基于cmos图像传感器的光学可重构puf装置的后一效果示意图。

具体实施方式

20.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

21.应当理解,当在本说明书和所附权利要求书中使用时,术语“包括”和

ꢀ“

包含”指示所描述特征、整体、步骤、操作、元素和/或组件的存在,但并不排除一个或多个其它特征、整

体、步骤、操作、元素、组件和/或其集合的存在或添加。

22.还应当理解,在此本发明说明书中所使用的术语仅仅是出于描述特定实施例的目的而并不意在限制本发明。如在本发明说明书和所附权利要求书中所使用的那样,除非上下文清楚地指明其它情况,否则单数形式的“一”、“一个”及“该”意在包括复数形式。

23.还应当进一步理解,在本发明说明书和所附权利要求书中使用的术语“和/ 或”是指相关联列出的项中的一个或多个的任何组合以及所有可能组合,并且包括这些组合。

24.请参阅图1至图3,图1为本发明实施例提供的基于cmos图像传感器的光学可重构puf装置的整体电路结构图;图2为本发明实施例提供的基于cmos图像传感器的光学可重构puf装置的局部电路结构图;图3为本发明实施例提供的基于cmos图像传感器的光学可重构puf装置的局部单元结构图。该基于cmos图像传感器的光学可重构puf装置包括偏置调节电路10、图像传感器(image sensor)20、双模式行译码器(2mode-decoder)md、列选择器(column access circuitry)cac、读出电路(readout circuitry)rc及比较器(comparator)co;所述图像传感器is为多个像素单元p所组成的像素阵列,每一所述像素单元p可进行独立感光以输出对应的光感输出电压vout;所述偏置调节电路10与所述图像传感器20中每一列像素单元进行连接,以对每一列像素单元中输入电流的大小进行偏置调节;所述双模式行译码器md与每一所述像素单元分别进行连接,用于依次导通每行像素单元或从所述图像传感器20的多组像素单元中选择每一组的一行像素单元进行导通,其中每组所述像素单元由多行像素单元组成;所述列选择器cac通过所述读出电路rc与每一所述像素单元p分别进行连接,所述比较器co与所述读出电路rc进行连接,所述列选择器cac用于输入选择信号至所述读出电路rc;所述读出电路rc用于根据所述选择信号从导通的多行像素单元中选择其中多列像素单元的光感输出电压输出至比较器co;所述比较器co用于对相邻两列像素单元的光感输出电压进行比较,以根据比较结果输出二进制的随机序列信号。

25.具体的,上述电路结构可在不改变图像传感器中像素单元阵列情况下,通过配置外围电路,利用原有像素单元的复位电压做随机性来源从而产生随机序列信号作为密钥进行使用。

26.在更具体的实施例中,所述偏置调节电路包括尾电流源管m

bias

及电流镜11;所述尾电流源管m

bias

及所述电流镜11分别与一列像素单元中每一所述像素单元p的电压输出端进行连接。在更具体的实施例中,调节所述电流镜11的偏置电压为每一列像素单元提供稳定的饱和限流,以使所述图像传感器20处于成像工作模式。其中,调节所述尾电流源管m

bias

的偏置电压使每一列像素单元中的源跟随晶体管m2处于亚阈值区,以使所述图像传感器20处于物理不可克隆函数工作模式。

27.如图2所示,电路结构中增加配置偏置调节电路,通过在每一列外接一个尾电流源管m

bias

,通过调节电流镜和外接管m

bias

的偏置电压就能实现puf模式和成像模式的切换。除此以外,如图1所示,双模式行译码器md,可在双模式下输出不同的行选信号,该行选信号作用于每一行像素单元内的行选晶体管m3。两种工作模式具体为:成像模式下,掐断外接管mbias,调节电流镜11的偏置电压,以为每一列像素单元提供稳定的饱和电流;复位晶体管m1先导通后关闭,将光信号引入到像素单元内;行选信号依次将每行像素单元的电压导通并通过列线输出至读出电路,列选择器cac和读出电路rc将每一列的输出电压串行扫出,并

通过相关双取样电路(cds,correlated double sampling)接入能将模拟信号转换成数字信号的模拟数字转换器(adc,analog to digital converter)中,其中buffer代表滤波器、放大器等附加元件,转化后的数字信号大小以灰度体现,代表每个像素的模拟电压。

28.例如,在设计的成像矩阵大小为128

×

32时,成像模式下一帧有128

×

32个模拟信号输出。puf模式下,掐断电流镜11,调节外接尾电流源管m

bias

的偏置电压,使得每一列像素单元中的源跟随晶体管m2处于亚阈值区;复位晶体管m1一直处于导通状态,即每个像素单元中的电压为复位电压;为了能得到可抗攻击的最优结果,可对图像传感器20中的像素单元进行分组,例如,双模式行译码器20可虚拟地将128行像素单元每16行分为一组,每组由16选1译码器选一个行像素单元导通,每列的输出信号由导通的8个像素单元的电压共同决定。因为受每个像素工艺偏差的影响,选择不同的像素单元时,每列的输出电压会有所不同,两个列之间的输出电压差通过比较器数字化,输出位是“0”或“1”的 一串二进制码,作为puf响应位r,如对相邻两列像素单元的输出电压进行比较,电压较高的列则输出对应的信号值 为“1”,电压较低的列则输出对应的信号值为“0”,每一列均能输出一个信号值,则所输出的随机序列信号即为仅包含“0”和“1”的二进制信号。所选的行地址由行选信号(数字输入激励r

sel

)确定,由于每两列通过比较能得到puf响应位r,所以32列的像素阵列相当于集成了31!个puf,也即可产生31!种不同的随机序列信号。

29.具体的,所述尾电流源管m

bias

的漏极与所述电流镜11及所述像素单元p相连接、其源极接地、其栅极用于输入基准电压v

bia

。

30.在更具体的实施例中,所述像素单元p包括光电二极管vd、复位晶体管m1、源跟随晶体管m2及行选晶体管m3;所述复位晶体管m1的漏极与所述源跟随晶体管m2的漏极相连接、所述复位晶体管m3的源极与所述光电二极管vd的负极及所述源跟随晶体管m2的栅极相连接、所述源跟随晶体管m2的源极与所述行选晶体管m3的源极相连接,所述光电二极管vd的正极接地,行选晶体管m3的栅极与所述双模式行译码器20相连接,用于输入数字输入激励r

sel

,所述行选晶体管m3的漏极作为所述像素单元p的电压输出端。其中,所述复位晶体管m1的栅极用于输入复位电压v

rst

,所述复位晶体管的漏极与所述源跟随晶体管的漏极均用于输入稳压电压vdd。

31.本实施例中的像素单元p采用的最经典的是基于帧的3-t aps结构。对于3-t aps结构,每一个像素单元均由光电二极管vd、复位晶体管m1、源跟随晶体管m2及行选晶体管m3组成,三个晶体管分别实现复位、信号缓冲和译码器访问电路的开关选择的功能。以3t为例,成像模式先是复位晶体管m1导通,光电二极管vd上面的电压pd复位到高电平vdd,然后复位晶体管m1关闭,光电二极管vd受到光照,光电流由于入射光变大而变大,光电二极管vd开始放电(省略小暗电流),具体过程如图4所示,光电二极管vd的放电速率即为图4中直线的斜率。曝光一段时间后,打开行选晶体管m3,读出该像素单元的输出电压。光电二极管vd节点电压随时间变化图如图4所示,在一定时间(t0)之后扫描每个像素单元的电压,再通过adc把模拟信号转换为数字信号,代表不同的灰度,实现成像功能。其中,复位晶体管m1、源跟随晶体管m2及行选晶体管m3均为nmos晶体管。

32.在puf模式下使用即可在输入电压中引入非线性(随机性),例如,128行像素单元被分为8组,每一列像素单元通过调节尾电流源管m

bias

的偏置电压v

bias

让各个像素单元p的源跟随晶体管m2处于亚阈值区。在管子源漏电压v

ds

大于100mv时,通过像素单元p1和像素单

元p2的亚阈值电流简约地采用公式(1)及公式(2)进行表示为:(1);(2);其中,v

pd

为各像素单元p中光电二极管vd的节点电压;is为像素单元的饱和电流;和分别为像素单元p1和像素单元p2中源跟随晶体管m2的阈值电压;为热电压kt/q,η为预置系数值。

33.从8组像素单元分别选取每一组中一行像素单元进行导通,则对于其中一列所导通的8个像素单元p而言,通过尾电流源管m

bias

的总电流可以采用公式(3)进行表示: (3);其中是尾电流源管m

bias

的偏置电压。因此输出电压可以反推得到公式(4):(4);可以看出各像素单元中源跟随晶体管m2的阈值电压和光电二极管vd节点电压这两个熵源对v

out

的作用是非线性的。这使得puf输出响应成为挑战输入的一个复杂的非线性函数,从而实现了抵御机器学习攻击的性能,也即使得到的物理不可克隆函数装置具有高可靠性。

34.在更具体的实施例中,所述图像传感器中像素单元的行数为8的倍数,所述图像传感器中共包含8组像素单元。具体的,所述图像传感器中像素单元的列数为8的倍数。其中,所述图像传感器中像素单元的列数为8、16、32或64。

35.为提高所输出的随机序列信号的非线性,可设置图像传感器20中像素单元的行数为8的倍数,则对图像传感器进行分组时可得到8组像素单元,也即使每一列所像素单元输出的输出电压为8个像素单元中熵源共同作用的结果,从而确保输出电压具有高随机性。为适用于计算机程序,可设置图像传感器20中像素单元的列数为8的倍数,则所得到的随机序列信号中信号值也为8的倍数。在具体应用过程中,可根据使用需求配置图像传感器中像素单元的列数为8、16、32或64。例如本实施例中图像传感器中像素单元的数量为128(行)

×

32(列),则对应可输入32bit(32位)的随机序列信号。具体的,本实施例的puf装置可采用65nm标准cmos制造工艺制造得到,目前其随机性,温度可靠性以及唯一性都得到了很好的证实,能够广泛适用于物联网(iot)设备,并实现低成本和轻量化的硬件安全应用。通过设计新型的光电传感读出以及数字化电路,得到一种能够与物联网中新型cmos偏振图像传感芯片相结合的强puf硬件装置,在实现puf功能的同时进行感光信息的精确读取,在较小的芯片面积代价下实现系统的双重工作模式,即作为一种集成光学可重构puf的图像传感器进行使用。

36.随机性是指puf生成随机信息源的能力,这是加密密钥管理和设备识别/认证应用的重要特征。为了测试puf电路输出的序列具有随机性,这里采用了广泛使用的nist测试套件测试。对于每个nist测试,通过计算各项测试的p值可以量化puf的随机性水平。通常,

nist测试结果的p值应大于0.01,其产生的信息源才能被视为随机的,置信水平高达99%。如表1所示,来自10个puf实例的输出通过了所有nist测试,表中的p值均大于0.01,表示puf满足了随机性的要求。

37.表1可靠性反映了puf在不同环境下和同样的输入激励的情况下,输出响应能够抵抗环境影响的能力。对可靠性影响最大的环境变量是温度和电压。puf实例的可靠性可以从片内汉明距离(hd)计算。通过比较puf在不同环境条件下对相同输入激励的响应,可以对puf的可靠性进行评估,误码率的计算以及误码率和可靠性之间的关系由以下公式(5)进行表示:(5);式中ri为在一般条件下所测得的puf输出的n位响应,r

i,j

是在该条件下重复第j次输入激励所得到的响应。hd(ri,r

i,j

)表示两者之间的汉明距离,k表示总共测量的次数。

38.据测试芯片仿真结果,对于温度范围(-20℃-80℃)其误码率测试结果如图5所示,对于宽电源电压范围(2.3v-2.8v)其误码率测试结果如图6所示,由图中可以得出,最坏情况下的本实施例的puf装置的可靠性分别为90.7%和94.8%。

39.唯一性反映了同一环境下,相同的输入激励应用于不同的puf芯片时所得到的输出响应的差异。理想值应为50%,服从高斯分布。在相同的环境条件下,我们通过将相同的输入激励应用于不同的puf来比较puf的输出响应,计算出不同芯片之间的片间汉明距离,从而测量puf的唯一性。准确的计算由以下公式(6)表示。其中ru和rv是两个不同的芯片u和v对于相同输入激励的n位响应。

40.(6);在这里,我们通过蒙特卡罗测试在标准电源电压2.5v和室温27℃的工作温度下10个puf实例。图7示出了模间汉明距离分布的概率质量函数,其通过高斯曲线拟合。在每个puf实例具有2000个响应位的情况下,总共相应位为2000bit

×

10,高斯分布的均值为0.4980,标准差为0.0327,对应唯一性为49.8%。

41.从提出的异或puf中测量了10000个随机选择的crp,其中8000个用于训练集,其余

用于测试集。图8示出了作为使用不同ml法(机器学习, machine learning)的训练集大小的函数的预测错误率,其中使用的算法包括svm(支持向量机,support vector machine)及mlp(多层感知机,multilayer perceptron),这些结果还与在仲裁器puf上使用svm攻击的比较结果如图8所示,测试结果证明,本实施例的puf装置能够抵御机器学习攻击。

42.将本实施例中的puf装置与现有技术中的几种强puf 设计进行相关特性的比较,比较结果如表2所示。

43.从比较结果中可以看出, 本实施例中的puf有较高的吞吐,并且 puf 的能耗较现有技术1和现有技术2更低。我们提出的puf在较大的温度范围和工作电压范围内具有出色的唯一性和可靠性。

44.表2*表示丢失42%的crps之后的数据本发明实施例提供了一种基于cmos图像传感器的光学可重构puf装置。包括偏置调节电路、图像传感器、双模式行译码器、列选择器、读出电路及比较器,图像传感器为多个像素单元所组成的像素阵列,偏置调节电路与每一列像素单元进行连接,双模式行译码器与每一像素单元分别进行连接,列选择器通过读出电路与每一所述像素单元分别进行连接,比较器与读出电路进行连接。上述的puf装置,基于cmos图像传感器主流的aps架构,结合传统电路进行复用,既能满足成像需求又能利用物理不可克隆函数产生密钥,利用图像传感器中像素单元在制造过程中的工艺误差,得到非线性的随机序列信号中包含大量crp,从而得到可抗机器学习攻击的高可靠性强物理不可克隆函数装置。

45.以上所述,仅为本发明的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到各种等效的修改或替换,这些修改或替换都应涵盖在本发明的保护范围之内。因此,本发明的保护范围应以权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1