存储设备、存储系统操作方法和计算系统与流程

存储设备、存储系统操作方法和计算系统

1.相关申请的交叉引用

2.本技术要求于2021年7月27日提交的韩国专利申请no.10-2021-0098683和于2022年3月25日提交的韩国专利申请no.10-2022-0037406的优先权,这两件韩国专利申请的共同主题通过引用整体合并于此。

技术领域

3.本发明构思总体上涉及数据存储系统。更具体地,本发明构思涉及能够传递(例如,发送和/或接收)0级同态密文(level-0 homomorphic ciphertext)的主机和存储设备。

背景技术:

4.随着通信技术的发展和电子设备的使用变得更普遍,不断努力寻求维护电子设备之间的通信安全。因此,大多数通信设备和技术使用某种形式的数据加密/解密。

5.从历史上看,当加密的消息在各方之间进行通信时,接收方在针对消息的信息执行另一项操作之前必须对加密的消息进行解密。但是,在解密过程期间,第三方黑客可能访问处于其临时解密状态的数据。

6.为了解决这个潜在的问题,已经研究了某些同态加密方法。与同态加密方法一致,可以对密文执行操作而不必对接收到的加密的消息进行解密。尽管如此,与通过加密对初步文本的操作的结果获得的结果相比,正确的结果可以被获得。因此,可以对密文安全地执行各种操作而不需要对加密的消息进行解密。

技术实现要素:

7.本发明构思的实施例涉及传递具有最小长度的同态密文的存储系统,使得可以使用增加总的数据传输速率的方法来对同态密文进行解密。

8.根据本发明构思的一方面,存储设备可以包括:非易失性存储器,和存储器控制器,所述存储器控制器被配置为:对明文进行加密以生成具有不同级别的同态密文当中的具有第一级别的同态密文,将所述具有第一级别的同态密文存储在所述非易失性存储器中,以及响应于从主机接收的请求提供所述具有第一级别的同态密文,其中,所述具有第一级别的同态密文在所述具有不同级别的同态密文当中具有最小长度。

9.根据本发明构思的一方面,用于包括主机和存储设备的存储系统的存储系统操作方法可以包括:在所述存储设备中,将第一明文加密为具有第一长度的第一同态密文,将所述第一同态密文从所述存储设备传递到所述主机,在所述主机中,响应于所述第一同态密文生成具有第二长度的第二同态密文,以及通过在所述第二同态密文与另一同态密文之间执行运算生成具有所述第一长度的第三同态密文,将所述第三同态密文从所述主机传递到所述存储设备,以及在所述存储设备中,通过对所述第三同态密文进行解密来生成第二明文,其中,所述第一同态密文和所述第三同态密文的所述第一长度是所述第一同态密文和所述第三同态密文中的每一者可解密的最小长度。

10.根据本发明构思的一方面,计算系统可以包括:移动设备,所述移动设备包括被配置为将第一明文加密为具有第一级别的第一同态密文的同态加密电路和被配置为存储所述第一同态密文的存储设备;和服务器,所述服务器被配置为:接收所述第一同态密文,将所述第一同态密文自举为具有第二级别的第二同态密文,通过对所述第二同态密文执行至少一个同态运算来生成具有所述第一级别的第三同态密文,以及向所述移动设备提供所述第三同态密文。

11.根据本发明构思的一个方面,通用闪存(ufs)可以包括:非易失性存储器,所述非易失性存储器被配置为存储数据;接口电路,所述接口电路被配置为从主机接收指令;和ufs设备控制器,所述ufs设备控制器被配置为:响应于所述指令对所述非易失性存储器执行操作以及将对所述指令的响应提供给所述主机,其中,所述ufs设备控制器将从所述主机接收的数据加密为第一同态密文,并且将所述第一同态密文存储在所述非易失性存储器中,所述第一同态密文具有使得所述第一同态密文可解密的最小长度的。

附图说明

12.通过结合附图考虑以下详细描述,可以更清楚地理解本发明构思的优点、益处和特征以及制造和使用,在附图中:

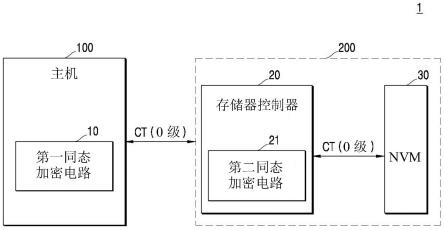

13.图1是示出根据本发明构思的实施例的存储系统的框图;

14.图2是示出根据本发明构思的实施例的同态加密电路的框图;

15.图3是示出根据本发明构思的实施例的加密的图;

16.图4是示出根据本发明构思的实施例的自举运算的图;

17.图5是示出根据本发明构思的实施例的模数切换运算的图;

18.图6是示出根据本发明构思的实施例的乘法运算的图;

19.图7是示出根据本发明构思的实施例的存储系统的框图;

20.图8是示出根据本发明构思的实施例的存储系统操作方法的流程图;

21.图9是示出根据本发明构思的实施例的自举级别的图;

22.图10是示出根据本发明构思的实施例的存储系统操作方法的图;

23.图11是示出根据本发明构思的实施例的存储系统的框图;

24.图12是示出根据本发明构思的实施例的存储系统操作方法的图;

25.图13是示出根据本发明构思的实施例的存储系统操作方法的图;

26.图14是示出根据本发明构思的实施例的存储系统的框图;

27.图15是示出根据本发明构思的实施例的存储设备操作方法的流程图;

28.图16是示出根据本发明构思的实施例的计算系统的框图;

29.图17是示出根据本发明构思的实施例的通用闪存(ufs)系统的图;

30.图18是示出根据本发明构思的实施例的ufs系统的图;并且

31.图19是示出根据本发明构思的实施例的计算系统的图。

具体实施方式

32.在整个书面描述和附图中,相同的附图标记和标签用于表示相同或相似的元件、组件、特征和/或方法步骤。

33.图1是示出根据本发明构思的实施例的存储系统1的框图。

34.参照图1,存储系统1通常可以包括主机100和存储设备200。

35.存储系统1可以是独立的计算系统,例如服务器、台式计算机、自助服务终端(kiosk)等。在一些实施例中,存储系统1可以是便携式计算系统、移动电话、可穿戴设备、笔记本电脑等。在一些实施例中,不同于独立计算系统或便携式计算系统,存储系统1可以是包括在任意系统中的子系统,例如家用电器、工业设备、交通工具或设备等。

36.主机100可以包括第一同态加密电路10。第一同态加密电路10可以用于使用同态加密算法将明文pt加密为同态密文ct和/或将同态密文ct解密为明文pt。在这种情况下,同态密文可以被理解为术语“密文”。由于同态加密方法的特点,在同态密文之间可以执行各种操作。即,从同态加密操作得到的解密数据可以与明文之间的操作结果一致(即,相同)。因为同态加密方法可以实现密文之间的操作,所以数据的安全性被增强了。

37.第一同态加密电路10可以用于将明文pt加密为0级密文ct或将0级密文ct解密为对应的明文pt。在这方面,“级别”可以表示对相应的同态密文执行的运算的最大数目。例如,“级别”可以被理解为关于密文ct执行的乘法运算的次数(或深度)。另外,在这方面,与本发明构思的实施例各种关联的不同(或多个)同态密文可以被生成为具有多个不同级别(例如,0级、1级、2级等)中的一个级别。例如,当密文ct的级别为1时,已经对密文ct执行了一次单个乘法运算。因此,对于1级密文ct,可以对密文ct执行一次乘法运算,并且乘法运算的结果可以被解密为明文pt。或者,对于0级密文ct,虽然可能已经对密文ct执行了乘法运算,但是乘法运算的结果可以无法被解密。

38.进一步地,密文ct的级别可以被理解为对应于密文ct的长度(或大小)。一般来说,密文ct的级别越高,密文ct的长度将越大。

39.第一同态加密电路10可以对密文ct执行自举运算(bootstrapping operation),并且可以对自举的密文ct执行乘法运算。第一同态加密电路10可以对自举的密文ct执行诸如加法运算和模运算的各种运算。自举运算可以增加密文ct的级别。因此,通过使用自举运算,密文ct的长度可以增加,并且可以对密文ct执行的乘法运算的数目可以增加。

40.主机100和存储设备200可以传递0级密文ct。0级密文ct可以是具有可以被正确地解密为明文pt的最小长度的同态密文。在图1的存储系统1中,主机100和存储设备200可以使用(一个或更多个)0级密文ct通信以使数据传输效率最大化。

41.存储设备200可以包括存储器控制器20和非易失性存储器(nvm)30。存储设备200可以包括被配置为响应于来自主机100的(一个或更多个)请求而存储数据的存储介质。在一些实施例中,存储设备200可以包括固态硬盘(ssd)、嵌入式存储器和可拆卸外部存储器中的至少一种。当存储设备200是ssd时,存储设备200可以遵循nvm快速(nvme)标准。当存储设备200为嵌入式存储器或外部存储器时,存储设备200可以遵循通用闪存(ufs)标准或嵌入式多媒体卡(emmc)标准。主机100和存储设备200中的每一者可以根据采用的标准协议来生成和传递数据包。

42.当nvm 30包括闪存时,闪存可以包括二维闪存(2d nand)存储阵列或三维(3d)(或垂直)nand(vnand)存储阵列。作为另一示例,存储设备200可以包括各种其他类型的nvm。例如,存储设备200可以包括磁性随机存取存储器(mram)、自旋转移矩mram、导电桥接ram(cbram)、铁电ram(feram)、相变ram(pram)、电阻ram(reram)、和各种其他类型的存储器。

43.存储器控制器20可以将0级密文ct存储在nvm 30中和/或从nvm 30读取0级密文ct。在根据本发明构思的实施例的存储设备200中,存储器控制器20将具有最小长度的0级密文ct存储在nvm 30中,从而可以提高存储速度。

44.nvm 30可以包括多个数据块。多个数据块中的每一个数据块可以存储0级密文ct。在一些实施例中,具有大于0的级别的密文ct可以不存储在所述多个数据块中。

45.存储器控制器20可以包括第二同态加密电路21。在一些实施例中,第二同态加密电路21可以对密文ct执行至少一个运算。这里,第二同态加密电路21可以对0级密文ct执行自举运算,也可以对自举的密文ct执行乘法运算。或者,第二同态加密电路21可以对自举的密文ct执行诸如加法运算和模运算的各种运算。

46.在一些实施例中,与第二同态加密电路21得到的运算结果相对应的密文ct的级别可以大于0。第二同态加密电路21可以将与运算结果相对应的密文ct的级别改变为0。即,第二同态加密电路21可以将密文ct的长度改变为密文ct可以被解密的最小长度。存储器控制器20将0级密文ct存储在nvm 30中以提高数据存储速度。因此,存储器控制器20可以向主机100提供0级密文ct,从而可以提高存储系统1的数据传输效率。

47.图2是示出根据本发明构思的实施例的同态加密电路40的框图。

48.参照图2,同态加密电路40可以包括编码器41、解码器42、加密器43、解密器44、自举电路45和模数切换(modulus switch)电路46。在一些实施例中,可以省略同态加密电路40的至少一个组件。这里,同态加密电路40可以是图1的第一同态加密电路10和/或第二同态加密电路21的一个示例。

49.编码器41可以生成与消息向量z相对应的明文多项式m(x)。消息向量z可以表示要被加密的输入数据。在当前说明书中,明文多项式m(x)可以被称为明文pt。

50.加密器43可以基于共享密钥pk和明文多项式m(x)生成密文ct。在一些实施例中,加密器43可以生成0级密文ct,并且因为0级密文ct具有允许密文ct被解密的最小长度,所以加密时间可以被减少。在这方面,图3是示出可以关于本发明构思的实施例使用的示例性加密方法的概念图。

51.参照图2,自举电路45可以基于0级密文ct生成具有k级(其中“k”是正整数)的密文ct。在这方面,可以对k级密文ct执行k个乘法运算。k级密文ct的长度可以大于0级密文ct的长度。即,执行自举运算要花费很长时间。在一些实施例中,自举电路45根据已经对自举密文执行了多少次乘法运算来自适应性地改变密文ct的级别,从而可以提高自举性能。在这方面,图4是示出可以关于本发明构思的实施例使用的示例性自举方法的概念图。

52.具有不同级别的同态密文中的至少一者可以是通过根据多个模数执行的模运算而生成的。例如,模数切换电路46可以通过改变密文的模数来控制密文的长度。即,模数切换电路46可以通过基于具有减小长度的模数对密文执行模运算来减小密文的长度。随着模运算的执行,密文的级别可以被降低。例如,模数切换电路46可以通过根据多个模数当中的最小模数执行模运算来生成0级的同态密文。模数切换运算可以称为重新调节(rescale)运算。在这方面,图5是示出可以关于本发明构思的实施例使用的示例性模数切换运算的概念图。

53.解密器44可以基于密钥sk和0级密文ct生成明文多项式m

′

(x)。下文将参照图3更详细地描述示例性的解密方法。

54.解码器42可以生成与明文多项式m

′

(x)相对应的向量消息z

′

。向量消息z

′

可以在有效位数(enob)上与向量消息z相同。

55.加密器43可以基于共享密钥pk和明文多项式m(x)生成密文ct。这里,共享密钥pk可以根据以下的[式1]进行表示:

[0056]

pk=(b

(j)

(x),a

(j)

(x))

0≤j≤l

,...[式1]

[0057]

其中,l表示密文的最大级别,并且b

(j)

(x)和a

(j)

(x)共享由以下的[式2]表示的关系:

[0058]b(j)

(x)=-a

(j)

(x)

·

s(x)+e(x),...[式2]

[0059]

其中,s(x)表示密钥多项式,e(x)表示误差多项式。

[0060]

这里,图2的加密器43可以根据以下的[式3]生成0级密文ct:

[0061]

ct=(v(x)

·

(b

(j)

(x),a

(j)

(x))+(m(x)+e0(x),e1(x)))(mod qj)

j=0

[0062]

=(v(x)

·b(j)

(x)+m(x)+e0(x),v(x)

·a(j)

(x)+e1(x))(mod qj)

j=0

=ct(0),...[式3]

[0063]

其中,v(x)表示系数为-1、0或1的多项式,e0(x)和e1(x)表示误差多项式,并且qj表示模数。

[0064]

即,根据[式3],当j=0时,加密器43可以基于共享密钥值生成0级密文ct。j=0时计算的值可以表示为第0子密文ct(0)。即,0级密文ct可以是第0子密文ct(0)。

[0065]

参照图3,当第0子密文ct(0)用位(bit)表示并且模数q0为2的平方时,第0子密文ct(0)的长度可以由模数q0确定。具体地,第0子密文ct(0)的长度可以是log2q0。

[0066]

从上文可以理解,根据本发明构思的某些实施例,在同态加密期间,通过将明文pt加密为0级密文ct,可以提高加密速度。

[0067]

参照图2和图4,自举电路45可以通过自举0级输入密文ct来生成l级输出密文ct

′

。即,自举电路45可以通过增加输入密文ct的级别来生成l级输出密文ct

′

。

[0068]

例如,图2的自举电路45可以被用于根据以下[式4]生成l级输出密文ct

′

:

[0069]

ct

′

=(v(x)

·

(b

(j)

(x),a

(j)

(x))+(m(x)+e0(x),e1(x)))(mod qj)

0≤j≤l

[0070]

=(v(x)

·b(j)

(x)+m(x)+e0(x),v(x)

·a(j)

(x)+e1(x))

0≤j≤l

,...[式4]

[0071]

其中,l表示自举级别。

[0072]

这里,应当另外注意的是,在一些实施例中,自举级别可以自适应地改变。在这方面,下面将参照图8描述自举级别改变的实施例。

[0073]

参照[式4],当(0≤j≤l)时,其中l是正整数,自举电路45可以基于共享密钥值生成l级输出密文ct

′

。另外,可以理解的是,l级输出密文ct

′

包括第0子输出密文ct

′

(0)至第l子输出密文ct

′

(l)。

[0074]

在自举期间,自举电路45可以执行与表示输入密文ct到明文槽(plaintext slot)的多项式的系数向量相对应的第一线性变换,可以对槽值(slot value)执行近似运算(approximate operation),并且可以执行将近似值与多项式的系数向量相对应的第二线性变换以生成输出密文ct

′

。由于同态加密的特性,自举电路45可以基于旋转密钥(rotation key)和共轭密钥(conjugation key)执行线性变换。

[0075]

参照图4,当第0子输出密文ct

′

(0)至第l子输出密文ct

′

(l)用位表示并且模数q0至ql为2的平方时,第0子输出密文ct

′

(0)至第l子输出密文ct

′

(l)的长度可以由模数q0至

ql确定。即,第0子输出密文ct

′

(0)至第l子输出密文ct

′

(l)的长度可以是log2q0至log2ql。

[0076]

图5是示出根据本发明构思的实施例的模数切换运算的概念图。

[0077]

参照图2和图5,模数切换电路46可以通过改变用于k级输入密文ct的模数来生成(k-1)级输出密文ct

′

,其中k是小于或等于l的正整数。

[0078]

k级输入密文ct可以包括第0子输入密文ct(0)至第k子输入密文ct(k)。第0子输入密文ct(0)至第k子输入密文ct(k)可以是基于第0模数q0至第k模数qk计算的模数值(modularvalue)。在图5中,输入密文ct的模数可以被理解为第0模数q0至第k模数qk的乘积。

[0079]

(k-1)级输出密文ct

′

可以包括第0子输出密文ct

′

(0)至第(k-1)子输出密文ct

′

(k-1)。第0子输出密文ct

′

(0)至第(k-1)子输出密文ct

′

(k-1)可以是基于第0模数q0至第k模数qk计算的模数值。在图5中,输出密文ct

′

的模数可以被理解为第0模数q0至第(k-1)模数q(k-1)的乘积。即,模数切换电路46可以通过将输入密文ct的模数降低qk来执行模数切换运算。在一些实施例中,第0模数q0至第k模数qk的长度可以彼此相等。因此,当执行模数切换运算时,可以离散地减小密文的长度。

[0080]

这里,输入密文ct可以由以下[式5]表示:

[0081]

ct=ct(j)

0≤j≤k

=(c0(j),c1(j)))

0≤j≤k

,...[式5]

[0082]

其中,根据[式3],c0(j)等于v(x)

·b(j)

(x)+m(x)+e0(x),v(x)

·a(j)

(x)+e1(x)并且c1(j)等于v(x)

·a(j)

(x)+e1(x)。

[0083]

因此,输出密文ct

′

可以由以下[式6]表示:

[0084]

ct

′

=(ct

′

(j)=(c

′0(j),c

′1(j))

0≤j≤k-1

,...[式6]

[0085]

其中,c

′

i(j)

(i=0或1)可以由以下[式7]表示:

[0086]c′

i(j)

=q

l-1

(c

i(j)-c

i(k)

)(mod qj)(i=0,1),...[式7]

[0087]

接着,参照图5和[式6],输出密文ct

′

的级别可以小于输入密文ct的级别。即,输出密文ct'的长度可以小于输入密文ct的长度。

[0088]

图6是示出根据本发明构思的实施例的乘法运算的概念图。

[0089]

参照图1、图2和图6,存储器控制器20可以基于具有k级的第一密文ct1和第二密文ct2通过执行乘法运算来生成第三密文ct3,其中k是正整数。如图6所示,第一密文ct1可以被表示为具有长度q1、第一明文m1和第一误差e1的位串的总和,第二密文ct2可以被表示为具有长度q1、第二明文m2和第二误差e2的位串的总和。

[0090]

第三密文ct3可以被表示为具有长度q1、第一明文和第二明文的乘积m1*m2和第三误差e3的位串的总和。第三误差e3的长度可以大于第一误差e1和第二误差e2中的每一者的长度。

[0091]

为了减小第三误差e3的长度,图2的模数切换电路46可以执行最低有效位(lsb)去除运算。lsb去除运算可以对应于图5的模数切换运算。即,模数切换电路46可以通过从第三密文ct3去除p个lsb来生成具有k-1级的第四密文ct4。在第一明文和第二明文的乘积m1*m2中,p个lsb可以具有低可靠性。因此,通过从第一明文和第二明文的乘积m1*m2去除p个lsb而获得的值(m1*m2)'可以是有效位。

[0092]

第四密文ct4可以被表示为具有长度q2、第一明文和第二明文的乘积m1*m2的有效位(m1*m2)'和第四误差e4的位串的总和。第四密文ct4的长度可以是q2,q2可以比q1小p。这

里,图5的模数ql可以对应于2的p次方。

[0093]

图7是示出根据本发明构思的实施例的存储系统2的框图。

[0094]

存储系统2通常可以包括主机300和存储设备200。主机300可以包括第一同态加密电路40,并且第一同态加密电路40可以包括自举电路45和模数切换电路46。

[0095]

主机300和存储设备200可以传递0级密文ct。主机300可以自举0级密文ct并且可以基于自举的密文执行运算。如图4所示,自举电路45可以将0级密文ct自举为l级密文ct'。主机300可以对l级密文ct'执行运算(例如,乘法运算)。如图5和图6所示,模数切换电路46可以通过对由运算生成的密文执行模数切换运算来降低密文的级别。

[0096]

图8是示出根据本发明构思的实施例的存储系统操作方法的流程图,并且图9是列出用于各种运算场景的变量的表格。

[0097]

参照图7、图8和图9,存储系统操作方法可以包括在主机300中根据基于运算场景确定的自举级别对密文执行自举运算(s810)。在这方面,运算场景可以表示对密文执行的一个或更多个运算。在一些实施例中,运算场景中包括的乘法运算的数目越大,可以对应的自举级别越高。

[0098]

这里,主机300可以存储运算场景表(snrt)(例如,将运算场景表存储在nvm中)。作为示出的示例,图9的运算场景表snrt包括第一运算场景、第二运算场景和第三运算场景(例如,snr1、snr2和snr3),然而运算场景的数目不限于此。

[0099]

在第一运算场景snrl中,可以首先执行多次(计数l)乘法运算,并且当在第一运算场景snrl中执行乘法运算时,密文的级别可以被降低sl1。当要对密文执行第一运算场景snr1时,自举电路45可以将密文的级别自举为l1。l1可以等于或大于sl1。

[0100]

在第二运算场景snr2中,可以其次执行多次(计数2)加法运算,并且当在第二运算场景snr2中执行加法运算时,密文的级别可以被降低sl2。当要对密文执行第二运算场景snr2时,自举电路45可以将密文的级别自举为l2。l2可以等于或大于sl2。

[0101]

在第三运算场景snr3中,可以再次执行多次(计数3)乘法和加法运算,并且当在第三运算场景snr3中执行乘法和加法运算时,密文的级别可以被降低sl3。当要对密文执行第三运算场景snr3时,自举电路45可以将密文的级别自举为l3。l3可以等于或大于sl3。

[0102]

然后,主机300可以根据运算场景对自举的密文执行至少一个运算(s820)。在一些实施例中,主机300可以执行将被执行了根据运算场景的所有运算的最终密文的级别改变为0的运算。或者,在一些实施例中,主机300可以从最终密文仅提取基于图3描述的第0密文ct(0)并且可以向存储设备200提供第0子密文ct(0)。

[0103]

图10是进一步示出根据本发明构思的实施例的存储系统操作方法的概念图。

[0104]

参照图7和图10,存储系统操作方法可以包括从存储设备200向主机300提供第一密文ctl(s1010)。这里,第一密文ct1可以是从nvm读取的0级同态密文。

[0105]

然后,主机300可以通过自举第一密文ctl来生成具有l级的第二密文ct2(s1020)。在一些实施例中,主机300可以根据运算场景(例如,图8和图9的运算场景)自适应地确定自举级别。

[0106]

然后,主机300可以通过对第二密文ct2执行至少一个运算来生成具有k级的第三密文ct3(s1030)。即,主机300可以对第三密文ct3执行至少一个预定运算。在一些实施例中,主机300可以根据运算场景(例如,图8和图9的运算场景)执行至少一个运算。这里,k可

以小于l,并且可以是0或正整数。在一些实施例中,当k级为0时,主机300可以通过向存储设备200提供第三密文ct3将第三密文ct3存储在存储设备200中。当k级为小于l的正整数时,可以执行操作s1040。

[0107]

然后,主机300可以通过重新调节第三密文ct3来生成具有0级的第四密文ct4(s1040)。在一些实施例中,主机300可以从第三密文ct3中提取第0子密文ct(0),并且可以使用所提取的第0子密文ct(0)作为第四密文ct4。

[0108]

然后,主机300可以将第四密文ct4存储在存储设备200中(s1050)。然而,因为第四密文ct4的级别是0,所以主机300可以将具有密文可以被解密的最小长度(或长度)的密文提供给存储设备200,从而可以增加密文传输速率。

[0109]

图11是示出根据本发明构思的实施例的存储系统3的框图。

[0110]

参照图11,存储系统3通常可以包括主机100和存储设备400,其中,存储设备400可以包括存储器控制器50和nvm 30。存储器控制器50可以包括第二同态加密电路51,并且第二同态加密电路51可以包括自举电路52和模数切换电路53。

[0111]

主机100和存储设备400可以传递密文ct。密文ct的级别可以变化。在一些实施例中,主机100和存储设备400可以传递0级密文ct,从而可以增加数据传输速率。

[0112]

在一些实施例中,存储器控制器50可以自举0级密文ct并且可以基于自举的密文ct执行运算。通过在乘法运算之后执行模数切换运算,可以降低密文的级别。在一些实施例中,存储器控制器50可以从与运算结果相对应的最终密文仅提取基于图3描述的第0子密文ct(0)并且可以向nvm 30或主机100提供第0子密文ct(0)。

[0113]

在一些实施例中,存储器控制器50可以将0级密文ct解密为明文pt。存储器控制器50可以对明文pt执行运算,并且将与运算结果相对应的明文pt'加密为0级同态密文ct'。存储器控制器50可以向主机100提供0级同态密文ct'。

[0114]

图12是进一步示出根据本发明构思的实施例的存储系统操作方法的概念图。

[0115]

参照图11和图12,在所示的存储系统操作方法中,存储器控制器50可以将第一密文ct1存储在nvm 30中(s1110)。第一密文ct1的级别可以是0。在一些实施例中,存储器控制器50可以从主机100接收第一密文ct1。在一些实施例中,存储器控制器50可以通过从主机100接收明文pt并且基于同态加密算法对明文pt进行加密来生成第一密文ct1。

[0116]

主机100可以从存储器控制器50请求第一密文ctl(s1120),并且存储器控制器50可以从nvm 30读取第一密文ctl(s1130)。这里,读取的第一密文ct1可以临时存储在易失性存储器(例如,与存储器控制器50相关联的动态随机存取存储器(dram))中。

[0117]

存储器控制器50可以通过自举第一密文ctl来生成具有l级(其中l是不小于2的整数)的第二密文ct2(s1140)。即,第一密文ct1可以对应于图4的输入密文ct并且第二密文ct2可以对应于图4的输出密文ct'。

[0118]

存储器控制器50可以向主机100提供第二密文ct2(s1150)。在一些实施例中,在操作s1150之后,主机100可以基于第二密文ct2执行至少一个运算。主机100可以通过对与至少一个运算结果相对应的密文进行解密来获得明文pt。

[0119]

图13是进一步示出根据本发明构思的实施例的存储系统操作方法的概念图。

[0120]

参照图10和图13,存储器控制器50可以将第一密文ct1存储在nvm30中(s1310)。此后,主机100可以向存储器控制器50发出请求以从nvm30检索第一密文ct1(s1320),其中,该

请求可以包括与将对第一密文ct1执行的运算有关的信息。例如,该请求可以包括例如图8的第一运算场景、第二运算场景和第三运算场景(snr1、snr2和snr3)的信息。响应于该请求,存储器控制器50可以从nvm 30检索(或读取)第一密文ct1(s1330)。

[0121]

然后,存储器控制器50可以通过自举第一密文ctl来生成l级的第二密文ct2(s1340),并且根据运算场景通过对第二密文ct2执行至少一个运算来生成第三密文ct3(s1350)。这里,第三密文ct3的级别可以低于第二密文ct2的级别。

[0122]

然后,存储器控制器50可以向主机100提供第三密文ct3(s1360),并且主机100可以通过对第三密文ct3进行解密来获得明文pt。

[0123]

图14是示出根据本发明构思的实施例的存储系统4的框图。

[0124]

参照图14,存储系统4通常可以包括主机500和存储设备600,然而,主机500被假设为不包括同态加密电路。存储设备600可以包括存储器控制器60和nvm 30。

[0125]

主机500和存储设备600可以传递明文pt。在一些实施例中,主机500和存储设备600可以传递消息向量z,即,上面参照图2描述的输入数据。

[0126]

存储器控制器60可以包括同态加密电路61和普通加密电路62。同态加密电路61可以是上面参照图2描述的同态加密电路40的实施例。普通加密电路62可以不基于同态加密算法而基于普通加密算法对明文pt进行加密。例如,普通加密算法可以是对称密钥算法或非对称密钥算法。普通加密算法可以提供比同态加密算法高的加密性能。普通加密算法可以包括高级加密标准(aes)算法、数据加密标准(des)算法、rivest-shamir-adleman(rsa)算法、消息摘要(md)算法或安全散列(sha)算法。

[0127]

存储器控制器60可以基于在明文pt被加密的状态下是否将被执行运算来基于同态加密算法或普通加密算法来对明文pt进行加密。

[0128]

因此,当在明文pt被加密的状态下将被执行运算时,同态加密电路61可以对明文pt进行加密。或者,当在明文pt被加密的状态下不被执行运算时,普通加密电路62可以对明文pt进行加密。

[0129]

图15是示出根据本发明构思的实施例的存储设备操作方法的流程图。

[0130]

参照图14和图15,存储设备600可以确定明文pt是否需要同态运算(s1510)。在一些实施例中,存储设备600可以从主机500接收表示明文pt是否需要同态运算的字段,并且可以识别相应的字段以确定明文pt是否需要同态运算。

[0131]

如果明文pt需要同态运算(s1510=是),则可以使用同态运算对明文pt进行加密(s1520)。即,存储设备600可以例如通过同态加密电路61使用所实现的同态加密算法对明文pt进行加密。以这种方式,同态加密电路61可以用于生成0级同态密文。

[0132]

然而,如果明文pt不需要同态运算(s1510=否),则存储设备600可以使用普通(即,非同态)加密算法对明文pt进行加密(s1530)。这里,使用普通加密算法可以导致比使用同态加密算法高的加密速度。

[0133]

然后,不管加密方法如何,存储设备600可以将密文存储在nvm 30中(s1540)。

[0134]

因此,根据本发明构思的某些实施例,因为可以根据与明文pt相关的同态运算的事先确定来选择性地使用同态加密算法或普通加密算法,所以可以获得优化的加密速度。

[0135]

图16是示出根据本发明构思的实施例的计算系统5的框图。

[0136]

参照图16,计算系统5通常可以包括移动设备700和服务器800。这里,假设移动设

备700是便携式计算系统,例如移动电话、可穿戴设备、笔记本电脑等。服务器800可以响应于移动设备700的请求将同态运算的结果提供给移动设备700。

[0137]

移动设备700可以包括第一散列电路710和第二散列电路750、第一密钥生成器720和第二密钥生成器760、同态加密电路730和存储设备740。

[0138]

第一散列电路710可以接收密码pw并且可以基于散列算法生成与密码pw相对应的摘要dig。不管密码pw的长度如何,摘要dig可以具有固定长度。

[0139]

第一秘钥生成器720可以基于摘要dig生成密钥sk。第一密钥生成器720可以向存储设备740提供密钥sk。

[0140]

存储设备740可以包括自举密钥生成器741、公钥生成器742和nvm 743。然而,本发明构思不限于此,并且存储设备740的一些组件可以设置在存储设备740外部。

[0141]

自举密钥生成器741可以基于密钥sk生成自举密钥bk。自举密钥bk可以包括旋转密钥和共轭密钥。公钥生成器742可以基于秘钥sk生成公钥pk。

[0142]

同态加密电路730可以包括加密器731和解密器732。加密器731可以接收第一明文pt1并且可以基于公钥pk生成第一密文ct1。例如,第一明文pt1可以包括移动设备700的用户的例如年龄、性别、血压的个人信息。第一密文ct1可以是0级同态密文。第一密文ct1可以被存储在nvm 743中。第一密文ct1可以被提供给服务器800用于同态运算。

[0143]

服务器800可以包括自举电路810、同态运算电路820和模数切换电路830。服务器800可以对第一密文ct1执行同态运算并且可以向移动设备700提供作为同态运算的结果而生成的第四密文ct4。

[0144]

自举电路810可以通过基于自举密钥bk自举第一密文ct1来生成第二密文ct2。第二密文ct2的级别可以大于0。

[0145]

同态运算电路820可以通过对第二密文ct2执行同态运算来生成第三密文ct3。同态运算可以包括乘法运算、加法运算、比较运算或模运算。例如,第三密文ct3可以表示基于用户的个人信息计算出的高血压概率。第三密文ct3的级别可以低于第二密文ct2的级别。当第三密文ct3的级别为0时,可以将第三密文ct3提供给移动设备700。当第三密文ct3的级别不为0时,模数切换电路830可以通过将第三密文ct3的级别变为0来生成第四密文ct4。可以将第四密文ct4提供给移动设备700。即,服务器800向移动设备700提供与0级相对应的同态密文,从而可以增加数据传输速率。

[0146]

第四密文ct4可以被存储在nvm 743中。为了提供与第四密文ct4相对应的第二明文pt2,移动设备700可以再次从用户接收密码pw。

[0147]

第二散列电路750可以基于散列算法生成与密码pw对应的摘要dig,并且第二密钥生成器760可以基于摘要dig生成秘钥sk。第一密钥生成器720和第二密钥生成器760可以生成相同的密钥sk。

[0148]

解密器732可以通过基于密钥sk对第四密文ct4进行解密来生成第二明文pt2,并且移动设备700可以输出第二明文pt2。

[0149]

图17是示出根据本发明构思的实施例的通用闪存(ufs)系统2000的框图。ufs系统2000可以是符合一个或更多个ufs标准的系统,如通过联合电子设备工程委员会(jedec)传统地理解和商业可获得的ufs标准。因此,ufs系统200包括ufs主机2100、ufs设备2200和ufs接口2300。这里,前面关于图1、图7、图11和图14描述的存储系统1、2、3和4中的任何一者或

更多者可以被应用于ufs系统2000。

[0150]

参照图17,ufs主机2100可以通过ufs接口2300连接到ufs设备2200。ufs主机2100可以被实现为ap的一部分。

[0151]

ufs主机2100可以包括ufs主机控制器2110、应用2120、ufs驱动器2130、主机存储器2140和ufs互连(uic)层2150。ufs设备2200可以包括ufs设备控制器2210、nvm 2220、存储接口(i/f)2230、设备存储器2240、uic层2250和调节器2260。nvm 2220可以包括多个存储单元。虽然每个存储单元可以包括具有2d结构或3d结构的v-nand闪存,每个存储单元可以包括另一种nvm,例如pram和/或rram。ufs设备控制器2210可以通过存储接口2230连接到nvm 2220。存储接口2230可以被配置为符合标准协议,例如触发(toggle)协议或开放式nand闪存接口(onfi)协议。

[0152]

应用2120可以指想要与ufs设备2200通信以使用ufs设备2200的功能的程序。应用2120可以向ufs驱动器2130传送输入-输出请求(ior),用于对ufs设备2200执行输入/输出(i/o)运算。ior可以指数据读取请求、数据存储(或写入)请求、和/或数据擦除(或丢弃)请求,但不限于此。

[0153]

ufs驱动器2130可以通过ufs-主机控制器接口(ufs-hci)来管理ufs主机控制器2110。ufs驱动器2130可以将应用2120生成的ior转换成ufs标准定义的ufs命令,并将ufs命令传递给ufs主机控制器2110。一个ior可以转换成多个ufs命令。虽然ufs命令基本上可以由scsi标准定义,但ufs命令可以是专用于ufs标准的命令。

[0154]

ufs主机控制器2110可以通过uic层2150和ufs接口2300将由ufs驱动器2130转换的ufs命令传递到ufs设备2200的uic层2250。在传输ufs命令期间,ufs主机控制器2110的ufs主机寄存器2111可以用作命令队列(cq)。

[0155]

ufs主机2100侧的uic层2150可以包括移动工业处理器接口(mipi)m-phy 2151和mipi uni-pro 2152,并且ufs设备2200侧的uic层2250也可以包括mipi m-phy 2251和mipi uni-pro 2252。

[0156]

ufs接口2300可以包括被配置为传递参考时钟信号ref_clk的线、被配置为传递用于ufs设备2200的硬件复位信号reset_n的线、被配置为传递成对的差分输入信号din_t和din_c的成对的线、以及被配置为传递成对的差分输出信号dout_t和dout_c的成对的线。

[0157]

从ufs主机2100提供给ufs设备2200的参考时钟信号ref_clk的频率可以是19.2mhz、26mhz、38.4mhz和52mhz中的一者,但不限于此。在运算期间,即在ufs主机2100和ufs设备2200之间的数据发送/接收运算期间,ufs主机2100可以改变参考时钟信号ref_clk的频率。ufs设备2200可以通过使用锁相环(pll)从由ufs主机2100提供的参考时钟信号ref_clk生成具有各种频率的时钟信号。此外,ufs主机2100可以通过使用参考时钟信号ref_clk的频率来设置ufs主机2100和ufs设备2200之间的数据速率。即,可以根据参考时钟信号ref_clk的频率来确定数据速率。

[0158]

ufs接口2300可以支持多个通道(lane),每个通道可以被实现为成对的差分线。例如,ufs接口2300可以包括至少一个接收通道和至少一个传输通道。在图17中,被配置为传递成对的差分输入信号din_t和din_c的成对的线可以构成接收通道,并且被配置为传递成对的差分输出信号dout_t和dout_c的成对的线可以构成发送通道。尽管在图17中示出了一个发送通道和一个接收通道,但是发送通道的数目和接收通道的数目可以改变。

[0159]

接收通道和发送通道可以基于串行通信方案来传递数据。由于接收通道与发送通道分离的结构,所以可以启用ufs主机2100和ufs设备2200之间的全双工通信。即,在通过接收通道从ufs主机2100接收数据的同时,ufs设备2200可以通过发送通道将数据传递到ufs主机2100。另外,从ufs主机2100到ufs设备2200的控制数据(例如,命令)和将被由ufs主机2100存储在ufs设备2200的nvm 2220中的用户数据或将由ufs主机2100从ufs设备2200的nvm 2220读取的用户数据可以通过相同的通道进行传递。因此,在ufs主机2100和ufs设备2200之间,除了成对的接收通道和成对的发送通道之外,可以不需要进一步提供单独的通道用于数据传输。

[0160]

ufs设备2200的ufs设备控制器2210可以控制ufs设备2200的所有运算。ufs设备控制器2210可以通过使用作为逻辑数据存储单元的逻辑单元(lu)2211来管理nvm 2220。lu 2211的数目可以是8个,但不限于此。ufs设备控制器2210可以包括ftl,并且可以通过使用ftl的地址映射信息将从ufs主机2100接收的逻辑数据地址(例如,逻辑块地址(lba))转换成物理数据地址(例如,物理块地址(pba))。被配置为在ufs系统2000中存储用户数据的逻辑块可以具有预定范围内的长度。例如,逻辑块的最小长度可以被设置为4kbyte。

[0161]

当来自ufs主机2100的命令通过uic层2250施加到ufs设备2200时,ufs设备控制器2210可以响应于该命令执行运算并且当运算完成时将完成响应传递给ufs主机2100。

[0162]

作为示例,当ufs主机2100打算将用户数据存储在ufs设备2200中时,ufs主机2100可以向ufs设备2200传递数据存储命令。当从ufs设备2200接收到指示ufs主机2100准备好接收用户数据(准备好传输)的响应(“准备好传输”响应)时,ufs主机2100可以将用户数据传递到ufs设备2200。ufs设备控制器2210可以将接收到的用户数据临时存储在设备存储器2240中,并且基于ftl的地址映射信息将临时存储在设备存储器2240中的用户数据存储在nvm 2220中的选定位置。

[0163]

作为另一示例,当ufs主机2100打算读取存储在ufs设备2200中的用户数据时,ufs主机2100可以向ufs设备2200传递数据读取命令。已经接收到该命令的ufs设备控制器2210可以基于数据读取命令从nvm 2220读取用户数据,并且将读取的用户数据临时存储在设备存储器2240中。在读取运算期间,ufs设备控制器2210可以通过使用嵌入在其中的纠错码(ecc)引擎(未显示)检测并纠正读取的用户数据中的错误。另外,ufs设备控制器2210可以将临时存储在设备存储器2240中的用户数据传递到ufs主机2100。另外,ufs设备控制器2210还可以包括aes引擎(未示出)。aes引擎可以通过使用对称密钥算法对传递到ufs设备控制器2210的数据执行加密运算和解密运算中的至少一者。

[0164]

根据本发明构思的实施例的ufs设备控制器2210可以包括同态加密(he)电路2212。同态加密电路2212可以生成0级同态密文。同态加密电路2212可以将通过成对的差分输入信号din_t和din_c接收到的明文加密为0级同态密文。0级同态密文可以通过存储接口2230存储在nvm 2220中。同态加密电路2212可以通过自举0级同态密文来生成具有l级(l是大于0的整数)的同态密文,并且可以对l级同态密文执行同态运算。ufs设备2200可以通过成对的差分输出信号对dout_t和dout_c向ufs主机2100提供0级同态密文。

[0165]

ufs主机2100可以把将传递给ufs设备2200的命令顺序地存储在可以用作公共队列的ufs主机寄存器2111中,并且顺序地将该命令传递给ufs设备2200。在这种情况下,即使ufs设备2200仍在处理先前传递的命令,即,即使在接收到ufs设备2200已经处理了先前传

递的命令的通知之前,ufs主机2100也可以向ufs设备2200传递在cq中处于等待状态的下一个命令。因此,ufs设备2200也可以在处理先前传递的命令期间从ufs主机2100接收下一个命令。可以存储在cq中的命令的最大数目(或队列深度)可以是例如32。另外,cq可以被实现为在队列中存储的命令行的开始和结束分别由头指针和尾指针指示的循环队列。

[0166]

多个存储单元中的每一者可以包括存储单元阵列(未示出)和被配置为控制存储单元阵列的运算的控制电路(未示出)。存储单元阵列可以包括2d存储单元阵列或3d存储单元阵列。存储单元阵列可以包括多个存储单元。虽然每个存储单元是被配置为存储1位信息的单级单元(single-level cell,slc),但是每个存储单元可以是被配置为存储2位或更多位信息的单元,例如多级单元(multi-level cell,mlc)、三级单元(triple-level cell,tlc)和四级单元(quadruple-level cell,qlc)。3d存储单元阵列可以包括至少一个存储单元被垂直定向并且位于另一存储单元上的垂直nand串。

[0167]

电压vcc、vccq和vccq2可以作为电源电压施加到ufs设备2200。电压vcc可以是ufs设备2200的主电源电压,并且为2.4v到3.6v。电压vccq可以是用于主要向ufs设备控制器2210提供低电压的电源电压,并且为1.14v至1.26v。电压vccq2可以是用于主要向诸如mipi m-phy 2251的i/o接口提供低于电压vcc和高于电压vccq的电压的电源电压,并且为1.7v至1.95v。电源电压可以通过调节器2260提供给ufs设备2200的各个组件。调节器2260可以被实现为分别连接到上述不同电源电压的一组单元调节器。

[0168]

图18是示出根据本发明构思的实施例的ufs系统3000的框图。

[0169]

这里,ufs系统3000的ufs主机3100可以包括ufs主机控制器3110。ufs主机控制器3110可以包括同态加密(he)电路3212。同态加密电路3212可以将从ufs驱动器2130接收的明文加密为0级同态密文。ufs主机3100可以通过成对的差分输入信号din_t和din_c向ufs存储器3200提供0级同态密文。

[0170]

同态加密电路3212可以通过自举0级同态密文来生成具有l级(l是大于0的整数)的同态密文,并且可以对l级同态密文执行同态运算。在一些实施例中,如图17所示,ufs设备控制器2210可以包括同态加密电路2212。

[0171]

图19是示出根据本发明构思的实施例的计算系统4000的框图。

[0172]

参照图19,计算系统4000可以包括主机4100、存储控制器4210和nvm4220。存储控制器4210和nvm 4220可以被包括在存储设备中。

[0173]

主机4100可以包括数字信号处理器(dsp)4110、神经处理单元(npu)4120、接口电路(if)4130、第一同态加密(he)电路4140、通信模块4150和图形处理单元(gpu)/中央处理单元(cpu)4160。

[0174]

数字信号处理器4110可以对通过转换模拟信号获得的数字信号执行运算。神经处理单元4120可以基于人工神经网络执行机器学习和推理。

[0175]

接口电路4130可以向存储控制器4210提供数据和从存储控制器4210接收数据。在一些实施例中,接口电路4130可以传递/接收0级同态密文。

[0176]

第一同态加密电路4140可以将明文加密为0级同态密文。在一些实施例中,第一同态加密电路4140可以自举0级同态密文并且可以基于自举的密文执行同态运算。在一些实施例中,用于自举的自举密钥可以通过接口电路4130从存储控制器4210传递到主机4100。

[0177]

通信模块4150可以包括3g、4g、长期演进(lte)、5g或无线通信模块。gpu/cpu 4160

可以包括至少一个处理指令的核并且可以控制主机4100的整体操作。

[0178]

存储控制器4210可以包括接口电路4211、cpu 4212、静态ram(sram)4213、第二同态加密电路4214和nand接口电路(nand if)4215,并且nand接口电路4215可以将数据传递到nvm 4220或传递来自nvm 4220的数据。

[0179]

接口电路4211可以接收来自主机4100的请求,可以执行对应于该请求的运算,并且可以将响应传递给主机4100。接口电路4211和cpu 4212可以包括至少一个处理指令的核并且可以控制存储控制器4210的整体操作。sram 4213可以临时存储由cpu 4212处理的数据。

[0180]

第二同态加密电路4214可以将明文加密为0级同态密文。在一些实施例中,第二同态加密电路4214可以自举0级同态密文并且可以基于自举的密文执行同态运算。在一些实施例中,由第二同态加密电路4214产生的0级同态密文可以通过nand接口电路4215存储在nvm 4220中。

[0181]

虽然本发明构思已经参照其实施例进行了具体的示出和描述,但是将理解的是,在不脱离所附权利要求的精神和范围的情况下,可以对本文进行形式和细节上的各种改变。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1