一种基于FPGA电子变倍前置DDR的相机系统的制作方法

一种基于fpga电子变倍前置ddr的相机系统

技术领域

1.本发明属于图像视频处理领域,尤其指一种基于fpga电子变倍前置ddr的相机系统。

背景技术:

2.目前fpga高速视频处理系统中的电子变倍技术,已经广泛应用于单兵领域,方便相机系统放大或锁定目标。传统的基于fpga的电子变倍是在ddr存储器之后进行电子变倍处理,在单兵系统的应用中由于某些特殊场景的需求,在传统高清高帧率的基础上要求输出视频图像的一致性,即输出视频图像的时钟、帧率、行频、分辨率一致,然而传统的基于fpga在ddr存储器之后的电子变倍处理,难以满足如此苛刻的要求。

技术实现要素:

3.为解决上述技术问题,本发明的目的是提供一种基于fpga电子变倍前置ddr的相机系统,在电子变倍后可以输出一致时钟、帧率、行频、分辨率的高清高帧率的视频图像。

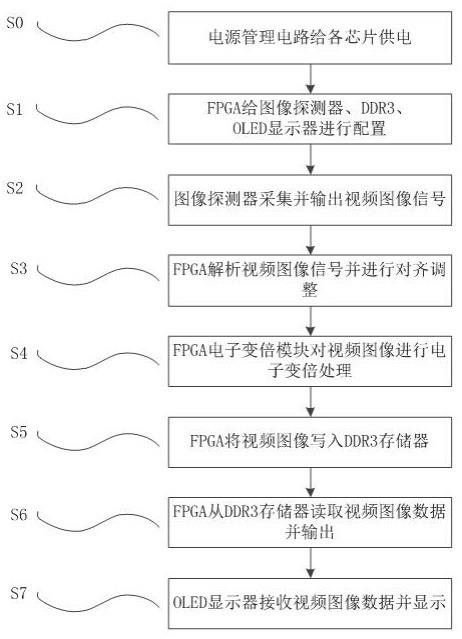

4.为实现上述目的,本发明采用的技术方案是:一种基于fpga电子变倍前置ddr的相机系统,包括fpga处理芯片、图像探测器、ddr3存储器、电源管理电路、oled显示器、按键控制电路,其特征在于,所述相机系统的电子变倍前置ddr处理,通过如下步骤实现:s0,电源管理电路给各芯片提供电源;s1,fpga处理芯片给图像探测器、ddr3存储器、oled显示组件进行配置;s2,图像探测器采集视频图像数据,将其转换为视频图像信号并输出至fpga处理芯片;s3,fpga处理芯片接收视频图像信号并进行解析和对齐调整;s4,fpga处理芯片中的电子变倍模块,根据按键控制电路选择的变倍倍数,对视频图像进行电子变倍处理;s5,fpga处理芯片将进行电子变倍处理后的视频图像写入ddr3存储器;s6,fpga处理芯片按照oled显示器显示的格式读取ddr3存储器的视频数据,并通过i/o引脚输出给oled显示器;s7,oled显示器接收视频图像数据并进行显示。

5.进一步地,所述电源管理电路由多片电源转换芯片及相应的外围电路组成,为fpga处理芯片、ddr3存储器、图像探测器、oled显示器提供电源。

6.进一步地,所述图像探测器连接在fpga处理芯片的i/o引脚上,fpga处理芯片为图像探测器提供的配置信息通过i/o口传输给图像探测器,并驱动图像探测器正常工作;图像探测器采集原始视频图像信息通过i/o口传输给fpga处理芯片,完成视频图像采集功能。

7.进一步地,所述ddr3存储器连接fpga处理芯片的内存控制器接口,作为系统的外挂大容量存储器。

8.进一步地,所述oled显示器连接在fpga处理芯片的i/o引脚上,通过引脚映射方式

驱动oled显示器显示成像,作为人机交互的显示界面。

9.进一步地,所述按键控制电路连接在fpga处理芯片的i/o引脚上,用户可通过按键控制电子变倍的倍率。

10.进一步地,s3步骤中所述的fpga处理芯片接收视频图像信号并进行解析和对齐调整,是将视频图像数据调整为分辨率为1920

×

1080、24bitycbcr数据输入值电子变倍模块,时钟为148.5mhz,帧率为60帧。

11.进一步地,s4步骤中所述的fpga处理芯片中的电子变倍模块根据按键控制电路选择的变倍倍数,对视频图像进行电子变倍处理,通过如下步骤实现:1、判断当前按键控制模块设定的电子变倍倍率是否为1,若为1将数据输入到24bitycbcr数据转换16bitycbcr数据模块;若电子变倍倍率不为1,则在所需区域开窗,开窗大小为960

×

540;2、通过使用fifo将处理视频图像数据的时钟切换到原时钟1/2的时钟上进行数据处理,通过使用3条fifo视频图像数据进行4

×

4滑窗处理;3、采用加权插值法对视频图像数据进行2倍电子变倍,此时数据量是一个时钟出4个数据,总数据量是960

×

540

×

4;由于第1通道和第2通道是插值后同一行数据,第3通道和第4通道也是同一行数据,所以总数据量为960

×2×

540

×

2;4、通过使用fifo将处理视频图像数据的1/2、3/4通道进行合并,处理的时钟从原时钟的1/2切换回原时钟,此时数据总量为1920

×

540

×

2,即每一行1920个双通道数据共540行;5、判断电子变倍的倍数是否为2,若为2将数据输入到24bitycbcr数据转换16bitycbcr数据模块;若电子变倍倍数不为2,则进行区域开窗处理,此时数据总量为960

×

270

×

2;6、将数据从双通道变成一通道,同时进行展行处理,此时数据总量为960

×

540,即每行960个数据,共540行;7、通过使用3条fifo视频图像数据进行4

×

4滑窗处理;8、采用加权插值法对视频图像数据进行2倍电子变倍,总数据量为960

×2×

540

×

2;9、将数据输入到24bitycbcr数据转换16bitycbcr数据模块,24bitycbcr数据转换16bitycbcr数据模块将24bitycbcr数据转换成16bitycbcr数据;10、判断电子变倍的倍数,若为1则每8个时钟组成一个数据组,奇数行数据放fifo1,偶数行数据放fifo2;若为2则每8个时钟组成一个数据组,通道1数据放fifo1,通道2数据放fifo2电子变倍的倍数,若为4则每4个时钟组成一个数据组,通道1通道2数据放fifo1,通道3通道4数据放fifo2。

12.进一步地,s5步骤中所述fpga处理芯片是将进行电子变倍处理后的视频图像中fifo1和fifo2的数据写入ddr3存储器。

13.与现有技术相比,本发明技术相对于传统在读取ddr3存储器之后做电子变倍的技术,具有以下优势:本发明基于fpga电子变倍前置ddr的相机系统,读取ddr3并输出视频图像的时序是一致的,满足相机系统特殊条件下对视频图像时序一致性的要求。

附图说明

14.图1为本发明一种基于fpga电子变倍前置ddr的相机系统框图;图2为本发明一种基于fpga电子变倍前置ddr的相机系统工作流程图;图3为本发明一种基于fpga电子变倍前置ddr的相机系统前置ddr电子变倍实现的具体流程图。

具体实施方式

15.下面结合附图和实施例,对本发明的技术方案作以下具体详细的描述。

16.如图1所示,本发明的一种基于fpga电子变倍前置ddr的相机系统,包括fpga处理芯片、图像探测器、ddr3存储器、电源管理电路、oled显示器、按键控制电路。

17.电源管理电路由多片电源转换芯片及相应的外围电路组成,为fpga处理芯片、ddr3存储器、图像探测器、oled显示器提供电源。

18.fpga是核心处理芯片,选用xilinx的a7系列xc7a50tcsg325-2芯片;fpga处理芯片负责解析视频输入、进行电子变倍、ddr3读写、输出视频数据等功能模块的实现。

19.图像探测器选用索尼的imx392彩色探测器,图像探测器连接在fpga处理芯片的i/o引脚上,是视频图像采集传感器,也是系统的视频输入来源;fpga处理芯片为图像探测器提供的配置信息通过i/o口传输给图像探测器,并驱动图像探测器正常工作;图像探测器采集原始视频图像信息通过i/o口传输给fpga处理芯片,完成视频图像采集功能。

20.ddr3是存储芯片,ddr3存储器采用镁光的mt41k128m16ha-125;ddr3存储器连接fpga处理芯片的内存控制器接口,作为系统的外挂大容量存储器负责视频数据的存储。

21.oled显示器是显示组件,oled显示器选用湖畔光电的硅基oled微显示器ls1080p071fc ;oled显示器连接在fpga处理芯片的i/o引脚上,通过引脚映射方式驱动oled显示器显示成像,实现人机交互的显示界面。

22.按键控制电路选择2

×

2矩阵排列的点触式矩阵,并分别连接在fpga处理芯片的4个i/o引脚上,用户可通过按键控制电子变倍的倍率。

23.如图2所示,本发明的一种基于fpga电子变倍前置ddr的相机系统的工作流程步骤如下:s0,电源管理电路给各芯片提供电源;s1,fpga处理芯片给图像探测器、ddr3存储器、oled显示组件进行配置;s2,图像探测器采集视频图像数据,将其转换为视频图像信号并输出至fpga处理芯片;s3,fpga处理芯片接收视频图像信号并进行解析和对齐调整;s4,fpga处理芯片中的电子变倍模块,根据按键控制电路选择的变倍倍数,对视频图像进行电子变倍处理;s5,fpga处理芯片将进行电子变倍处理后的视频图像写入ddr3存储器;s6,fpga处理芯片按照oled显示器显示的格式读取ddr3存储器的视频数据,并通过i/o引脚输出给oled显示器;s7,oled显示器接收视频图像数据并进行显示。

24.如图3所示,本发明的一种基于fpga电子变倍前置ddr的相机系统的电子变倍前置

处理流程如下:视频数据经前端模块调整为分辨率为1920

×

1080、24bitycbcr数据输入值电子变倍模块,时钟为148.5mhz,帧率为60帧;判断当前按键控制模块设定的电子变倍倍率是否为1,若为1将数据输入到24bitycbcr数据转换16bitycbcr数据模块;若电子变倍倍率不为1,则在所需区域开窗,开窗大小为960

×

540;通过使用fifo将处理视频图像数据的时钟切换到原时钟1/2的时钟上进行数据处理;通过使用3条fifo视频图像数据进行4

×

4滑窗处理,输出的数据接口代码如下:module mix_4x4(input

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

clk_pix

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

,

ꢀꢀꢀꢀ

input

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

rst_n

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

,

ꢀꢀꢀꢀ

input

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

fvld_in

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

,

ꢀꢀꢀꢀ

input

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

lvld_in

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

,

ꢀꢀꢀꢀ

input

ꢀꢀꢀꢀꢀꢀꢀꢀ

[23:0]

ꢀꢀꢀꢀꢀꢀ

data_in

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

,

ꢀꢀꢀꢀ

input

ꢀꢀꢀꢀꢀꢀꢀꢀ

[1 :0]

ꢀꢀꢀꢀꢀꢀ

model

ꢀꢀꢀꢀꢀ

,//00-》x1 01-》x2 10-》x4

ꢀꢀꢀꢀ

output reg

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

fvld_o

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

,

ꢀꢀꢀꢀ

output reg

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

lvld_o

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

,

ꢀꢀꢀꢀ

output reg

ꢀꢀꢀ

[23:0]

ꢀꢀꢀꢀꢀꢀ

data_o_11

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

,

ꢀꢀꢀꢀ

output reg

ꢀꢀꢀ

[23:0]

ꢀꢀꢀꢀꢀꢀ

data_o_12

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

,

ꢀꢀꢀꢀ

output reg

ꢀꢀꢀ

[23:0]

ꢀꢀꢀꢀꢀꢀ

data_o_13

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

,

ꢀꢀꢀꢀ

output reg

ꢀꢀꢀ

[23:0]

ꢀꢀꢀꢀꢀꢀ

data_o_14

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

,

ꢀꢀꢀꢀ

output reg

ꢀꢀꢀ

[23:0]

ꢀꢀꢀꢀꢀꢀ

data_o_21

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

,

ꢀꢀꢀꢀ

output reg

ꢀꢀꢀ

[23:0]

ꢀꢀꢀꢀꢀꢀ

data_o_22

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

,

ꢀꢀꢀꢀ

output reg

ꢀꢀꢀ

[23:0]

ꢀꢀꢀꢀꢀꢀ

data_o_23

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

,

ꢀꢀꢀꢀ

output reg

ꢀꢀꢀ

[23:0]

ꢀꢀꢀꢀꢀꢀ

data_o_24

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

,

ꢀꢀꢀꢀ

output reg

ꢀꢀꢀ

[23:0]

ꢀꢀꢀꢀꢀ

data_o_31

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

,

ꢀꢀꢀꢀ

output reg

ꢀꢀꢀ

[23:0]

ꢀꢀꢀꢀꢀ

data_o_32

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

,

ꢀꢀꢀꢀ

output reg

ꢀꢀꢀ

[23:0]

ꢀꢀꢀꢀꢀ

data_o_33

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

,

ꢀꢀꢀꢀ

output reg

ꢀꢀꢀ

[23:0]

ꢀꢀꢀꢀꢀ

data_o_34

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

,

ꢀꢀꢀꢀ

output reg

ꢀꢀꢀ

[23:0]

ꢀꢀꢀꢀꢀ

data_o_41

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

,

ꢀꢀꢀꢀ

output reg

ꢀꢀꢀ

[23:0]

ꢀꢀꢀꢀꢀ

data_o_42

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

,

ꢀꢀꢀꢀ

output reg

ꢀꢀꢀ

[23:0]

ꢀꢀꢀꢀꢀ

data_o_43

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

,

ꢀꢀꢀꢀ

output reg

ꢀꢀꢀ

[23:0]

ꢀꢀꢀꢀꢀ

data_o_44

ꢀꢀꢀ

);采用加权插值法对视频图像数据进行2倍电子变倍,此时数据量是一个时钟出4个数据,总数据量是960

×

540

×

4;由于第1通道和第2通道是插值后同一行数据,第3通道和第4通道也是同一行数据,所以总数据量为960

×2×

540

×

2,输出的数据接口代码如下:module zoom_x2(

input

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

clk_pix

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

,

ꢀꢀꢀꢀ

input

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

rst_n

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

,

ꢀꢀꢀꢀ

input

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

fvld_in

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

,

ꢀꢀꢀꢀ

input

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

lvld_in

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

,

ꢀꢀꢀꢀ

input

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

[23:0]

ꢀꢀꢀꢀꢀꢀ

data_in_11

ꢀꢀꢀꢀꢀꢀꢀꢀ

,

ꢀꢀꢀꢀ

input

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

[23:0]

ꢀꢀꢀꢀꢀꢀ

data_in_12

ꢀꢀꢀꢀꢀꢀꢀꢀ

,

ꢀꢀꢀꢀ

input

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

[23:0]

ꢀꢀꢀꢀꢀꢀ

data_in_13

ꢀꢀꢀꢀꢀꢀꢀꢀ

,

ꢀꢀꢀꢀ

input

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

[23:0]

ꢀꢀꢀꢀꢀꢀ

data_in_14

ꢀꢀꢀꢀꢀꢀꢀꢀ

,

ꢀꢀꢀꢀ

input

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

[23:0]

ꢀꢀꢀꢀꢀꢀ

data_in_21

ꢀꢀꢀꢀꢀꢀꢀꢀ

,

ꢀꢀꢀꢀꢀ

input

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

[23:0]

ꢀꢀꢀꢀꢀꢀ

data_in_22

ꢀꢀꢀꢀꢀꢀꢀꢀ

,

ꢀꢀꢀꢀ

input

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

[23:0]

ꢀꢀꢀꢀꢀꢀ

data_in_23

ꢀꢀꢀꢀꢀꢀꢀꢀ

,

ꢀꢀꢀꢀ

input

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

[23:0]

ꢀꢀꢀꢀꢀꢀ

data_in_24

ꢀꢀꢀꢀꢀꢀꢀꢀ

,

ꢀꢀꢀꢀ

input

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

[23:0]

ꢀꢀꢀꢀꢀꢀ

data_in_31

ꢀꢀꢀꢀꢀꢀꢀꢀ

,

ꢀꢀꢀꢀ

input

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

[23:0]

ꢀꢀꢀꢀꢀꢀ

data_in_32

ꢀꢀꢀꢀꢀꢀꢀꢀ

,

ꢀꢀꢀꢀ

input

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

[23:0]

ꢀꢀꢀꢀꢀꢀ

data_in_33

ꢀꢀꢀꢀꢀꢀꢀꢀ

,

ꢀꢀꢀꢀ

input

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

[23:0]

ꢀꢀꢀꢀꢀꢀ

data_in_34

ꢀꢀꢀꢀꢀꢀꢀꢀ

,

ꢀꢀꢀꢀ

input

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

[23:0]

ꢀꢀꢀꢀꢀꢀ

data_in_41

ꢀꢀꢀꢀꢀꢀꢀꢀ

,

ꢀꢀꢀꢀ

input

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

[23:0]

ꢀꢀꢀꢀꢀꢀ

data_in_42

ꢀꢀꢀꢀꢀꢀꢀꢀ

,

ꢀꢀꢀꢀ

input

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

[23:0]

ꢀꢀꢀꢀꢀꢀ

data_in_43

ꢀꢀꢀꢀꢀꢀꢀꢀ

,

ꢀꢀꢀꢀ

input

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

[23:0]

ꢀꢀꢀꢀꢀꢀ

data_in_44

ꢀꢀꢀꢀꢀꢀꢀꢀ

,

ꢀꢀꢀꢀ

output reg

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

fvld_o

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

,

ꢀꢀꢀꢀ

output reg

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

lvld_o

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

,

ꢀꢀꢀꢀ

output reg

ꢀꢀꢀꢀ

[23:0]

ꢀꢀꢀꢀꢀꢀ

data_o_11

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

,

ꢀꢀꢀꢀ

output reg

ꢀꢀꢀꢀ

[23:0]

ꢀꢀꢀꢀꢀꢀ

data_o_12

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

,

ꢀꢀꢀꢀ

output reg

ꢀꢀꢀꢀ

[23:0]

ꢀꢀꢀꢀꢀꢀ

data_o_21

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

,

ꢀꢀꢀꢀ

output reg

ꢀꢀꢀꢀ

[23:0]

ꢀꢀꢀꢀꢀꢀ

data_o_22);通过使用fifo将处理视频图像数据的1/2、3/4通道进行合并,处理的时钟从原时钟的1/2切换回原时钟,此时数据总量为1920

×

540

×

2,即每一行1920个双通道数据共540行;判断电子变倍的倍数是否为2,若为2将数据输入到24bitycbcr数据转换16bitycbcr数据模块;若电子变倍倍数不为2,则进行区域开窗处理,此时数据总量为960

×

270

×

2;将数据从双通道变成一通道,同时进行展行处理,此时数据总量为960

×

540,即每行960个数据,共540行;通过使用3条fifo视频图像数据进行4

×

4滑窗处理,这里代码同2倍电子变倍;采用加权插值法对视频图像数据进行2倍电子变倍,这里代码同2倍电子变倍,总数据量为960

×2×

540

×

2;将数据输入到24bitycbcr数据转换16bitycbcr数据模块,24bitycbcr数据转换

16bitycbcr数据模块将24bitycbcr数据转换成16bitycbcr数据;判断电子变倍的倍数,若为1则每8个时钟组成一个数据组,奇数行数据放fifo1,偶数行数据放fifo2;若为2则每8个时钟组成一个数据组,通道1数据放fifo1,通道2数据放fifo2电子变倍的倍数,若为4则每4个时钟组成一个数据组,通道1通道2数据放fifo1,通道3通道4数据放fifo2,输出的数据代码如下:always@(posedge pix_clk) begin

ꢀꢀꢀꢀꢀꢀ

if(r_data_cnt==7&&model==model_x1&&odd_st==1) begin

ꢀꢀꢀꢀꢀ

r_wr_fifo_data_1

ꢀꢀꢀꢀ

《=

ꢀꢀꢀꢀꢀꢀꢀ

{r_data_d_11[0],r_data_d_11[1],r_data_d_11[2],r_data_d_11[3],r_data_d_11[4],r_data_d_11[5],r_data_d_11[6],r_data_d_11[7]}

ꢀꢀꢀ

;end else if(r_data_cnt==7&&model==model_x2) begin

ꢀꢀꢀꢀꢀꢀꢀꢀ

r_wr_fifo_data_1

ꢀꢀꢀꢀꢀꢀ

《=

ꢀꢀꢀꢀꢀꢀꢀ

{r_data_d_11[0],r_data_d_11[1],r_data_d_11[2],r_data_d_11[3],r_data_d_11[4],r_data_d_11[5],r_data_d_11[6],r_data_d_11[7]}

ꢀꢀꢀ

;

ꢀꢀꢀꢀ

end else if(r_data_cnt%4==3&&model==model_x4) begin

ꢀꢀꢀꢀꢀꢀꢀꢀ

r_wr_fifo_data_1

ꢀꢀꢀꢀꢀꢀ

《=

ꢀꢀꢀꢀꢀꢀꢀ

{r_data_d_12[0],r_data_d_11[0],r_data_d_12[1],r_data_d_11[1],r_data_d_12[2],r_data_d_11[2],r_data_d_12[3],r_data_d_11[3]}

ꢀꢀꢀ

;

ꢀꢀꢀꢀ

end else begin

ꢀꢀꢀꢀꢀꢀꢀꢀ

r_wr_fifo_data_1

ꢀꢀꢀꢀꢀꢀ

《=

ꢀꢀꢀꢀ

128'd0

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

;

ꢀꢀꢀꢀ

endendalways@(posedge pix_clk) begin

ꢀꢀꢀ

if(r_data_cnt==7&&model==model_x1&&odd_st==0) begin

ꢀꢀꢀꢀꢀꢀꢀꢀ

r_wr_fifo_data_2

ꢀꢀꢀꢀꢀꢀꢀꢀ

《=

ꢀꢀꢀꢀꢀꢀꢀ

{r_data_d_11[0],r_data_d_11[1],r_data_d_11[2],r_data_d_11[3],r_data_d_11[4],r_data_d_11[5],r_data_d_11[6],r_data_d_11[7]}

ꢀꢀꢀ

;

ꢀꢀꢀ

end else if(r_data_cnt==7&&model==model_x2) begin

ꢀꢀꢀꢀꢀꢀꢀꢀ

r_wr_fifo_data_2

ꢀꢀꢀꢀꢀꢀꢀꢀ

《=

ꢀꢀꢀꢀꢀꢀꢀ

{r_data_d_21[0],r_data_d_21[1],r_data_d_21[2],r_data_d_21[3],r_data_d_21[4],r_data_d_21[5],r_data_d_21[6],r_data_d_21[7]}

ꢀꢀꢀ

;

ꢀꢀꢀ

end else if(r_data_cnt%4==3&&model==model_x4) begin

ꢀꢀꢀꢀꢀꢀꢀꢀ

r_wr_fifo_data_2

ꢀꢀꢀꢀꢀꢀꢀꢀ

《=

ꢀꢀꢀꢀꢀꢀꢀ

{r_data_d_22[0],r_data_d_21[0],r_data_d_22[1],r_data_d_21[1],r_data_d_22[2],r_data_d_21[2],r_data_d_22[3],r_data_d_21[3]}

ꢀꢀꢀ

;

ꢀꢀꢀ

end else begin

ꢀꢀꢀꢀꢀꢀꢀꢀ

r_wr_fifo_data_2

ꢀꢀꢀꢀꢀꢀꢀꢀ

《=

ꢀꢀꢀꢀ

128'd0

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

;

ꢀꢀꢀ

endend

ddr3写模块将fifo1和fifo2的数据写入ddr3存储器中;之后,fpga按照oled规定的固定时序读出ddr3存储的视频数据并输出给oled显示器即可显示。

[0025]

上述仅为本发明的较佳实例及所运用技术原理,本发明不限于这里所述的特定实施例,对于数据时钟小于2.5倍ddr3用户时钟的前置电子变倍都在本发明的范围由所附的权利要求范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1