一种用于超大规模图像传感器的模数转换电路及量化方法

1.本发明属于模拟数字转换技术领域,涉及任意类型的用于cmos图像传感器的列级逐次逼近型模数转换电路及量化方法。

背景技术:

2.由于cmos图像传感器具有功耗低和成像速度快的特点,获得了大量的关注。随着图像传感器的广泛发展,在部分高速摄像中,对传感器的速度和精度提出了较高的要求。传统的应用于cmos图像传感器的逐次逼近型模数转换电路由于面积过大无法满足要求。

3.传统的逐次逼近型模数转换电路结构如附图1所示。包括比较器、采样保持电路、sar逻辑控制单元、c-dac。采样保持电路采取列级读出电路输出的模拟信号,比较器的输出端接sar逻辑控制单元的输入端,sar逻辑控制单元的输出端接采样保持电路的控制端、比较器的控制端和c-dac的控制端,参考电平接c-dac的输入端,比较器的正端接c-dac的输出端,比较器的负端接采样保持电路的输出端。

4.在上述的传统逐次逼近型模数转换器中,sar adc量化的过程主要是基于二进制搜索算法进行的,首先通过采样保持电路将采集到的像素电压输入到比较器的负端,同时sar逻辑控制单元将c-dac的最高位逻辑电平变为1,其余位置逻辑电平为0。比较器将采集到的像素电压和c-dac产生的1/2vref进行比较,如果比较器的输出为1,则像素电压小于1/2vref,逻辑控制单元将c-dac的最高位置为0,次高位置为1,其余位置为0,此时逻辑控制单元控制c-dac输出为1/4vref;如果比较器的输出为0,则像素电压大于1/2vref,逻辑控制单元将c-dac的最高位置为1,次高位置为1,其余位置为0,此时逻辑控制电路控制c-dac输出为3/4vref。然后比较器进行下一位的比较,不断重复上述过程,直到sar adc的所有位全部量化结束。

5.对于传统的应用于超大规模cmos图像传感器的列级sar adc,一个传统n位sar adc量化一个像素电压只需要n个时钟周期,而现阶段主要应用于cmos图像传感器的单斜式模数转换器完成n位的量化需要2n个时钟周期,故极大的提高了模数转换的的速度。但是由于每列sar adc都需要一个c-dac来提供量化过程的参考电平,巨大的电容数量导致面积成本以及功耗的大幅牺牲。对于大阵列的cmos图像传感器来说,每一列读出电路都需要一个sar adc进行模数转换,这就导致整个cmos图像传感器的模数转换器的部分占用太大的面积,以至于无法应用于实际设计,对于逐次逼近型模拟数字转换器若要应用于超大规模cmos图像传感器的列级读出电路,则必须进行一定程度的改进,减小列级sar adc的面积损耗。

技术实现要素:

6.针对现有技术中存在的问题,本发明提供一种用于超大规模图像传感器的模数转换电路及量化方法,解决现有逐次逼近型模数转换电路的面积问题,从而实现逐次逼近型模数转换电路在超大规模cmos图像传感器上的应用。

7.本发明是通过以下技术方案来实现:

8.一种用于超大规模图像传感器的模数转换电路,包括列级读出电路、复用型c-dac和列级布置的多个sar adc模块;所述sar adc模块包括寄存器、采样保持单元、多路加法器、比较器以及sar逻辑控制单元;

9.所述列级读出电路的输入端接像素单元,列级读出电路的各级输出端连接各sar adc模块的采样保持单元的输入端,采样保持单元的输出端接比较器的负端,所述复用型c-dac的参考电平输出端接多路加法器的输入端,多路加法器的输出端接比较器的正端,比较器的输出端接多路加法器和寄存器,sar逻辑控制单元接寄存器和多路加法器,sar逻辑控制单元控制多路加法器与复用型c-dac连接。

10.优选的,所述列级布置的多个sar adc模块的输出端接计数器。

11.优选的,所述像素单元为m

×

n像素阵列。

12.一种用于超大规模图像传感器的模数转换电路的量化方法,所述采样保持单元将像素电压输入至比较器的负端,sar逻辑控制单元将数字码的最高位置为1,其余位置为0,sar逻辑控制单元控制多路加法器从复用型c-dac得到参考电平并输入至比较器正端,比较器将像素电压和从复用型c-dac得到的1/2vref进行比较;

13.当比较器的输出为1,则像素电压小于1/2vref,sar逻辑控制单元将数字码最高位置为0,次高位为1,其余位为0并存入寄存器,同时sar逻辑控制单元控制多路加法器从复用型c-dac得到1/4vref并输入到比较器正端,然后比较器进行下一位的比较并重复该过程,直到sar adc模块的所有位全部量化结束。

14.优选的,当比较器的输出为0,则像素电压大于1/2vref,逻辑控制单元将最高位为1,次高位为1,其余位为0的数字码存入寄存器,同时sar逻辑控制单元控制该列sar adc的多路加法器从复用型c-dac得到3/4vref并输入到比较器正端。然后比较器进行下一位的比较,不断重复上述过程,直到sar adc模块的所有位全部量化结束。

15.与现有技术相比,本发明具有以下有益的技术效果:

16.本发明提供的一种用于超大规模图像传感器的模数转换电路,通过将每一列sar adc中的c-dac提取出来,由一个复用型c-dac提供所有列sar adc需要的参考电平,将应用于图像传感器中的n列sar adc模块需要的n个内置c-dac替换成了一个复用型c-dac,在保持原有结构的精度和速度优势的基础上,比传统的列级sar adc大幅度减小了面积成本,实现了sar adc模块在超大规模cmos图像传感器上的应用。

17.该用于超大规模图像传感器的模数转换电路的量化方法,采用的复用型c-dac能够同时提供各列sar adc所有需要的参考电平值,在不同列sar adc模块从复用型c-dac获取参考电平时互不影响,相互独立,各列sar adc模块通过多路加法器从复用型c-dac得到需要的参考电平,通过逻辑控制单元完成逐次逼近过程,实现了c-dac的复用,在不牺牲大面积的情况下,完成高速高精度的列读取进程,大大减小了芯片整体面积,并降低了列级功耗,为列级sar adc在超大规模cmos图像传感器上的应用提供了可行的解决方案,采用该量化方法得到了面积更小的应用于cmos图像传感器的列级sar adc模块的设计方案,为sar adc模块在超大规模cmos图像传感器上的应用提供了具体可行的实施方案。

附图说明

18.图1为传统的逐次逼近型模数转换电路示意图;

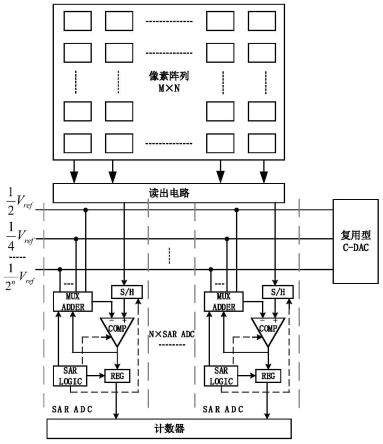

19.图2为本发明应用于超大规模图像传感器的列级逐次逼近型模数转换电路示意图;

20.图3为本发明量化过程的阐述示意图。

具体实施方式

21.下面结合附图对本发明做进一步的详细说明,所述是对本发明的解释而不是限定。

22.如图2所示,一种用于超大规模图像传感器的模数转换电路,包括列级读出电路、复用型c-dac、计数器和列级布置的多个sar adc模块;

23.所述的sar adc模块包括寄存器、采样保持单元、多路加法器、比较器以及用于控制整体逻辑的sar逻辑控制单元。

24.所述列级读出电路的输入端接像素单元,列级读出电路的输出端接采样保持单元的输入端,采样保持单元的输出端接比较器的负端,所述复用型c-dac的参考电平输出接多路加法器的输入端,多路加法器的输出端接比较器的正端,比较器的输出端接多路加法器和寄存器,sar逻辑控制单元接寄存器和多路加法器,sar逻辑控制单元控制多路加法器与复用型c-dac连接,sar adc模块的输出端接计数器。

25.该用于超大规模cmos图像传感器的模数转换电路,sar adc模块中的采样保持电路,比较器和寄存器与传统sar adc结构一致,列级读出电路和像素单元都与传统结构一致,所不同的是内置c-dac从sar adc结构提取出来替换成一个复用型c-dac提供参考电平,增加了一个多路加法器将复用型c-dac提供的参考电平输入到sar adc中。

26.参阅图3,该用于超大规模cmos图像传感器的模数转换电路的工作方法如下,其中,1/2nvref是复用型c-dac产生的参考电平值。与传统的cmos图像传感器列级sar adc的工作流程不同,本发明的工作流程:第一步准备阶段,第二步sar adc的采样阶段,第三步sar adc的量化阶段,具体如下:

27.第一步,准备阶段,复用型c-dac产生列级逐次逼近型模数转换电路整个量化过程需要的全部参考电平,此阶段产生的参考电平在接下来的工作周期内保持不变,各参考电平互不影响且相互独立。

28.需要注意的是,该第一阶段在一个工作流程中只需要进行一次。

29.第二步,采样保持阶段,此阶段列级读出电路读出各列像素单元的模拟输出值,通过采样保持单元进行采样放大,将采样得到的模拟信号输入到比较器的负端。此时sar逻辑控制单元将数字码的最高位置为1,其余位置为0,通过逻辑控制单元控制多路加法器从复用型c-dac得到此时需要的参考电平然后输入到比较器正端,比较器将像素电压和得到的1/2vref进行比较。

30.第三步,量化阶段,这是整个流程中最重要的部分,sar逻辑控制单元首先将数字码初始值的最高位置为1,其余位置为0,并控制多路加法器从复用型c-dac得到1/2vref,sar adc模块中的比较器将像素电压和1/2vref进行比较。

31.此时,如果比较器的比较结果输出为高电平,则该列模拟电压小于1/2vref,逻辑

控制单元将数字码的最高位置为0,次高位置为1,其余位置为0并存入该列sar adc的寄存器中,同时逻辑控制单元控制多路加法器向该列sar adc模块的比较器正端输入1/4vref;

32.如果比较器的比较结果输出为低电平,则像素电压大于1/2vref,逻辑控制单元数字码将最高位置为1,次高位置为1,其余位置为0并存入寄存器中,同时逻辑控制单元控制多路选择器从复用型c-dac得到3/4vref并输入到比较器正端。然后比较器进行下一位的比较,不断重复上述过程,直到sar adc的所有位全部量化结束。

33.在这个阶段中,复用型c-dac能够同时提供1/2nvref,sar adc模块通过逻辑控制单元控制多路加法器从复用型c-dac得到需要的参考电平值,然后sar adc通过逻辑控制单元完成逐次逼近过程。

34.本发明提供的用于超大规模cmos图像传感器的模数转换电路,较传统结构上大幅度缩小了面积和功耗成本,提出的c-dac复用方法具有以下优势:首先,利用复用型c-dac可以使n列sar adc减少n-1个c-dac,大幅度减小了模数转换器占用图像传感器芯片的面积,使得在同等面积要求下可以进行更大规模的列读取;其次,sar adc模块面积的减小使得sar adc模块在图像传感器上有了更好的应用,同时相较常用于超大规模cmos图像传感器的单斜式模数转换结构实现了更高速的模数转换。利用本文提出的方法为sar adc模块在超大规模cmos图像传感器上的应用提供了具体可行的实施方案。

35.本发明的用于超大规模cmos图像传感器的模数转换电路,首先由复用型c-dac产生整个模数转换过程中需要的参考电平且保持不变,sar adc模块通过逻辑电路控制多路加法器从复用型c-dac得到需要的参考电平,实现了sar adc模块中c-dac的复用,在不牺牲大面积的情况下,完成高速高精度列读取进程。本发明将c-dac从sar adc模块中提取出来,仅仅通过一个复用型c-dac提供所有sar adc模块需要的参考电平,并利用sar adc模块内部的逻辑控制电路完成逐次逼近的过程,实现了c-dac的复用,大大减小了芯片整体面积,并降低了列级功耗,为列级sar adc在超大规模cmos图像传感器上的应用提供了可行的解决方案。

36.以上内容仅为说明本发明的技术思想,不能以此限定本发明的保护范围,凡是按照本发明提出的技术思想,在技术方案基础上所做的任何改动,均落入本发明权利要求书的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1