带宽资源分配方法、PCIe通道切换器及电子设备与流程

带宽资源分配方法、pcie通道切换器及电子设备

技术领域

1.本技术涉及计算机技术领域,尤其涉及一种带宽资源分配方法、pcie通道切换器及电子设备。

背景技术:

2.随着高速串行计算机扩展总线标准(peripheral component interconnect express,pcie)规范逐步演进,目前已演进到pcie5.0和pcie6.0,pcie5.0单个lane的速率可达到32.0gt/s,4gb/s的带宽,pcie6.0单个lane的速率可达到64.0gt/s,8gb/s的带宽。处理器都是通过pcie x4或者pcie x2连接闪存固态硬盘(solid state drives,ssd),即是将4个或2个lane合并为一个通道连接ssd,从而实现主机与ssd之间的高带宽需求。这种方式比较固化,无法实现pcie带宽资源的灵活配置。

技术实现要素:

3.本技术实施例提供了一种带宽资源分配方法、pcie通道切换器及电子设备,可以实现pcie带宽资源的灵活分配。

4.第一方面,本技术实施例提供一种带宽资源分配方法,该方法应用于电子设备中,所述电子设备包括处理器、pcie通道切换器、存储模块以及通信模块;所述处理器与所述pcie通道切换器之间通信连接,所述pcie通道切换器分别与所述存储模块和所述通信模块之间通信连接;所述方法包括:

5.所述pcie通道切换器获取目标带宽资源分配方案,所述目标带宽资源分配方案用于指示将所述处理器与所述pcie通道切换器之间的pcie带宽资源分配给所述存储模块或所述通信模块中的任意一个;或者所述目标带宽资源分配方案用于指示将所述处理器与所述pcie通道切换器之间的pcie带宽资源分配给所述存储模块和所述通信模块之间的比例;

6.所述pcie通道切换器根据所述目标带宽资源分配方案,进行带宽资源分配。

7.上述方法,通过该目标带宽资源分配方案指示将处理器与pcie通道切换器之间的pcie带宽资源分配给存储模块或通信模块中的任意一个,或者指示分配给存储模块和通信模块之间的比例,从而pcie通道切换器根据目标带宽资源分配方案配置pcie通道切换器与所述存储模块之间的pcie带宽,和/或,配置pcie通道切换器与通信模块之间的pcie带宽,实现pcie带宽资源的灵活配置。

8.在一种可能的实现中,所述pcie通道切换器根据所述目标带宽资源分配方案,进行带宽资源分配,包括:所述pcie通道切换器根据所述目标带宽资源分配方案,配置所述pcie通道切换器与所述存储模块之间的pcie带宽,和/或,所述pcie通道切换器根据所述目标带宽资源分配方案,配置所述pcie通道切换器与所述通信模块之间的pcie带宽。

9.在一种可能的实现中,所述处理器与所述pcie通道切换器之间通过至少一个第一pcie通道连接;所述处理器与所述pcie通道切换器之间的pcie带宽资源包括所述至少一个第一pcie通道的pcie带宽资源。

10.上述方法,pcie通道切换器与处理器之间通过至少一个第一pcie通道连接,从而将该至少一个第一pcie通道的pcie带宽资源进行灵活配置。

11.在一种可能的实现中,所述pcie通道切换器与所述存储模块之间通过至少一个第二pcie通道连接;

12.所述pcie通道切换器根据所述目标带宽资源分配方案,配置所述pcie通道切换器与所述存储模块之间的pcie带宽,包括:确定分配给所述存储模块的带宽资源大小并根据分配给所述存储模块的带宽资源大小,配置使用所述至少一个第二pcie通道中的一个或多个第二pcie通道与所述存储模块进行数据存取操作;所述一个或多个第二pcie通道的pcie带宽资源总和小于或等于分配给所述存储模块的带宽资源大小。

13.上述方法,pcie通道切换器可以灵活的从pcie通道切换器与所述存储模块之间连接的至少一个第二pcie通道中选择一个或多个第二pcie通道与存储模块之间进行数据存取操作,从而实现第二pcie通道的灵活选择。

14.在一种可能的实现中,所述存储模块包括至少一个存储器,所述第二pcie通道中的每一个分别与所述至少一个存储器一一连接。

15.上述方法,每个第二pcie通道与每个存储器之间一一连接,从而可以实现灵活选择存储器进行存取操作。

16.在一种可能的实现中,所述至少一个第二pcie通道中包括一种规格的pcie通道或多种不同规格的pcie通道,其中,不同规格的pcie通道包含的lane的数量不同。

17.上述方法,可以实现不同规格的第二pcie通道的混排,从而可以灵活选择不同规格或相同规格的第二pcie通道配置pcie带宽资源。

18.在一种可能的实现中,所述pcie通道切换器与所述通信模块之间通过至少一个第三pcie通道连接;

19.所述pcie通道切换器根据所述目标带宽资源分配方案,配置所述pcie通道切换器与所述通信模块之间的pcie带宽,包括:确定分配给所述通信模块的带宽资源大小并根据分配给所述通信模块的带宽资源大小,配置使用所述至少一个第三pcie通道中的一个或多个第三pcie通道与所述通信模块进行数据传输,所述一个或多个第三pcie通道的pcie带宽资源总和小于或等于分配给所述通信模块的带宽资源大小。

20.上述方法,pcie通道切换器可以灵活的从pcie通道切换器与所述通信模块之间连接的至少一个第三pcie通道中选择一个或多个第二pcie通道与通信模块之间进行数据传输,从而实现第三pcie通道的灵活选择。

21.在一种可能的实现中,所述通信模块包括至少一个网卡,所述第三pcie通道中的每一个分别与所述至少一个网卡一一连接。

22.上述方法,每个第三pcie通道与每个网卡之间一一连接,从而可以实现灵活选择网卡进行数据传输。

23.在一种可能的实现中,所述至少一个第三pcie通道中包括一种规格的pcie通道或多种不同规格的pcie通道,其中,不同规格的pcie通道包含的lane的数量不同。

24.上述方法,可以实现不同规格的第三pcie通道的混排,从而可以灵活选择不同规格或相同规格的第三pcie通道配置pcie带宽资源。

25.在一种可能的实现中,所述pcie通道切换器获取目标带宽资源分配方案,包括:

26.所述pcie通道切换器从基板管理控制器bmc接收指示信息,所述指示信息用于指示所述目标带宽资源分配方案。

27.上述方法,所述pcie通道切换器可以从bmc中获取目标带宽资源分配方案,从而便于pcie通道切换器进行pcie带宽资源的配置。

28.在一种可能的实现中,所述目标带宽资源分配方案是根据所述存储模块的存储性能需求参数,和/或,所述通信模块所传输业务数据的速率需求确定。

29.上述方法,可以根据存储模块和/或通信模块的需求确定目标带宽资源分配方案,从而满足存储模块的存取需求以及通信模块的数据传输需求。

30.第二方面,本技术实施例还提供一种电子设备中的pcie通道切换器,所述电子设备还包括第一处理器、存储模块以及通信模块;所述第一处理器与所述pcie通道切换器之间通信连接,所述pcie通道切换器分别与所述存储模块和所述通信模块之间通信连接;所述pcie通道切换器包括:第二处理器,存储器,所述存储器与所述第二处理器耦合;所述存储器用于存储计算机指令;所述第二处理器用于调用所述计算机指令执行:

31.获取目标带宽资源分配方案,所述目标带宽资源分配方案用于指示将所述处理器与所述pcie通道切换器之间的pcie带宽资源分配给所述存储模块和所述通信模块中的任意一个;或者所述目标带宽资源分配方案用于指示将所述处理器与所述pcie通道切换器之间的pcie带宽资源分配给所述存储模块和所述通信模块之间的比例;

32.根据所述目标带宽资源分配方案,进行带宽资源分配。

33.在一些可能的实现中,处理器还用于执行上述第一方面任意一种可能的实现中的步骤,这里不再赘述。

34.第三方面,本技术实施例还提供一种电子设备,包括:第一处理器、pcie通道切换器、存储模块以及通信模块;所述第一处理器与所述pcie通道切换器之间通信连接,所述pcie通道切换器分别与所述存储模块和所述通信模块之间通信连接,所述pcie通道切换器包括至少一个第二处理器、内存,所述第二处理器耦合所述内存;所述内存中存储计算指令,所述第二处理器用于调用所述计算指令执行上述第一方面任意一种可能的实现中的带宽资源分配方法。

35.第四方面,本技术实施例还提供一种计算机存储介质,包括计算机指令,当所述计算机指令在电子设备上运行时,使得所述电子设备执行如第一方面或第一方面中任一可能的实现描述的方法。

36.第五方面,本技术实施例还提供一种计算机程序产品,当上述计算机程序产品在电子设备上运行时,使得所述电子设备执行如第一方面或第一方面中任一可能的实现描述的方法。

37.可以理解地,上述提供的第二方面提供的pcie通道切换器、第三方面提供的电子设备、第四方面提供的计算机存储介质和第六方面提供的计算机程序产品均可实现上述第一方面所提供的方法。因此,其所能达到的有益效果可参考第一方面中对应的有益效果,此处不再赘述。

附图说明

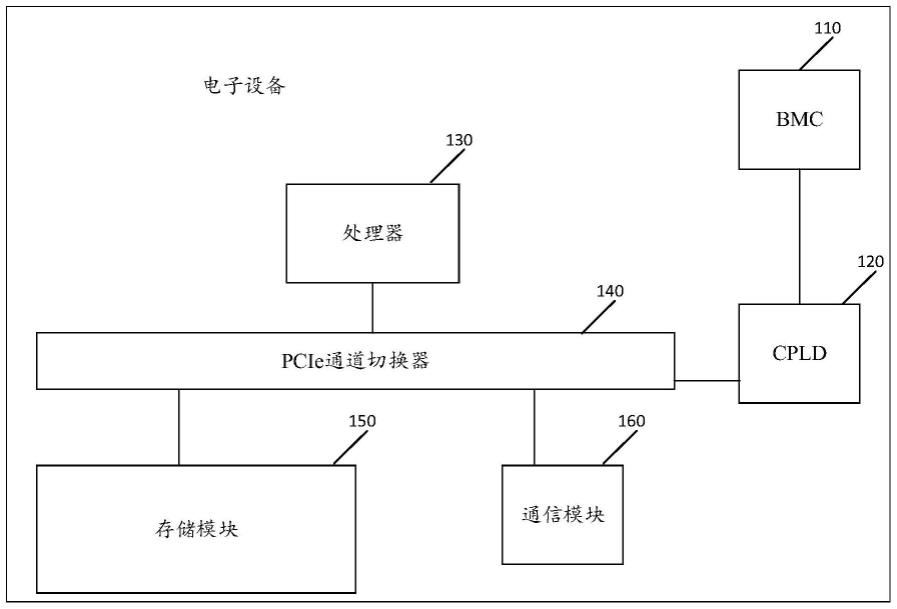

38.图1a是本技术实施例提供的一种电子设备的硬件架构示例图;

39.图1b是本技术实施例提供的另一种电子设备的硬件结构示例图;

40.图1c是本技术实施例提供的又一种电子设备的硬件结构示例图;

41.图1d是本技术实施例提供的又一种电子设备的硬件结构示例图;

42.图1e是本技术实施例提供的又一种电子设备的硬件结构示例图;

43.图1f是本技术实施例提供的又一种电子设备的硬件结构示例图;

44.图2a是本技术实施例提供的一种资源分配方案示意图;

45.图2b是本技术实施例提供的另一种资源分配方案示意图;

46.图2c是本技术实施例提供的又一种资源分配方案示意图;

47.图3a是本技术实施例提供的一种bmc的结构示意图;

48.图3b是本技术实施例提供的一种pcie通道切换器;

49.图4是本技术实施例提供的一种带宽资源分配方法的流程示意图;

50.图5是本技术实施例提供的另一种带宽资源分配方法的流程示意图。

具体实施方式

51.首先对本技术实施例涉及的术语进行说明。

52.pcie

53.pcie是一种高速串行计算机扩展总线标准,它的主要优势就是数据传输速率高,而且还有相当大的发展潜力。随着pcie标准的逐步演进,目前已演进到pcie5.0和pcie6.0,pcie5.0单个lane的速率可达到32.0gt/s,4gb/s的带宽,pcie6.0单个lane的速率可达到64.0gt/s,8gb/s的带宽。通常可以将2n个lane合并为一个通道,从而形成多种pcie规格的pcie通道,其中,n为大于或者等于0的整数。例如,pcie x1是指将一个lane作为一个pcie通道,pcie x2是指将两个lane合并为一个pcie通道,pcie x4是指将四个lane合并为一个pcie通道,以此类推。以pcie5.0为例说明,pcie x2通道的带宽可达8gb/s,pcie x4通道的带宽可达16gb/s。

54.如图1a所示,为本技术实施例提供的一种电子设备的硬件架构示例图,该电子设备可以是服务器,也可以是基站、路由器等网关设备或网络设备,还可以是笔记本电脑、台式电脑、平板电脑、手机等终端设备。其中,服务器可以是文件服务器(file server)、域控制服务器(domain server)、数据库服务器(database server),邮件服务器(mail server),web服务器(web server),多媒体服务器(multimedia server),通讯服务器(communication server),终端服务器(terminal server),基础架构服务器(infrastructure server),虚拟化服务器(virtualization server)等。服务器可以是塔式、机架式、刀片式等。电子设备可以但不限于采用x86架构,精简指令集计算机(reduced instruction set computer,risc)架构,进阶精简指令集机器(advanced risc machine,arm)架构等。

55.该电子设备可以包括但不限于:基板管理控制器(baseboard management controller,bmc)110、复杂可编程逻辑器件(complex programmable logic device,cpld)120、一个或多个处理器130、pcie通道切换器140、存储模块150、通信模块160等中的部分或全部。其中,处理器130可以是中央处理器(central processing unit,cpu)。

56.处理器130与pcie通道切换器140之间通过第一pcie通道进行通信,该第一pcie通

道可以是通过至少一个lane合并得到,例如,如果该第一pcie通道是通过16个lane合并得到的,则该第一pcie通道为pcie x16。其中,每个lane上的速率与pcie标准有关。例如,若pcie6.0单个lane的速率可达到8gb/s的带宽。

57.pcie通道切换器140与存储模块150之间通过第二pcie通道进行通信,该第二pcie通道也可以是通过至少一个lane合并得到。存储模块150可以包括外部存储器,例如ssd。

58.pcie通道切换器140与通信模块160之间通过第三pcie通道进行通信,该第三pcie通道也可以是通过至少一个lane合并得到。通信模块160可以为用于与外部进行通信的模块,例如,网卡。

59.处理器130可以集成内存控制器。将内存控制器集成到处理器130中可以有效控制内存控制器工作在与处理器核心同样的频率上。

60.bmc 110主要用于对电子设备进行监控和管理,是独立于电子设备之外的小型操作系统,是一个集成在主板上的芯片。在本技术实施例中,bmc 110可以用于确定将处理器130与pcie通道切换器之间的第一pcie通道的带宽资源分配给存储模块150和/或通信模块160的带宽资源分配方案,并将该带宽资源分配方案指示给cpld120,通过cpld120将该带宽资源分配方案指示给pcie通道切换器140。pcie通道切换器140根据该带宽资源分配方案进行通道配置。

61.在一些实施例中,电子设备还可以包括其他的处理单元,例如:包括应用处理器(application processor,ap),图形处理器(graphics processing unit,gpu),神经网络处理器(neural-network processing unit,npu),调制解调处理器,图像信号处理器(image signal processor,isp),存储器,视频编解码器,数字信号处理器(digital signal processor,dsp),基带处理器等。其中,不同的处理单元可以是独立的器件,也可以集成在一个或多个处理器中。

62.处理器130中还可以设置存储器,用于存储指令和数据。在一些实施例中,处理器130中的存储器为高速缓冲存储器。该存储器可以保存处理器130刚用过或循环使用的指令或数据。如果处理器130需要再次使用该指令或数据,可从所述存储器中直接调用。避免了重复存取,减少了处理器13010的等待时间,因而提高了电子设备的数据处理效率。

63.上述存储器可以是动态随机存取存储器(dynamic random access memory,dram)、同步动态随机存取内存(synchronous dynamic random-access memory,sdram)、双倍速率同步动态随机存储器(double data rate sdram,ddr sdram)等。

64.pcie通道切换器140、基板管理控制器(baseboard management controller,bmc)110、存储模块150、通信模块160等可以是电子设备的主板上的芯片组。

65.其中,bmc 110与cpld120之间可以通过bmc-cpld通信总线连接,例如localbus、lps、i2c、spi等,cpld120与pcie通道切换器140之间可以通过cpld-pcie switch通信总线连接,例如i2c或uart等。

66.还应理解,不限于图1a所指的电子设备,电子设备还可以包括更多或更少的单元,

67.可以理解的是,本发明实施例示意的结构并不构成对电子设备的具体限定。在本技术另一些实施例中,电子设备可以包括比图示更多或更少的部件,或者组合某些部件,或者拆分某些部件,或者不同的部件布置。图示的部件可以以硬件,软件或软件和硬件的组合实现。

68.如图1b所示,为本技术实施例提供的另一种电子设备的结构示意图,可理解,该实施例中的电子设备可以是图1a所示电子设备的一种细化实施例。如图1b所示,该电子设备可包括bmc210、cpld220、一个或多个处理器230、pcie通道切换器240、存储模块250、通信模块260等中的部分或全部,其中,存储模块250包括分别与pcie通道切换器连接的16个ssd,可理解,存储模块250包含的ssd的数量还可以是其他数字,本技术以16作为举例。其中,处理器230可以是中央处理器(central processing unit,cpu)。

69.该电子设备可以是服务器,也可以是手机、平板电脑、个人计算机、智能电视、车载设备等终端,还可以是基站、路由器等网络设备,这里不作限定。

70.处理器230通过pcie x16的第一pcie通道与pcie通道切换器240进行连接,pcie通道切换器240通过pcie x4的第二pcie通道与每个ssd连接,pcie通道切换器240通过两个pcie x8的第三pcie通道与通信模块260连接,可理解,通信模块260可包括两个网卡,pcie通道切换器240通过pcie x8的第三pcie通道与每个网卡连接。存储模块250和通信模块260共享处理器pcie x16的带宽资源。

71.在一些实施例中,电子设备还可以包括其他的处理单元,例如:包括应用处理器(application processor,ap),图形处理器(graphics processing unit,gpu),神经网络处理器(neural-network processing unit,npu),调制解调处理器,图像信号处理器(image signal processor,isp),存储器,视频编解码器,数字信号处理器(digital signal processor,dsp),基带处理器等。其中,不同的处理单元可以是独立的器件,也可以集成在一个或多个处理器中。

72.处理器230中还可以设置存储器,用于存储指令和数据。在一些实施例中,处理器230中的存储器为高速缓冲存储器。该存储器可以保存处理器230刚用过或循环使用的指令或数据。如果处理器230需要再次使用该指令或数据,可从所述存储器中直接调用。避免了重复存取,减少了处理器230的等待时间,因而提高了电子设备的数据处理效率。

73.在一些实施例中,电子设备还可以包括bmc210和cpld220等。

74.如图1c所示,为本技术实施例提供的又一种电子设备的结构示意图,可理解,该实施例中的电子设备可以是图1a所示电子设备的一种细化实施例。图1c所示实施例与图1b所示实施例的区别在于,pcie通道切换器240通过pcie x4的第二pcie通道与一部分ssd连接,pcie通道切换器240通过pcie x2的第二pcie通道与另一部分ssd连接。如图1c所示,pcie通道切换器240通过8个pcie x4的第二pcie通道分别与8个ssd连接,pcie通道切换器240通过8个pcie x2的第二pcie通道分别与8个ssd连接。

75.如图1d所示,为本技术实施例提供的又一种电子设备的结构示意图,可理解,该实施例中的电子设备可以是图1a所示电子设备的一种细化实施例。图1d所示实施例与图1b所示实施例的区别在于,pcie通道切换器240通过pcie x4的第二pcie通道与一部分ssd连接,pcie通道切换器240通过pcie x1的第二pcie通道与另一部分ssd连接。如图1d所示,pcie通道切换器240通过8个pcie x4的第二pcie通道分别与8个ssd连接,pcie通道切换器240通过8个pcie x1的第二pcie通道分别与8个ssd连接。

76.如图1e所示,为本技术实施例提供的又一种电子设备的结构示意图,可理解,该实施例中的电子设备可以是图1a所示电子设备的一种细化实施例。图1e所示实施例与图1b所示实施例的区别在于,pcie通道切换器240通过pcie x4的第二pcie通道与一部分ssd连接,

pcie通道切换器240通过pcie x2的第二pcie通道与另一部分ssd连接,pcie通道切换器240通过pcie x1的第二pcie通道与又一部分ssd连接。如图1e所示,pcie通道切换器240通过8个pcie x4的第二pcie通道分别与8个ssd连接,pcie通道切换器240通过4个pcie x2的第二pcie通道分别与4个ssd连接。pcie通道切换器240通过4个pcie x1的第二pcie通道分别与4个ssd连接。

77.如图1f所示,为本技术实施例提供的又一种电子设备的结构示意图,可理解,该实施例中的电子设备可以是图1a所示电子设备的一种细化实施例。图1f所示实施例与图1b所示实施例的区别在于,pcie通道切换器240通过pcie x1的第二pcie通道与ssd连接。如图1f所示,pcie通道切换器240通过16个pcie x1的第二pcie通道分别与16个ssd连接。

78.可理解,以上图1b-图1f是以pcie通道切换器240与存储模块中ssd之间的第二pcie通道分布作为举例,pcie通道切换器240与通信模块之间的至少一个第三pcie通道也可以参照pcie通道切换器240与存储模块之间的至少一个第二pcie通道的分布,即不同规格的第三pcie通道混排。

79.需要说明的是,以上对各个pcie通道的阐述仅为举例,本技术不限定各个pcie通道所包含lane的数量,以及各个pcie通道的混排分布。

80.其中,在以上图1b-图1f所示实施例中,bmc210可以确定将处理器的pcie x16的带宽资源分配给存储模块250和/或通信模块260的资源分配方案。例如,可以将pcie x16的带宽资源全部分配给存储模块250中的ssd,具体可以参照后续实施例中图2a的实施例描述,在此不再赘述。又例如,可以将pcie x16的带宽资源全部分配给通信模块260,具体可以参照后续实施例中图2b的实施例描述,在此不再赘述。再例如,可以将pcie x16的带宽资源均衡分配给存储模块250和通信模块260,具体可以参照后续实施例中图2c的实施例描述,在此不再赘述。可理解,资源分配方案可以不仅包含于图2a-图2c的三种可选实施方式,还可以是其他分配方案,本技术不作限定。

81.cpld220用于将bmc所确定的带宽资源分配方案指示给pcie通道切换器240,pcie通道切换器240可以根据cpld220指示的带宽资源分配方案进行通道配置。

82.以下结合附图2a-附图2c对本技术实施例的三种可选的带宽资源分配方案进行举例说明。可理解,在以下三种可选的带宽资源分配方案中,pcie通道切换器与存储模块以及通信模块的连接方式可以采用以上图1b-图1f中任一种连接方式,当然还可以是其他连接方式,本技术不作限定。需要说明的是,在图2a-图2c中pcie通道切换器里面的连线可理解为该pcie通道切换器配置使用该些第二pcie通道和/或第三pcie通道,可理解,如图2a-图2c中的配置仅为举例,不对本技术构成限定。

83.如图2a所示,为本技术实施例提供的一种资源分配方案的示意图,如图2a所示,pcie通道切换器320可以将处理器的pcie x16的带宽资源全部分配给存储模块330,而通信模块310的通道不可用。该种资源分配方案可以称为单存储模式。例如,在一些对存储性能要求比较高的场景下,可采用该种资源分配方案。

84.如图2a所示,pcie通道切换器320分别与各个ssd连接,其中,pcie通道切换器320分别与各个ssd之间的连接方式可以参照图1b-图1f中的任一种连接方式。例如,采用图1b所示的连接方式,pcie通道切换器320与一个ssd之间可以采用pcie x4的第二pcie通道连接,即四个lane合并为一个第二pcie通道。可理解,pcie x4的第二pcie通道可承载小于或

者等于pcie x4的带宽速率。在图2a所示的实施例中,如果采用图1b所示的连接方式,可将处理器的pcie x16的带宽资源分配给4个ssd,即配置使用4个第二pcie通道,每个ssd的带宽速率是pcie x4的带宽速率,例如,采用的是pcie6.0标准,则pcie x4的带宽速率可达到32gb/s。可理解,也可以采用图1f所示的连接方式,pcie通道切换器320与一个ssd之间可以采用pcie x1的第二pcie通道连接,即一个lane合并为一个pcie通道。将处理器的pcie x16的带宽资源分配给16个ssd,每个ssd的带宽速率是pcie x1的带宽速率。又例如,也可以采用图1c、图1d以及图1e所示的混排方式进行组合,则pcie通道切换器可以从不同规格的第二pcie通道中选择部分第二pcie通道进行组合,例如,如果采用图1c所示的混排方式进行组合,pcie通道切换器可以选择2个pcie x4的第二pcie通道,且选择4个pcie x2的第二pcie通道共享处理器的pcie x16的带宽资源。

85.如图2b所示,为本技术实施例提供的另一种资源分配方案的示意图,如图2b所示,pcie通道切换器320可以将处理器的pcie x16的带宽资源全部分配给通信模块310,而存储模块330的通道不可用。该种资源分配方案可以称为单网络模式。例如,在传输一些如视频、音频等高带宽需求的业务数据时,可采用该种资源分配方案。可理解,在图2b中的通信模块可以包括一个或多个网卡。

86.如图2b所示,pcie通道切换器320通过两个pcie x8的pcie通道与通信模块310连接,示例性的,该通信模块310可以包括两个网卡,pcie通道切换器320与一个网卡之间可以采用pcie x8的第三pcie通道连接,即八个lane合并为一个第三pcie通道。可理解,pcie x8的第三pcie通道可承载小于或者等于pcie x8的带宽速率。在图2b所示的实施例中,可将处理器的pcie x16的带宽资源全部分配给存储模块310的两个网卡,即配置使用2个第三pcie通道,每个网卡的带宽速率是pcie x8的带宽速率,例如,采用的是pcie6.0标准,则pcie x8的带宽速率可达到64gb/s。可理解,通信模块310中两个第三pcie通道也可以采用混排的方式,例如,其中一个第三pcie通道包括8个lane,另一个第三pcie通道包括16个lane。pcie通道切换器可以将pcie x16的带宽资源全部分配给包括16个lane的第三pcie通道,或者,可以将pcie x16的带宽资源一半的带宽资源分配给包括8个lane第三pcie通道,另一半分配给包括16个lane的第三pcie通道,本技术不作限定。

87.如图2c所示,为本技术实施例提供的又一种资源分配方案的示意图,pcie通道切换器320可以将处理器的pcie x16的带宽资源部分配给存储模块330,部分分配给通信模块310,例如,将一半的带宽资源分配给存储模块330,一半的带宽资源分配给通信模块310。该种资源分配方案可以称为性能均衡模式。例如,在一些对存储性能要求不高且传输的业务数据对带宽速率要求也不高的场景下,可采用该种资源分配方案。

88.如图2c所示,pcie通道切换器320分别与各个ssd连接,其中,pcie通道切换器320分别与各个ssd之间的连接方式可以参照图1b-图1f中的任一种连接方式。例如,采用图1b所示的连接方式,pcie通道切换器320与一个ssd之间可以采用pcie x4的第二pcie通道连接,即四个lane合并为一个第二pcie通道。在图2c所示的实施例中,可将处理器的pcie x16的一半带宽资源分配给2个ssd,即配置使用2个第二pcie通道,每个ssd的带宽速率是pcie x4的带宽速率,例如,采用的是pcie6.0标准,则pcie x4的带宽速率可达到32gb/s。将处理器的pcie x16的一半带宽资源分配给通信模块310的一个网卡,网卡的带宽速率是pcie x8的带宽速率,即配置使用1个第三pcie通道。例如,采用的是pcie6.0标准,则pcie x8的带宽

速率可达到64gb/s。可理解,也可以采用图1f所示的连接方式,pcie通道切换器320与一个ssd之间可以采用pcie x1的第二pcie通道连接,即一个lane合并为一个pcie通道。将处理器的pcie x16的一半带宽资源分配给8个ssd,每个ssd的带宽速率是pcie x1的带宽速率。又例如,也可以采用图1c、图1d以及图1e所示的混排方式进行组合,则pcie通道切换器可以从不同规格的第二pcie通道中选择部分第二pcie通道进行组合,例如,如果采用图1c所示的混排方式进行组合,pcie通道切换器可以选择1个pcie x4的第二pcie通道,且选择2个pcie x2的第二pcie通道共享处理器的pcie x16的一半带宽资源。可理解,如果通信模块也是采用混排方式进行pcie通道组合,也可以将选择不同规格的第三pcie通道共享处理器的pcie x16的一半带宽资源。

89.不限于上述三种可选的资源分配方案,还可以包括其他的资源分配方案,这里不再赘述,上述三种资源分配方案仅为举例。

90.如图3a所示,为本技术实施例提供的一种bmc 600的结构示意图。该bmc600可以包括处理器610以及存储器620。其中,处理器610耦合存储器620。

91.存储器620用于存储计算机指令,还可以存储资源选择方案等,处理器610执行存储器620存储的计算机指令,可以实现下述带宽资源分配方法的实施例中bmc执行的步骤。这里不再赘述。

92.应理解,bmc 600可以使用嵌入式系统,如linux系统等。bmc可以采用分层架构,可以包括但不限于应用层、系统层、驱动层和硬件层等。

93.其应用层可以包括但不限于资源分配系统,该资源分配系统可以包括资源分配方案确定模块和发送模块。其中,资源分配方案确定模块用于确定资源分配方案,发送模块用于向cpld指示所确定的资源分配方案。

94.其中,资源分配方案确定模块可以包括人机交互模块以及确定模块,该人机交互模块用于接收用户输入的资源选择信息,确定模块,用于根据用户输入的选择信息确定资源分配方案。

95.各个单元的具体实现还可以参见下述图4或图5所示的方法实施例中的相关描述,这里不再赘述。

96.如图3b所示,为本技术实施例提供的一种pcie通道切换器700的结构示意图。该bmc700可以包括处理器710以及存储器720。其中,处理器710耦合存储器720。

97.存储器720用于存储计算机指令,还可以存储资源选择方案等,处理器710执行存储器720存储的计算机指令,可以实现下述带宽资源分配方法的实施例中pcie通道切换器执行的步骤。这里不再赘述。

98.应理解,pcie通道切换器可以使用嵌入式系统,如linux系统等。pcie通道切换器可以采用分层架构,可以包括但不限于应用层、系统层、驱动层和硬件层等。

99.各个单元的具体实现还可以参见下述图4或图5所示的方法实施例中的相关描述,这里不再赘述。

100.以下结合图4和图5所示的流程示意图,介绍本技术实施例涉及的一种带宽资源分配方法,该方法可以由上述图1a所示的电子设备也可以由上述图1b所示的电子设备来实现。

101.如图4所示,为本技术实施例提供的一种带宽资源分配方法的流程示意图,该方法

可以包括但不限行于如下部分或全部步骤:

102.s101:bmc确定带宽资源分配方案。

103.为便于描述,将处理器与pcie通道切换器之间的pcie通道称为第一pcie通道,将pcie通道切换器与存储模块之间的pcie通道称为第二pcie通道,将pcie通道切换器与通信模块之间的pcie通道称为第三pcie通道。可理解,pcie通道切换器与存储模块之间可通过至少一个第二pcie通道通信连接,pcie通道切换器与通信模块之间可通过至少一个第三pcie通道通信连接。

104.其中,第一pcie通道可以包括2m个lane,该m为大于或者等于0的整数。可理解,本技术实施例中第一pcie通道的数量可以大于或者等于1,本技术不作限定,为便于描述,本技术以一个第一pcie通道作为举例。本技术实施例中可将该2m个lane的带宽资源分配给存储模块和通信模块中至少一个。示例性的,可将该2m个lane的带宽资源全部分配给存储模块,或者,也可以将该2m个lane的带宽资源全部分配给网络模块,或者,也可以将该2m个lane的带宽资源一部分分配给网络模块,一部分分配给存储模块,即网络模块和存储模块之间存在分配比例,本技术不作限定。

105.作为一种可选的实施方式,第二pcie通道可以包括2n个lane。可理解,若该存储模块包括多个ssd,则可以是一个第二pcie通道与一个ssd连接,如图1b所示,若该存储模块包括16个ssd,则可以通过16个第二pcie通道分别与该16个ssd连接。

106.作为一种可选的实施方式,第三pcie通道可以包括2

p

个lane。可理解,若该通信模块可以包括多个网卡,则可以是一个第三pcie通道与一个网卡连接,例如,若该通信模块包括2个网卡,则可以通过2个第三pcie通道分别与该2个网卡连接。

107.需要说明的是,第一pcie通道、第二pcie通道以及第三pcie通道中各个lane能够支持的最大速率可以相同也可以不同,换言之,第一pcie通道、第二pcie通道以及第三pcie通道的pcie标准可以是相同或不同的。例如,第一pcie通道的标准是pcie5.0,第二pcie通道和第三pcie通道的标准是pcie6.0。第一pcie通道、第二pcie通道以及第三pcie通道中各个lane能够支持的最大速率可以相同,第一pcie通道、第二pcie通道以及第三pcie通道可以均为pcie6.0的标准,本技术不作限定。

108.可以配置使用存储模块的至少一个第二pcie通道,和/或,配置使用通信模块的至少一个第三pcie通道。可理解,第一pcie通道、第二pcie通道以及第三pcie通道所采用的标准相同的情况下,通信模块和/或存储模块中配置使用的lane的数量需要小于或者等于第一pcie通道的数量与2m之间的乘积。

109.在本技术实施例中,m个lane所能够支持的最大带宽资源分配给存储模块和/或通信模块,示例性的,可以根据存储模块中存储设备的存储性能需求以及通信模块所传输业务数据的带宽需求,确定资源分配方案。

110.作为一示例,若存储模块中存储设备的存储性能需求高,需要高速率存储,比如,存储设备的存储速率需求大于第一阈值,则可以将2m个lane所能够支持的最大带宽资源全部分配给存储模块中的存储设备。存储模块的每个第二pcie通道包括2n个lane。以第一pcie通道和第二pcie通道采用相同的pcie标准为例进行举例说明,各个第二pcie通道包含的lane的个数相同,则可配置启动存储模块中2m/2n个ssd进行存取操作,即配置使用2m/2n个第二pcie通道。

111.作为另一示例,若通信模块中所传输的业务数据的带宽需求高,例如,传输视频类型的业务数据或音频类型的业务数据,则可以将2m个lane所能够支持的最大带宽资源全部分配给通信模块中的网卡。通信模块中每个第三pcie通道中包含2

p

个lane。以第一pcie通道和第三pcie通道采用相同的pcie标准为例进行举例说明,各个第三pcie通道包含的lane的个数相同,则可配置使用通信模块中2m/2

p

个网卡进行数据传输。

112.需要说明的是,为便于识别哪些业务数据的带宽需求高,本技术可以将带宽需求高的业务数据的数据标识作为预设数据标识加入数据库中,当检测到通信模块所传输的业务数据的数据标识与数据库中的预设数据标识匹配时,则可将2m个lane所能够支持的最大带宽资源全部分配给通信模块。其中,数据库中可以包括一个或多个预设数据标识。示例性的,该数据库中可以包括视频类型的数据标识和音频类型的数据标识。

113.作为又一示例,若存储模块中存储设备的存储性能需求不高,通信模块中所传输的业务数据的带宽需求也不高,则可以将2m个lane所能够支持的最大带宽资源一部分分配给存储模块中的存储设备,一部分分配给通信模块。比如,存储设备的存储速率需求小于第一阈值,通信模块所传输的业务数据的数据标识不是数据库中的预设数据标识,则可以将2m个lane所能够支持的最大带宽资源一部分分配给存储模块中的存储设备,一部分分配给通信模块。示例性的,可以通过存储设备的存储速率需求的具体值和/或通信模块所传输业务数据的速率需求的具体值,确定分配给存储模块和通信模块的带宽资源比例。比如,可以将2a个lane所能够支持的最大带宽资源分配给存储模块,将2b个lane所能够支持的最大带宽资源分配给通信模块,a和b为大于或者等于0的整数,且a+b=m。

114.可理解,若通信模块所传输的业务数据的带宽需求高,且存储模块的存储性能需求也高,则需要选择将带宽资源全部分配给通信模块或存储模块。

115.s102:bmc向cpld发送指示信息,该指示信息用于指示带宽资源分配方案。

116.s103:cpld向pcie通道切换器发送指示信息,该指示信息用于指示带宽资源分配方案。s104:pcie通道切换器根据指示信息,进行通道配置。

117.bmc在确定带宽资源分配方案之后,即可向cpld发送指示信息,该指示信息用于指示带宽资源分配方案,cpld接收到bmc发送的指示信息后,将该指示信息发送给pcie通道切换器,可理解,bmc也可以直接将指示信息发送给pcie通道切换器。

118.其中,该指示信息可以包括存储模块和通信模块之间的资源分配比例,例如,若将带宽资源全部分配给存储模块,则存储模块与通信模块之间的资源分配比例为1:0;又例如,将30%的带宽资源分配给存储模块,则存储模块与通信模块之间的资源分配比例为:3:7。可选的,该指示信息还可以包括配置使用第二pcie通道和/或第三pcie通道中lane的个数,和/或,配置使用第二pcie通道的通道个数和/或第三pcie通道的通道个数。

119.pcie通道切换器可根据接收到的指示信息,进行通道配置。其中,通道配置可以包括配置使用哪些第二pcie通道和/或哪些第三pcie通道。可理解,配置使用的所有第二pcie通道的带宽资源可以小于或者等于分配给存储模块的带宽资源,同理,配置使用的所有第三pcie通道的带宽资源可以小于或者等于分配给通信模块的带宽资源。

120.例如,存储模块与通信模块之间的资源分配比例为1:0,即将带宽资源全部分配给存储模块,如果第一pcie通道中包括16个lane,第二pcie通道包括1个lane,则pcie通道切换器配置16个第二pcie通道用于数据存取。可理解,pcie通道切换器配置使用的第二pcie

通道的带宽资源总和可以小于或者等于分配给存储模块的带宽资源大小,本技术不作限定。例如,pcie通道切换器可以配置8个第二pcie通道用于数据存取。可理解,也可以将带宽资源全部分配给通信模块,pcie通道切换器配置使用的第三pcie通道的带宽资源总和可以小于或者等于分配给通信模块的带宽资源大小,本技术不作限定。

121.上述实施例,bmc可以根据存储模块和通信模块的特点,确定合理的带宽资源分配方案,并将其指示给pcie通道切换器进行通道配置,能够实现灵活的带宽资源分配,并且保证存储模块和通信模块的带宽需求。

122.如图5所示,为本技术实施例提供的另一种带宽资源分配方法的流程示意图,该方法可以包括但不限行于如下部分或全部步骤:

123.s201,bmc配置至少一种资源分配方案。

124.其中,在bmc中预先配置至少一种资源分配方案。在一些实施例中,该至少一种资源分配方案可以被称为至少一种资源分配模式。示例性的,该bmc可以提供界面给用户设置,该界面可以是web界面,命令行界面等,用户可以通过该界面设置该至少一种资源分配方案。例如,可以设置单存储模式(storage only),即将第一pcie通道的带宽资源全部分配给存储模块,而通信模块的所有第三pcie通道不可用。还可以设置单网络模式,即将第一pcie通道的带宽资源全部分配给网络模块,而存储模块的所有第二pcie通道不可用。还可以设置性能均衡模式,将第一pcie通道的带宽资源的一半分配给存储模块,一半分配给网络模块。可理解,上述三种资源分配模式仅为举例,还可以包括其他资源分配模式,本技术不作限定。

125.在一些实施例中,还可以配置使用该至少一种资源分配方案中各个资源分配方案的使用条件。例如,可配置单存储模式所对应的使用条件为,存储模块的存储速率需求大于第一阈值。

126.s202,bmc从至少一种资源分配方案中确定目标资源分配方案。

127.在配置好至少一种资源分配方案之后,可以进一步从该至少一种资源分配方案中确定目标资源分配方案。在一些实施例中,可以是用户通过交互界面从至少一种资源分配方案中确定目标资源分配方案。在另一些实施例中,还可以是获取存储模块的存储速率需求,和/或,网络模块所传输业务数据的传输速率需求,根据该存储模块的存储速率需求和/或网络模块的业务数据的传输速率需求所满足的使用条件,确定所满足使用条件对应的目标资源分配方案。例如,若存储模块的存储速率需求较高,而网络模块传输的业务数据的传输速率需求比较低,则可以选择单存储模式的目标资源分配方案。

128.s203,bmc向cpld发送切换命令。

129.s204,cpld向pcie通道切换器发送切换命令。

130.s205,pcie通道切换器根据切换命令,进行通道配置。

131.bmc在确定目标资源分配方案之后,可以将指示该目标资源分配方案的切换命令发送给cpld,该cpld将该切换命令发送给pcie通道切换器。可理解,bmc也可以直接将指示该目标资源分配方案的切换命令发送给pcie通道切换器。

132.pcie通道切换器接收到来自cpld的切换命令之后,可以由当前采用的资源分配方案切换到目标资源分配方案,即按照目标资源分配方案进行通道的配置,重新分配pcie带宽资源。采用本技术实施例,可以实时监测存储模块和通信模块的需求,从而随时进行资源

分配方案的切换。

133.上述实施例中所使用的术语只是为了描述特定实施例的目的,而并非旨在作为对本技术的限制。如在本技术的说明书和所附权利要求书中所使用的那样,单数表达形式“一个”、“一种”、“所述”、“上述”、“该”和“这一”旨在也包括复数表达形式,除非其上下文中明确地有相反指示。还应当理解,本技术中使用的术语“和/或”是指并包含一个或多个所列出项目的任何或所有可能组合。

134.上述实施例中所用,根据上下文,术语“当

…

时”可以被解释为意思是“如果

…”

或“在

…

后”或“响应于确定

…”

或“响应于检测到

…”

。类似地,根据上下文,短语“在确定

…

时”或“如果检测到(所陈述的条件或事件)”可以被解释为意思是“如果确定

…”

或“响应于确定

…”

或“在检测到(所陈述的条件或事件)时”或“响应于检测到(所陈述的条件或事件)”。

135.在上述实施例中,可以全部或部分地通过软件、硬件、固件或者其任意组合来实现。当使用软件实现时,可以全部或部分地以计算机程序产品的形式实现。所述计算机程序产品包括一个或多个计算机指令。在计算机上加载和执行所述计算机程序指令时,全部或部分地产生按照本技术实施例所述的流程或功能。所述计算机可以是通用计算机、专用计算机、计算机网络、或者其他可编程装置。所述计算机指令可以存储在计算机可读存储介质中,或者从一个计算机可读存储介质向另一个计算机可读存储介质传输,例如,所述计算机指令可以从一个网站站点、计算机、服务器或数据中心通过有线(例如同轴电缆、光纤、数字用户线)或无线(例如红外、无线、微波等)方式向另一个网站站点、计算机、服务器或数据中心进行传输。所述计算机可读存储介质可以是计算机能够存取的任何可用介质或者是包含一个或多个可用介质集成的服务器、数据中心等数据存储设备。所述可用介质可以是磁性介质,(例如,软盘、硬盘、磁带)、光介质(例如dvd)、或者半导体介质(例如固态硬盘)等。

136.本领域普通技术人员可以理解实现上述实施例方法中的全部或部分流程,该流程可以由计算机程序来指令相关的硬件完成,该程序可存储于计算机可读取存储介质中,该程序在执行时,可包括如上述各方法实施例的流程。而前述的存储介质包括:rom或随机存储记忆体ram、磁碟或者光盘等各种可存储程序代码的介质。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1