一种基于LDPC信道编码的码字反馈补偿抗干扰方法

一种基于ldpc信道编码的码字反馈补偿抗干扰方法

技术领域

1.本发明涉及一种基于ldpc信道编码的码字反馈补偿抗干扰方法,属于通信信号处理领域。

背景技术:

2.分集合并(diversity combing)作为一种常见的抗干扰技术,其基本原理是通过多个信道传输同一个发送信息的多个副本,接收机通过接收包含相同原始信息的多个副本提高正确还原出原始信息的概率。分集合并技术的关键在于接收端采用何种方式进行合并,不同的分集合并算法对于系统性能具有较大影响。在传统的跳频通信系统当中,常见的分集合并算法包括:最大似然(maximum likelihood,ml)合并、自适应增益控制(adaptive gain control,agc)合并、等增益控制(equal gain control,egc)合并、自归一化(self normalization,snorm)合并、截断线性(clipped linear,cl)、乘积(product,pd)合并等。上述分集合并算法对于信道边信息(side information,si)要求不同,完整信道边信息包括跳频频点是否受扰、干扰类型、受扰信号信噪比(signal-to-noise ratio,snr)和信干噪比(signal-to-jamming ratio,sjr)、信号能量。例如,ml合并作为最优分集合并算法依赖完整边信息包括信号、干扰和噪声功率;在次优合并算法中如agc合并算法中仅需要部分边信息包括干扰和噪声功率信息,部分次优合并算法则不需要边信息如cl合并和pd合并等。这类对于边信息无要求的合并算法只需要信号电平作为参考值即可完成合并过程。上述次优合并算法凭借其对于信息完整边信息的低依赖性以及较为简单的实现步骤得到广泛使用。

3.在通信信号处理领域,诸如:直接序列扩频(direct sequence spread spectrum)跳频(frequency hopping,fh)技术、信道编码(channel coding)、分集合并(diversity combing)、自适应天线(adaptive antenna)、交织(interleaving)等技术是目前主流的抗干扰技术。在众多信道编码码字中,特别的,ldpc(low density parity check,ldpc)码作为近年来性能优异的信道编码,凭借其接近香农极限的性能、良好的纠错检错能力、并行处理能力和结构简单的特点已被广泛应用于多种商业标准,如802.11、802.16、dvb-s2、ccsds和5g等。

4.为了获得更好的抗干扰能力和更大链路信噪比,信道编码、分集合并和跳频的复合通信体制被广泛采用。然而,在接收端上述次优合并算法实现所必须的信号电平或幅度信息在干扰复杂的恶劣传输信道下易受干扰影响产生畸变,进而影响分集合并过程,无法有效抑制干扰的影响。通过分集合并还原出的接收信息裹挟过多干扰影响,进而使得后续译码输出可靠性降低,系统整体误码率性能下降。

技术实现要素:

5.针对传统基于信道编码和分集合并的跳频通信体制中,次优合并算法无法抑制干扰影响,使得合并结果产生畸变,进而影响译码过程,降低系统整体误码率性能的问题。本

发明的主要目的是提供一种基于ldpc信道编码的码字反馈补偿抗干扰方法(codeword feedback compensation anti-jamming,cfc-aj),综合利用译码器输出的硬判决比特信息和接收信号中未受干扰比特来补偿接收信号的比特先验信息,并通过迭代反馈回路优化译码器输入,提升译码可靠性。

6.本发明的目的是通过下述技术方案实现的:

7.本发明公开的一种基于ldpc信道编码的码字反馈补偿抗干扰方法,在原有的跳频通信系统基础上,选取ldpc码作为信道编码码字方案;在接收端进行分集合并前,针对比特级别的符号,首先通过干扰检测确定受干扰比特的位置,将比特所携带的软信息擦除置零,有效提升系统抗干扰能力;其次,接收端通过相干合并还原出初始接收信号作为译码器输入,并将译码结果结合未受干扰比特信息进行置零比特的修正补偿反馈;最后,接收端通过迭代不断优化取值,使受干扰比特的初始后验概率信息得到合理补偿,替代原始相干合并结果作为译码器输入,提升译码可靠性。

8.本发明公开的一种基于ldpc信道编码的码字反馈补偿抗干扰(cfc-aj)方法,包括如下步骤:

9.步骤一、发端对原始信息序列进行ldpc信道编码、分集以及跳频处理。

10.长度为k个符号的原始信息序列x,与生成矩阵g相乘得到编码结果c=x

·

g,其中编码结果c的长度为n;编码结果c通过分集进行复制,得到分集集数为z,包含完全相同的原始信息序列的集合c

div

={c1,c2,

…

,cz},其中ci为集合中一组信息序列,1≤i≤z;通过多进制频移键控,信息序列集合c

div

调制为跳频信号集合f

div

={f1,f2,...,fz},其中fi为跳频信号集合中一串跳频信息序列,1≤i≤z。

11.步骤二、接收步骤一发送的信号,通过干扰检测,确定受干扰频点,经过解跳后确定受干扰比特位置,对其擦除置零以抑制干扰的影响。

12.以r

div

={r1,r2,...,rz}表示接收信号集合,其中ri为接收信号集合中的一串信息序列,1≤i≤z。tc表示未受干扰比特集合,t表示受干扰比特集合,e

div

={e1,e2,...,ez}表示经过擦除置零后的接收信号集合,其中ei表示擦除置零后信号集合中一串信息序列,1≤i≤z。则接收信号中各比特可表示为,

[0013][0014]

计算接收信号中未受干扰比特的后验概率信息绝对值,得到均值

[0015][0016]

步骤三、信号集合进行相干合并。

[0017]

对已经过干扰抑制后的接收信号集合e中,不同信号序列中相同位置的比特幅度信息相干合并,最终得到一串信息序列g=[g1,g2,...,gn],序列中各比特gj表示为

[0018][0019]

译码器采用最小和译码算法,因此该信息序列g中各比特的幅度信息代表其先验

概率软信息,充当译码器输入。

[0020]

步骤四、完成最小和译码过程。

[0021]

以信息序列g=[g1,g2,...,gn]中各比特的幅度信息作为译码器输入,译码器采用最小和译码算法,完成预设次数迭代的译码过程。译码器输出各比特的后验概率信息集合l

judge

以及译码判决结果d。译码判决结果d由后验概率信息判决得到,二者的关系如下:

[0022][0023]

其中,n代表l

judge

中第n个比特,1≤n≤n。完成所有迭代译码后,接收端提取所有变量节点后验概率消息l

judge

中的各比特的极性集合,表示为

[0024]

l

sign

=sign(l

judge

)

ꢀꢀꢀ

(5)

[0025]

步骤五、补偿干扰比特先验概率信息并反馈结果。

[0026]

依据步骤二中的均值q和步骤四中各比特极性集合l

sign

,接收端补偿受干扰比特所缺失的先验概率信息,得到新的修正过后的接收信号比特集合其中表示集合中一串经过修正过后的信息序列,1≤i≤z。上标v代表第v次补偿反馈迭代过程。

[0027]

具体补偿方式如下式所示,

[0028][0029]

其中,0<α<1,α为修正比例因子。由于受到干扰影响,接收信号所携带的先验概率信息无法为译码过程提供较高的可靠性,译码器的译码结果中各比特的极性判断并不是绝对正确的。因此,该模块在补偿过程中引入修正比例因子α,减缓干扰缺陷的影响,缓慢补偿受干扰比特的幅值信息,提升整体方法的可靠性。α的值通过蒙特卡洛模拟得到。

[0030]

将上述步骤中经过修正后的比特集合反馈到步骤二中,代替原有的接收信号集合e

div

。

[0031]

步骤六,补偿停止判断。

[0032]

重复步骤三到步骤五,在每一次补偿反馈前,该步骤计算判决结果d是否满足校验方程h

·dt

=0。在达到补偿迭代的最大次数之前,若校验方程成立时,接收端则被视为获得了有效码字,立即结束补偿反馈,并将本次迭代反馈中的译码判决结果d作为最终译码器输出y;否则,统计接收端各次反馈迭代中校验方程h

·dt

=0中成立的校验节点个数,记为集合i

check

={b1,b2,...,bv},其中,bk为第k次补偿反馈迭代中使校验方程成立的校验节点的个数,1≤k≤v。在完成全部补偿迭代后,接收端选取i

check

当中的最大值bk所对应的第k次译码判决结果d作为最终的译码器输出y。

[0033]

每次补偿迭代的修正结果都将使最终的译码判决结果逐渐精确,在给定修正版比例因子α和最大补偿迭代次数v条件下,得出最优解,提升译码可靠性。

[0034]

有益效果:

[0035]

1、本发明公开的一种基于ldpc信道编码的码字反馈补偿抗干扰(cfc-aj)方法,通过干扰检测和相干合并替代传统的次优合并算法还原接收信息,降低对于信道边信息的依

赖,降低系统实现复杂度;

[0036]

2、本发明公开的一种基于ldpc信道编码的码字反馈补偿抗干扰(cfc-aj)方法,接收端综合利用ldpc码良好的纠错检错能力和未受干扰影响的优良比特,修正擦除置零比特,并在接收端引入补偿反馈回路,通过迭代反馈不断优化补偿值,使受干扰比特的初始先验概率信息得到合理补偿,替代原始相干合并结果作为译码器输入,进一步提升译码可靠性。

附图说明

[0037]

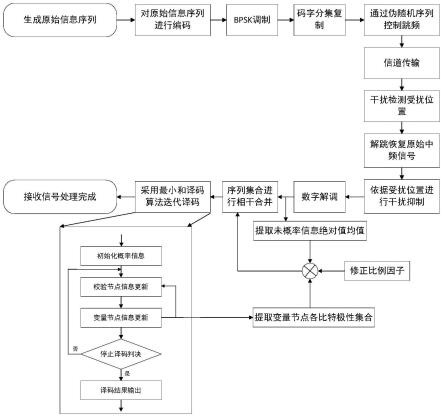

图1是本发明所述的一种基于ldpc信道编码的码字反馈补偿抗干扰(cfc-aj)方法流程示意图;

[0038]

图2是本发明所述的基于ldpc信道编码的码字反馈补偿抗干扰(cfc-aj)方法的系统结构框图;

[0039]

图3是本发明实施例所述的参考ccsds 131.1-0-1标准中(512,256)码型,基于ldpc信道编码的码字反馈补偿抗干扰(cfc-aj)方法与传统的基于ldpc信道编码的跳频抗干扰方法的ber性能曲线对比图。

具体实施方式

[0040]

下面将结合附图和实施例对本发明加以详细说明。同时也叙述了本发明技术方案解决的技术问题及有益效果,需要指出的是,所描述的实施例仅旨在便于对本发明的理解,而对其不起任何限定作用。

[0041]

为使本发明的目的、技术方案和优点更易理解,以下结合附图和具体实施方式对本发明进行进一步的详细说明。本实施例为针对美国深空通信ccsds 131.1-0-1标准中(512,256)ldpc码型的基于ldpc信道编码的码字反馈补偿抗干扰(cfc-aj)方法,本实施例中系统参数如下表所示:

[0042]

参数详情每帧符号数512码率1/2打孔方式校验位末128位调制方式bpsk信道模型混合信道(背景噪声+干扰)译码器最大迭代次数20分集集数2补偿反馈迭代次数10修正比例因子0.5

[0043]

如图2所示,本实施例还公开基于ldpc信道编码的码字反馈补偿抗干扰(cfc-aj)系统框图,用于实现基于ldpc信道编码的码字反馈补偿抗干扰(cfc-aj)方法。所述基于ldpc信道编码的码字反馈补偿抗干扰系统主要由编码模块、分集模块、跳频模块、干扰检测模块、解跳模块、合并模块、ldpc译码模块、补偿反馈模块、判决模块组成。编码模块、分集模块和跳频模块涉及步骤一,编码模块完成原始信息序列的ldpc信道编码过程,得到编码信

息,分集模块通过对发端原始信号进行分集重传和跳频处理,减小因信道非理想特性导致的信号损失,提升系统的干扰容限,跳频模块为系统带来更大的扩频增益和较强的抗干扰性能。干扰检测模块涉及步骤二,通过干扰检测获得实时的干扰信号的类型、能量和所在频段等信息,为后续干扰抑制奠定基础。解跳模块则是与发端的跳频模块相对应,将接收信号的载频还原到中频或者基带。合并模块涉及步骤三,将干扰抑制的接收信号进行等增益的相干合并,既使得各个比特所携带的自身幅度信息累加,增大先验概率,减小信道非理想特性的影响,又能够在一定程度上补偿因干扰抑制而损失的比特软信息,加速迭代译码的收敛速度。ldpc译码模块涉及步骤四,ldpc译码模块采用常见的最小和译码算法,提取合并模块中得到的比特序列幅值代表其初始先验概率大小作为译码器输入。译码器充分利用了ldpc信道编译码本身的纠错和检错能力,使得因干扰抑制而幅度置零的比特软信息由零值不断向其最优解接近,增强了系统的抗干扰性能。补偿反馈模块涉及步骤五,该模块综合ldpc译码器的纠错能力和原始接收信号中未受干扰比特所携带信息,为受干扰比特提供信息补偿,并且通过修正比例因子和迭代过程,降低干扰导致的可靠性不足的影响,逐步提升补偿信息的可靠性和准确性,确保缺失的比特信息趋向于判决出正确结果。

[0044]

如图1所示,本实施例中基于ldpc信道编码的码字反馈补偿抗干扰(cfc-aj)方法,具体实施步骤如下:

[0045]

步骤一、发送已通过ldpc信道编码、分集以及跳频处理后的信号。

[0046]

长度为256个符号的原始信息序列x,与生成矩阵g相乘得到编码结果c=x

·

g,经过打孔后,编码结果c的长度为512;编码结果c通过分集进行复制,得到包含2个完全相同的编码后信息序列的集合c

div

={c1,c2},其中c1,c2为两组完全相同的编码后信息序列;通过多进制频移键控,信息序列集合c

div

调制为跳频信号集合f

div

={f1,f2},其中f1,f2为完全相同的跳频信息序列。

[0047]

步骤二、接收步骤一发送的信号,通过干扰检测,确定受干扰频点,经过解跳后确定对应的受干扰比特位置,对其擦除置零以抑制干扰的影响。

[0048]

以r

div

={r1,r2}表示接收信号集合,其中r1,r2为接收信号集合中的信息序列。tc表示未受干扰比特集合,t表示受干扰比特集合,e

div

={e1,e2}表示经过擦除置零后的接收信号,其中e1,e2为接收信号集合中的信息序列。则接收信号中各比特可表示为,

[0049][0050]

计算接收信号中未受干扰比特的后验概率信息绝对值,得到均值

[0051][0052]

步骤三、信号集合进行相干合并。

[0053]

对已经过干扰抑制后的接收信号集合e中,不同信号序列中相同位置的比特幅度信息相干合并,最终得到一个信息序列g=[g1,g2],序列中各比特gj可以表示为

[0054]

[0055]

译码器采用最小和译码算法,因此信息序列g中各比特的幅度信息代表其后验概率软信息,充当译码器输入。

[0056]

步骤四、完成最小和译码过程。

[0057]

以信息序列g=[g1,g2,...,gn]中各比特的幅度信息作为译码器输入,译码器采用最小和译码算法,完成预设次数迭代的译码过程。译码器输出各比特的后验概率信息集合l

judge

以及译码判决结果d。译码判决结果d由后验概率信息判决得到,二者的关系如下:

[0058][0059]

其中,n代表l

judge

中第n个比特,1≤n≤512。完成所有迭代译码后,接收端提取所有变量节点后验概率消息l

judge

中的各比特的极性集合,表示为

[0060]

l

sign

=sign(l

judge

)

ꢀꢀꢀ

(11)

[0061]

步骤五,补偿干扰比特后验概率信息并反馈结果。

[0062]

提取步骤六的迭代译码结果中变量节点硬判决结果d的各比特极性,组成集合l

sign

,依据步骤二中的均值q,完成受干扰比特所缺失的后验概率信息的补偿,得到新的修正过后的接收信号比特集合其中是经过修正后的信息序列。上标v代表第v次补偿反馈迭代过程,最大次数为10次。

[0063]

具体补偿方式如下式所示,

[0064][0065]

由于接收信号受到干扰影响,其所携带的后验概率信息无法保证译码结果的准确性。因此,对迭代译码结果中的比特极性判断并不是绝对正确的。因此,通过引入修正比例因子,减缓干扰缺陷的影响,缓慢补偿反馈受干扰比特的幅值信息,提升整体方法的可靠性。

[0066]

将上述步骤得到的修正后的比特集合反馈到步骤二中,代替原有的接收信号集合e

div

。

[0067]

步骤六,补偿停止判断。

[0068]

重复步骤三到步骤五,在每一次补偿反馈前,接收端计算判决结果d是否满足校验方程h

·dt

=0。在达到补偿迭代的最大次数之前,若校验方程成立时,接收端则被视为获得了有效码字,立即结束补偿反馈,并将本次迭代反馈中的译码判决结果d作为最终译码器输出y;否则,统计接收端各次反馈迭代中校验方程h

·dt

=0中成立的校验节点个数,记为集合i

check

={b1,b2,...,b

10

},其中,bk为第k次补偿反馈迭代中使校验方程成立的校验节点的个数,1≤k≤10。在完成全部补偿迭代后,接收端选取i

check

当中的最大值bk所对应的第k次译码判决结果d作为最终的译码器输出y。

[0069]

图2虚线箭头代表迭代流程。随着迭代次数的增加,补偿反馈的比特软信息逐渐向正确初始先验概率信息的性能逐渐收敛。使用ber误码率作为衡量标准,为体现cfc-aj方法的性能优势,在传统的基于ldpc信道编码的跳频抗干扰方法基础上引入相同分集集数的分集合并处理,并且采用次优合并算法中的等增益合并算法,通过分析其性能作为对照。如图

3所示,不同的干扰比例系数p代表在信道传输过程当中,受干扰的频带范围占总体跳频频谱范围的比例。从图中可以看出,引入基于ldpc信道编码的码字反馈补偿抗干扰(cfc-aj)方法能够带来可观的系统性能提升。以10e-6作为误码率性能指标,在干扰比例系数p=0.1信道环境下,未结合分集合并的cfc-aj方法能够取得约1db的性能增益,并且该增益随着干扰比例和分集集数的增加而增加,系统的译码可靠性得到提升。同时,在干扰比例系数较大如p=0.3或者p=0.4的非理想信道环境下,系统在较低分集集数z=2条件下就能够有效应对干扰和信号衰弱的影响。

[0070]

以上所述的具体描述,对发明的目的、技术方案和有益效果进行进一步详细说明,所应理解的是,以上所述仅为本发明的具体实施例而已,并不用于限定本发明的保护范围,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1