一种FPGA折叠相关器结构及控制方法与流程

一种fpga折叠相关器结构及控制方法

技术领域

1.本公开一般涉及通信领域,具体涉及一种fpga折叠相关器结构及控制方法。

背景技术:

2.相关器是通信系统中一种常见的结构,广泛应用于对扩频信号的解扩处理和对数字信号的检测。相关器利用设备接收到的输入数据与伪码做相关运算,依靠伪码优异的自相关特性,从相关输出中判别相关峰值。

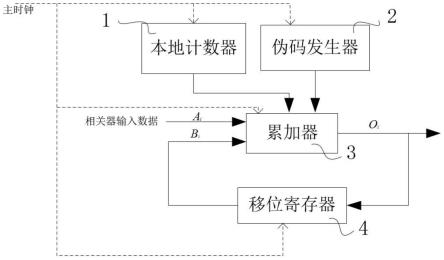

3.现有技术中的fpga相关器实现结构见图2,如图中所示,伪码长度越长,使用的累加器和移位寄存器的数量越多,硬件资源消耗越大。

技术实现要素:

4.鉴于现有技术中的上述缺陷或不足,期望提供可解决上述技术问题的一种fpga折叠相关器结构及控制方法。

5.本技术第一方面提供一种fpga折叠相关器结构,包括:

6.伪码发生器,所述伪码发生器用于周期性输出伪码序列,所述伪码序列包括n个伪码pn;所述伪码发生器每个主时钟频率f输出一个伪码pn;

7.累加器,所述累加器具有第一输入端、第二输入端、计数输入端、伪码输入端以及累加输出端;所述第一输入端用于输入相关器输入数据ai,所述相关器输入数据ai的数据速率为v;所述第二输入端用于输入移位数据bi;所述伪码输入端与所述伪码发生器的输出端连接;所述累加输出端用于输出累加数据oi;n=f/v;

8.本地计数器,所述本地计数器与所述累加器的计数输入端连接,用于输出计数值c,所述计数值c的取值为0~n-1,且当切换所述相关器输入数据ai时,所述计数值c清零;

9.移位寄存器,所述移位寄存器的输入端与所述累加输出端连接,所述移位寄存器的输出端与所述第二输入端连接;

10.其中,所述移位寄存器配置用于:

11.存储寄存序列,所述寄存序列的长度为d=n+1,初始值为0;

12.将所述寄存序列首位数据作为所述移位数据bi输出至所述累加器中;

13.对所述寄存序列进行移位操作;

14.将所述累加数据oi存储至所述寄存序列末位;

15.其中,所述累加器配置用于:

16.接收所述相关器输入数据ai、移位数据bi、伪码pn以及计数值c;

17.判断计数值c=0且所述伪码pn=1,输出oi=0+ai;

18.判断计数值c=0且所述伪码pn=-1,输出oi=0-ai;

19.判断计数值c≠0且所述伪码pn=1,输出oi=bi+ai;

20.判断计数值c≠0且所述伪码pn=-1,输出oi=b

i-ai。

21.根据本技术实施例提供的技术方案,所述伪码发生器用于输入原始伪码序列,所

述伪码发生器具体配置用于:接收设定伪码序列,周期性输出所述设定伪码序列;

22.所述设定伪码序列的获取方式通过以下步骤得到:

23.接收原始伪码序列;

24.判断所述原始伪码序列的伪码个数等于n,所述原始伪码序列作为所述设定伪码序列周期性输出。

25.根据本技术实施例提供的技术方案,所述设定伪码序列的获取方式还包括:

26.判断所述原始伪码序列的伪码个数小于n,在所述原始伪码序列后补0,得到伪码序列,所述伪码序列的伪码个数等于n,所述伪码序列作为所述设定伪码序列周期性输出;

27.其中,所述累加器(3)还配置用于:

28.判断计数值c≠0且所述伪码pn=0,输出oi=bi。

29.根据本技术实施例提供的技术方案,所述累加输出端连接有比较器,所述比较器用于比较所述累加数据oi,获取所述累加数据oi中的最大值。

30.本技术第二方面提供一种fpga折叠相关器控制方法,采用如上述所述的一种fpga折叠相关器结构,所述fpga折叠相关器控制方法包括如下步骤:

31.将所述寄存序列首位数据作为所述移位数据bi接收;

32.所述寄存序列进行移位操作;

33.接收所述相关器输入数据ai、伪码pn以及计数值c;

34.判断计数值c=0且所述伪码pn=1,输出oi=0+ai;

35.判断计数值c=0且所述伪码pn=-1,输出oi=0-ai;

36.判断计数值c≠0且所述伪码pn=1,输出oi=bi+ai;

37.判断计数值c≠0且所述伪码pn=-1,输出oi=b

i-ai;

38.将所述累加数据oi存储至所述寄存序列末位。

39.根据本技术实施例提供的技术方案,所述设定伪码序列的获取方式通过以下步骤得到:

40.接收原始伪码序列;

41.判断所述原始伪码序列的伪码个数等于n,所述原始伪码序列作为所述设定伪码序列周期性输出。

42.根据本技术实施例提供的技术方案,所述设定伪码序列的获取方式还包括:

43.判断所述原始伪码序列的伪码个数小于n,在所述原始伪码序列后补0,得到伪码序列,所述伪码序列的伪码个数等于n,所述伪码序列作为所述设定伪码序列周期性输出;

44.所述fpga折叠相关器控制方法还包括:

45.判断计数值c≠0且所述伪码pn=0,输出oi=bi。

46.本技术的有益效果在于:基于本技术提出的技术方案,包括本地计数器、伪码发生器、累加器和移位寄存器,使用时,所述移位寄存器内初始存储长度为d的寄存序列,所述寄存序列的初始值为0,将所述寄存序列的首位数据作为所述移位数据bi输出至所述累加器中,同时,所述伪码发生器每个主时钟频率输出一个伪码pn,所述累加器接收所述相关器输入数据ai、移位数据bi、伪码pn以及计数值c,根据所述计数值c和伪码pn的数值,进行相应运算并输出所述累加数据oi,且所述累加数据oi存储至所述寄存序列末位;通过上述结构使得,所述累加器和所述移位寄存器各使用一个重复进行折叠运算,在不损失性能的前提下

大大降低了硬件资源的消耗。

附图说明

47.通过阅读参照以下附图所作的对非限制性实施例所作的详细描述,本技术的其它特征、目的和优点将会变得更明显:

48.图1是本技术中的一种fpga折叠相关器结构的示意图;

49.图2是本技术中的一种常规fpga相关器结构的示意图;

50.图3是本技术中原始伪码序列中伪码个数等于n的计算过程;

51.图4是本技术中原始伪码序列中伪码个数小于n的计算过程;

52.图5是本技术中的一种fpga折叠相关器与常规fpga相关器资源对比图。

53.图中:1、本地计数器;2、伪码发生器;3、累加器;4、移位寄存器。

具体实施方式

54.下面结合附图和实施例对本技术作进一步的详细说明。可以理解的是,此处所描述的具体实施例仅仅用于解释相关发明,而非对该发明的限定。另外还需要说明的是,为了便于描述,附图中仅示出了与发明相关的部分。

55.需要说明的是,在不冲突的情况下,本技术中的实施例及实施例中的特征可以相互组合。下面将参考附图并结合实施例来详细说明本技术。

56.实施例1

57.请参考图1-图5为本技术提供的一种fpga折叠相关器结构的结构示意图,包括:

58.伪码发生器2,所述伪码发生器2用于周期性输出伪码序列,所述伪码序列包括n个伪码pn;所述伪码发生器2每个主时钟频率f输出一个伪码pn;

59.累加器3,所述累加器3具有第一输入端、第二输入端、计数输入端、伪码输入端以及累加输出端;所述第一输入端用于输入相关器输入数据ai,所述相关器输入数据ai的数据速率为v;所述第二输入端用于输入移位数据bi;所述伪码输入端与所述伪码发生器2的输出端连接;所述累加输出端用于输出累加数据oi;n=f/v;

60.本地计数器1,所述本地计数器1与所述累加器3的计数输入端连接,用于输出计数值c,所述计数值c的取值为0~n-1,且当切换所述相关器输入数据ai时,所述计数值c清零;

61.移位寄存器4,所述移位寄存器4的输入端与所述累加输出端连接,所述移位寄存器4的输出端与所述第二输入端连接;

62.其中,所述移位寄存器4配置用于:

63.存储寄存序列,所述寄存序列的长度为d=n+1,初始值为0;

64.将所述寄存序列首位数据作为所述移位数据bi输出至所述累加器3中;

65.对所述寄存序列进行移位操作;

66.将所述累加数据oi存储至所述寄存序列末位;

67.其中,所述累加器3配置用于:

68.接收所述相关器输入数据ai、移位数据bi、伪码pn以及计数值c;

69.判断计数值c=0且所述伪码pn=1,输出oi=0+ai;

70.判断计数值c=0且所述伪码pn=-1,输出oi=0-ai;

71.判断计数值c≠0且所述伪码pn=1,输出oi=bi+ai;

72.判断计数值c≠0且所述伪码pn=-1,输出oi=b

i-ai。

73.具体的,所述计数值c的取值为0~n-1;

74.具体的,所述伪码发生器输入原始伪码序列,在主时钟的控制下周期性输出设定伪码序列;

75.在一些实施例中,所述伪码发生器、本地计数器、累加器、移位寄存器均在主时钟的控制下串行顺序输出进行运算;

76.工作原理:使用时,所述移位寄存器4内初始存储长度为d的寄存序列,所述寄存序列的初始值为0,将所述寄存序列的首位数据作为所述移位数据bi输出至所述累加器中,同时,所述伪码发生器2每个主时钟频率输出一个伪码pn,所述累加器3接收所述相关器输入数据ai、移位数据bi、伪码pn以及计数值c,根据所述计数值c和伪码pn的数值,进行相应运算并输出所述累加数据oi,且所述累加数据oi存储至所述寄存序列末位;通过上述结构使得,如图1、图2、图5所示,本技术内所述累加器3和所述移位寄存器4各使用一个并重复进行折叠运算,在不损失性能的前提下大大降低了硬件资源的消耗。

77.在某些实施方式中,所述伪码发生器2具体配置用于:接收设定伪码序列,周期性输出所述设定伪码序列;

78.所述设定伪码序列的获取方式通过以下步骤得到:

79.接收原始伪码序列;

80.判断所述原始伪码序列的伪码个数等于n,所述原始伪码序列作为所述设定伪码序列周期性输出。

81.在一些实施例中,所述原始伪码序列包括n个伪码pn,如图3所示,所述原始伪码序列为[-1,1,-1,-1],所述相关器输入数据ai=[-1,-1,1,-1,-1,1,1],n=4,d=n+1=5,c=[0,1,2,3];具体计算过程如下:

[0082]

累加器内输入的相关器输入数据ai=-1、移位数据bi=0,此时所述计数值c=0且所述伪码pn=-1,因此输出oi=0-ai=1;

[0083]

累加器内输入的相关器输入数据ai=-1、移位数据bi=0,此时所述计数值c=1且所述伪码pn=1,因此输出oi=bi+ai=-1;

[0084]

累加器内输入的相关器输入数据ai=-1、移位数据bi=0,此时所述计数值c=2且所述伪码pn=-1,因此输出oi=b

i-ai=1;

[0085]

累加器内输入的相关器输入数据ai=-1、移位数据bi=0,此时所述计数值c=3且所述伪码pn=-1,因此输出oi=b

i-ai=1;

[0086]

切换为下一个相关器输入数据ai,所述计数值c清零;

[0087]

累加器内输入的相关器输入数据ai=-1、移位数据bi=0,此时所述计数值c=0且所述伪码pn=-1,因此输出oi=0-ai=1;

[0088]

累加器内输入的相关器输入数据ai=-1、移位数据bi=1,此时所述计数值c=1且所述伪码pn=1,因此输出oi=bi+ai=0;

[0089]

累加器内输入的相关器输入数据ai=-1、移位数据bi=-1,此时所述计数值c=2且所述伪码pn=-1,因此输出oi=b

i-ai=0;

[0090]

累加器内输入的相关器输入数据ai=-1、移位数据bi=1,此时所述计数值c=3且

所述伪码pn=-1,因此输出oi=b

i-ai=2;

[0091]

切换为下一个相关器输入数据ai,所述计数值c清零;

[0092]

累加器内输入的相关器输入数据ai=1、移位数据bi=1,此时所述计数值c=0且所述伪码pn=-1,因此输出oi=0-ai=-1;

[0093]

累加器内输入的相关器输入数据ai=1、移位数据bi=1,此时所述计数值c=1且所述伪码pn=1,因此输出oi=bi+ai=2;

[0094]

累加器内输入的相关器输入数据ai=1、移位数据bi=0,此时所述计数值c=2且所述伪码pn=-1,因此输出oi=b

i-ai=-1;

[0095]

累加器内输入的相关器输入数据ai=1、移位数据bi=0,此时所述计数值c=3且所述伪码pn=-1,因此输出oi=b

i-ai=-1;

[0096]

此时切换为下一个相关器输入数据ai,所述计数值c清零;

[0097]

累加器内输入的相关器输入数据ai=-1、移位数据bi=2,此时所述计数值c=0且所述伪码pn=-1,因此输出oi=0-ai=1;

[0098]

累加器内输入的相关器输入数据ai=-1、移位数据bi=-1,此时所述计数值c=1且所述伪码pn=1,因此输出oi=bi+ai=-2;

[0099]

累加器内输入的相关器输入数据ai=-1、移位数据bi=2,此时所述计数值c=2且所述伪码pn=-1,因此输出oi=b

i-ai=3;

[0100]

累加器内输入的相关器输入数据ai=-1、移位数据bi=-1,此时所述计数值c=3且所述伪码pn=-1,因此输出oi=b

i-ai=0;

[0101]

此时切换为下一个相关器输入数据ai,所述计数值c清零;

[0102]

累加器内输入的相关器输入数据ai=-1、移位数据bi=-1,此时所述计数值c=0且所述伪码pn=-1,因此输出oi=0-ai=1;

[0103]

累加器内输入的相关器输入数据ai=-1、移位数据bi=1,此时所述计数值c=1且所述伪码pn=1,因此输出oi=bi+ai=0;

[0104]

累加器内输入的相关器输入数据ai=-1、移位数据bi=-2,此时所述计数值c=2且所述伪码pn=-1,因此输出oi=b

i-ai=-1;

[0105]

累加器内输入的相关器输入数据ai=-1、移位数据bi=3,此时所述计数值c=3且所述伪码pn=-1,因此输出oi=b

i-ai=4;

[0106]

切换为下一个相关器输入数据ai,所述计数值c清零;

[0107]

累加器内输入的相关器输入数据ai=1、移位数据bi=0,此时所述计数值c=0且所述伪码pn=-1,因此输出oi=0-ai=-1;

[0108]

累加器内输入的相关器输入数据ai=1、移位数据bi=1,此时所述计数值c=1且所述伪码pn=1,因此输出oi=bi+ai=2;

[0109]

累加器内输入的相关器输入数据ai=1、移位数据bi=0,此时所述计数值c=2且所述伪码pn=-1,因此输出oi=b

i-ai=-1;

[0110]

累加器内输入的相关器输入数据ai=1、移位数据bi=-1,此时所述计数值c=3且所述伪码pn=-1,因此输出oi=b

i-ai=-2;

[0111]

切换为下一个相关器输入数据ai,所述计数值c清零;

[0112]

累加器内输入的相关器输入数据ai=1、移位数据bi=4,此时所述计数值c=0且所

述伪码pn=-1,因此输出oi=0-ai=-1;

[0113]

累加器内输入的相关器输入数据ai=1、移位数据bi=-1,此时所述计数值c=1且所述伪码pn=1,因此输出oi=bi+ai=0;

[0114]

累加器内输入的相关器输入数据ai=1、移位数据bi=2,此时所述计数值c=2且所述伪码pn=-1,因此输出oi=b

i-ai=1;

[0115]

累加器内输入的相关器输入数据ai=1、移位数据bi=-1,此时所述计数值c=3且所述伪码pn=-1,因此输出oi=b

i-ai=-2。

[0116]

在某些实施方式中,所述原始伪码序列内包括的伪码个数小于n个时,所述设定伪码序列的获取方式还包括:

[0117]

判断所述原始伪码序列的伪码个数小于n,在所述原始伪码序列后补0,得到伪码序列,所述伪码序列的伪码个数等于n,所述伪码序列作为所述设定伪码序列周期性输出;

[0118]

其中,所述累加器3还配置用于:

[0119]

判断计数值c≠0且所述伪码pn=0,输出oi=bi。

[0120]

在一些实施例中,所述原始伪码序列内包括的伪码个数小于n个,在伪码发生器内输入所述原始伪码序列时,将所述原始伪码序列后补0,使所述原始伪码序列的伪码个数等于n,补0后的原始伪码序列作为所述设定伪码序列周期性输出;如图4所示,所述原始伪码序列为[-1,1,-1],所述相关器输入数据ai=[-1,-1,1,-1,-1,1,1],n=4,d=n+1=5,c=[0,1,2,3];将所述原始伪码序列后补0变为[-1,1,-1,0];具体的计算过程如下:

[0121]

累加器内输入的相关器输入数据ai=-1、移位数据bi=0,此时所述计数值c=0且所述伪码pn=-1,因此输出oi=0-ai=1;

[0122]

累加器内输入的相关器输入数据ai=-1、移位数据bi=0,此时所述计数值c=1且所述伪码pn=1,因此输出oi=bi+ai=-1;

[0123]

累加器内输入的相关器输入数据ai=-1、移位数据bi=0,此时所述计数值c=2且所述伪码pn=-1,因此输出oi=b

i-ai=1;

[0124]

累加器内输入的相关器输入数据ai=-1、移位数据bi=0,此时所述计数值c=3且所述伪码pn=0,因此输出oi=bi=0;

[0125]

切换为下一个相关器输入数据ai,所述计数值c清零;

[0126]

累加器内输入的相关器输入数据ai=-1、移位数据bi=0,此时所述计数值c=0且所述伪码pn=-1,因此输出oi=0-ai=1;

[0127]

累加器内输入的相关器输入数据ai=-1、移位数据bi=1,此时所述计数值c=1且所述伪码pn=1,因此输出oi=bi+ai=0;

[0128]

累加器内输入的相关器输入数据ai=-1、移位数据bi=-1,此时所述计数值c=2且所述伪码pn=-1,因此输出oi=b

i-ai=0;

[0129]

累加器内输入的相关器输入数据ai=-1、移位数据bi=1,此时所述计数值c=3且所述伪码pn=0,因此输出oi=bi=1;

[0130]

切换为下一个相关器输入数据ai,所述计数值c清零;

[0131]

累加器内输入的相关器输入数据ai=1、移位数据bi=0,此时所述计数值c=0且所述伪码pn=-1,因此输出oi=0-ai=-1;

[0132]

累加器内输入的相关器输入数据ai=1、移位数据bi=1,此时所述计数值c=1且所

述伪码pn=1,因此输出oi=bi+ai=2;

[0133]

累加器内输入的相关器输入数据ai=1、移位数据bi=0,此时所述计数值c=2且所述伪码pn=-1,因此输出oi=b

i-ai=-1;

[0134]

累加器内输入的相关器输入数据ai=1、移位数据bi=0,此时所述计数值c=3且所述伪码pn=0,因此输出oi=bi=0;

[0135]

此时切换为下一个相关器输入数据ai,所述计数值c清零;

[0136]

累加器内输入的相关器输入数据ai=-1、移位数据bi=1,此时所述计数值c=0且所述伪码pn=-1,因此输出oi=0-ai=1;

[0137]

累加器内输入的相关器输入数据ai=-1、移位数据bi=-1,此时所述计数值c=1且所述伪码pn=1,因此输出oi=bi+ai=-2;

[0138]

累加器内输入的相关器输入数据ai=-1、移位数据bi=2,此时所述计数值c=2且所述伪码pn=-1,因此输出oi=b

i-ai=3;

[0139]

累加器内输入的相关器输入数据ai=-1、移位数据bi=-1,此时所述计数值c=3且所述伪码pn=0,因此输出oi=bi=-1;

[0140]

此时切换为下一个相关器输入数据ai,所述计数值c清零;

[0141]

累加器内输入的相关器输入数据ai=-1、移位数据bi=0,此时所述计数值c=0且所述伪码pn=-1,因此输出oi=0-ai=1;

[0142]

累加器内输入的相关器输入数据ai=-1、移位数据bi=1,此时所述计数值c=1且所述伪码pn=1,因此输出oi=bi+ai=0;

[0143]

累加器内输入的相关器输入数据ai=-1、移位数据bi=-2,此时所述计数值c=2且所述伪码pn=-1,因此输出oi=b

i-ai=-1;

[0144]

累加器内输入的相关器输入数据ai=-1、移位数据bi=3,此时所述计数值c=3且所述伪码pn=0,因此输出oi=bi=3;

[0145]

切换为下一个相关器输入数据ai,所述计数值c清零;

[0146]

累加器内输入的相关器输入数据ai=1、移位数据bi=-1,此时所述计数值c=0且所述伪码pn=-1,因此输出oi=0-ai=-1;

[0147]

累加器内输入的相关器输入数据ai=1、移位数据bi=1,此时所述计数值c=1且所述伪码pn=1,因此输出oi=bi+ai=2;

[0148]

累加器内输入的相关器输入数据ai=1、移位数据bi=0,此时所述计数值c=2且所述伪码pn=-1,因此输出oi=b

i-ai=-1;

[0149]

累加器内输入的相关器输入数据ai=1、移位数据bi=-1,此时所述计数值c=3且所述伪码pn=0,因此输出oi=bi=-1;

[0150]

切换为下一个相关器输入数据ai,所述计数值c清零;

[0151]

累加器内输入的相关器输入数据ai=1、移位数据bi=3,此时所述计数值c=0且所述伪码pn=-1,因此输出oi=0-ai=-1;

[0152]

累加器内输入的相关器输入数据ai=1、移位数据bi=-1,此时所述计数值c=1且所述伪码pn=1,因此输出oi=bi+ai=0;

[0153]

累加器内输入的相关器输入数据ai=1、移位数据bi=2,此时所述计数值c=2且所述伪码pn=-1,因此输出oi=b

i-ai=1;

[0154]

累加器内输入的相关器输入数据ai=1、移位数据bi=-1,此时所述计数值c=3且所述伪码pn=0,因此输出oi=bi=-1;

[0155]

在一些实施方式中,所述原始伪码序列包括的伪码个数大于n个,将所述原始伪码序列拆分成最少一个包括n个伪码的伪码序列和最多一个包括小于n个伪码的伪码序列,例如:所述原始伪码序列包括2n+4个伪码,所述伪码序列拆分为[pn(0),pn(1),

……

pn(n-1)],[pn(n),pn(n+1),

……

pn(2n-1)],[pn(2n),pn(2n+1),pn(2n+2),pn(2n+3)];然后依次将多个所述伪码序列作为所述设定伪码序列周期性输出,在所述累加器内内进行运算,输出所述累加数据oi,再将多次计算出的累加数据oi对应累加得到最终的累加数据oi。

[0156]

在某些实施方式中,所述累加输出端连接有比较器,所述比较器用于比较所述累加数据oi,获取所述累加数据oi中的最大值。

[0157]

具体的,所述累加器3的累加输出端连接有比较器,所述比较器用于比较所述累加数据oi,获取所述累加数据oi中的最大值,所述最大值为相关峰值。

[0158]

实施例2

[0159]

本技术提供的一种fpga折叠相关器控制方法,采用上述所述的一种fpga折叠相关器结构,所述fpga折叠相关器控制方法包括如下步骤

[0160]

将所述寄存序列首位数据作为所述移位数据bi接收;

[0161]

所述寄存序列进行移位操作;

[0162]

接收所述相关器输入数据ai、伪码pn以及计数值c;

[0163]

判断计数值c=0且所述伪码pn=1,输出oi=0+ai;

[0164]

判断计数值c=0且所述伪码pn=-1,输出oi=0-ai;

[0165]

判断计数值c≠0且所述伪码pn=1,输出oi=bi+ai;

[0166]

判断计数值c≠0且所述伪码pn=-1,输出oi=b

i-ai;

[0167]

将所述累加数据oi存储至所述寄存序列末位。

[0168]

在某些实施方式中,所述设定伪码序列的获取方式通过以下步骤得到:

[0169]

接收原始伪码序列;

[0170]

判断所述原始伪码序列的伪码个数等于n,所述原始伪码序列作为所述设定伪码序列周期性输出。

[0171]

在某些实施方式中,所述设定伪码序列的获取方式还包括:

[0172]

判断所述原始伪码序列的伪码个数小于n,在所述原始伪码序列后补0,得到伪码序列,所述伪码序列的伪码个数等于n,所述伪码序列作为所述设定伪码序列周期性输出;

[0173]

所述fpga折叠相关器控制方法还包括:

[0174]

判断计数值c≠0且所述伪码pn=0,输出oi=bi。

[0175]

以上描述仅为本技术的较佳实施例以及对所运用技术原理的说明。本领域技术人员应当理解,本技术中所涉及的发明范围,并不限于上述技术特征的特定组合而成的技术方案,同时也应涵盖在不脱离所述发明构思的情况下,由上述技术特征或其等同特征进行任意组合而形成的其它技术方案。例如上述特征与本技术中公开的(但不限于)具有类似功能的技术特征进行互相替换而形成的技术方案。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1