基于差动斜坡与TDC的两步式高速ADC电路

基于差动斜坡与tdc的两步式高速adc电路

技术领域

1.本发明属于模拟数字转换技术领域,涉及一种基于差动斜坡与tdc的两步式高速adc电路。

背景技术:

2.传统的两步式单斜模数转换电路结构如附图1所示,包括多级比较器、开关电容电路、数字控制逻辑,像素信号vpix_sf作为多级比较器的输入之一,比较器的输出端接数字控制逻辑的输入端,数字控制逻辑的输出端接开关控制电路中开关sh的控制端,开关控制电路的输出端vc接多级比较器的输入正端,斜坡电压vr连接到开关电容控制电路的输入端。在上述的两步式单斜模拟数字转换器中,先进行粗量化,在开关电容控制电路中,控制开关sc和sh为导通状态,vr此时为粗斜坡电压,从0开始,步进到粗斜坡电压的满摆幅电压v

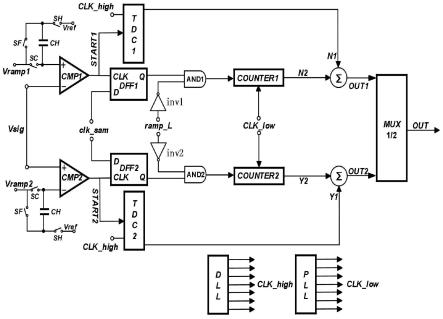

fs

,每一次的步进值为粗斜坡电压的一个台阶值δc。比较器对正端输入信号vc和负端输入信号vin进行比较,粗斜坡电压vr每步进增加δc,比较器便会比较一次,若经过m次步进,比较器的输出变为高电平,则表明输入信号在mδc《vin《(m+1)δc。这个粗量化区间内,就找到了vin所在的粗量化区间,此时关断开关sh,电容ch就存储了此时的粗斜坡电压值(m+1)δc,电容ch的上下极板电压差为(m+1)δc

–

vref,vref为一固定电平。粗斜坡电压vr步进到满摆幅电压v

fs

之后,开关sc关断,粗量化过程结束。

3.然后进行细量化操作,此时在开关电容电路中,开关sf为导通状态,vr此时为细斜坡电压,接到开关电容电路中电容ch的下极板,由于电容ch存储了之前的粗斜坡电压值(m+1)δc,则比较器的正输入端vc为vr+(m+1)δc,细斜坡电压vr从-δc步进变化到vref,每一次的步进值为细斜坡电压的一个台阶值δf。vc就从mδc变化到(m+1)δc,即对vin所在的粗量化区间进行细量化。比较器对正端输入信号vc和负端输入信号vin进行比较,若细斜坡电压vr经过n次步进,比较器的输出变为高电平,则表明输入信号在mδc+(n-1)δf《vin《mδc+nδf这个细量化区间内,一个完整的量化周期结束。

4.对于上述的两步式单斜模拟数字转换器,一次量化的时间为2m+2n。这种串行的结构思路有着较大的升级改动的空间,以进一步减少单次量化所需的时间,达到更高的速度,以满足高帧频cmos图像传感器的应用需求。

技术实现要素:

5.本发明的目的是提供一种基于差动斜坡与tdc的两步式高速adc电路,该电路通过差动形式的单斜式adc(analog-to-digital converter,adc,模数转换器)电路和tdc(time-to-digital converter,tdc,时间数字转换器)电路,在保证精度的前提下,实现了超高速的量化模式。

6.本发明所采用的技术方案是,基于差动斜坡与tdc的两步式高速adc电路,包括差动形式的单斜式adc电路,单斜式adc电路完成模拟-时间-数字的转换,单斜式adc电路中比较器的翻转信号作为时间数字转换tdc电路的start信号,同时在下一个时钟沿的到来作为

tdc的stop信号,单斜式adc电路的输出与tdc电路的输出通过累加器输出out1和out2,out1和out2通过二选一数据选择器mux 1/2判决出整体电路模数转换的结果out。

7.本发明的特点还在于:

8.差动形式的单斜式adc电路包括比较器cmp1和cmp2,比较器cmp1和cmp2负端均连接开关电容控制网络,比较器cmp1和cmp2的正端均连接vsig信号,比较器cmp1和cmp2的输出端start1和start2连接数字逻辑电路,start1和start2同时对应连接时间数字转换tdc1和tdc2电路。

9.开关电容控制网络包括开关sc,开关sc与开关sf的一端同时连接斜坡电压vramp1或vramp2,开关sc的另一端连接比较器cmp1或cmp2的负输入端以及电容ch的上级板;开关sf的另一端与开关sh连接电容ch的下极板;开关sh的另一端连接基准电压vref。

10.数字逻辑电路包括触发器dff1和dff2,触发器dff1和dff2的d端均接控制信号clk_sam,clk端对应与比较器cmp1和cmp2的输出端start1和start2连接;

11.还包括反相器inv1和inv2,inv1和inv2的输入端均接控制信号ramp_l,其输出端与触发器dff1和dff2的q端分别对应连接与门and1和and2的输入端,and1和and2的输出端对应连接接计数器counter1和counter2的输入端,计数器counter1和counter2的对应的输出n2与y2。

12.比较器cmp1和cmp2的输出端start1和start2对应连接了时间数字转换tdc1和tdc2电路,tdc1的输出结果n1、tdc2的输出结果y1,作为差分量化的低权重的模数转换结果。

13.本发明的有益效果是,本发明提供的基于差动斜坡与tdc的两步式高速adc电路,假设差动斜坡为mbit粗斜坡与nbit细斜坡组成,tdc为qbit,在保证总的量化精度为(m+n+q)bit的前提下,最终的实际量化时间仅为2

m-1

+2

n-1

,相较于上述传统两步式adc而言,可以完成更高速的量化,为高帧频大面阵的cmos图像传感器实现提供了有效的解决方案。

附图说明

14.图1为传统两步式单斜模数转换电路结构示意图;

15.图2为本发明基于差动斜坡与tdc的两步式高速adc电路的结构示意图;

16.图3为本发明基于差动斜坡与tdc的两步式高速adc电路的原理示意图;

17.图4为本发明基于差动斜坡与tdc的两步式高速adc电路的数字控制信号时序示意图。

具体实施方式

18.下面结合附图和具体实施方式对本发明进行详细说明。

19.本发明基于差动斜坡与tdc的两步式高速adc电路,如图2所示,包括差动形式的单斜式adc电路和时间数字转换tdc电路;单斜式adc完成模拟-时间-数字的转换,单斜式adc中比较器的翻转信号作为tdc的start信号,下一个时钟沿的到来作为tdc的stop信号,在单斜式adc量化的最后一个时钟周期,tdc配合adc完成更高精度的时间-数字的转换过程。

20.差动形式的单斜式adc电路包括比较器cmp1和cmp2,比较器cmp1和cmp2负端均连接开关电容控制网络,正端均连接vsig信号。比较器cmp1和cmp2的输出端start1和start2

连接数字逻辑电路,共同组成单斜式adc数字逻辑电路。同时对应连接时间数字转换tdc1和tdc2电路。

21.与比较器cmp1和cmp2的负端所接的开关电容控制网络,包括开关sc、sf和sh,还有电容ch。开关sc与sf的一端同时连接斜坡电压vramp1或vramp2,开关sc的另一端连接比较器cmp1或cmp2的负输入端以及电容ch的上级板;开关sf的另一端与开关sh连接电容ch的下极板;开关sh的另一端连接基准电压vref。值得注意的时,在差动形式的单斜式adc电路中,开关电容控制网络的工作时序保持一致并且电路结构完全对称。

22.数字逻辑电路包括触发器dff1和dff2,触发器dff1和dff2的d端均接控制信号clk_sam,clk端对应与比较器cmp1和cmp2的输出端start1和start2连接;

23.还包括反相器inv1和inv2,inv1和inv2的输入端均接控制信号ramp_l,其输出端与触发器dff1和dff2的q端分别对应连接与门and1和and2的输入端,and1和and2的输出端对应连接接计数器counter1和counter2的输入端,计数器counter1和counter2的对应的输出n2与y2为单斜式adc数字逻辑电路的高权重的模数转换结果,计数器所采用的时钟为低频时钟clk_low,由锁相环pll提供。与配合数字相关双采样的控制信号clk_sam和ramp_l。clk_sam接触发器dff1和dff2的d端,ramp_l接反相器inv1和inv2的输入端,ramp_h为计数器的复位端。

24.比较器cmp1和cmp2的输出端start1和start2对应连接了时间数字转换tdc1和tdc2电路。tdc1和tdc2所需要的时钟为多项延迟时钟,等效为高频时钟clk_high,由延迟锁相环dll来提供。tdc1的输出结果n1、tdc2的输出结果y1,作为差分量化的低权重的模数转换结果。

25.差动斜坡电路的输出作为高权重的模数转换结果n2和y2,时间数字转换tdc电路的输出n1和y1作为低权重的模数转换结果,分别对应通过累加器得到输出out1和out2,再通过二选一数据选择器mux判决出整体电路模数转换的结果out。

26.本发明将单斜式adc采用差分形式的斜坡量化,如图3所示:待量化信号vin在vramp1和vramp2中选择可以正常量化的粗斜坡,完成第一步mbit的粗量化过程,接下来vramp1和vramp2切换为差分形式的细斜坡,对通过两路比较器对vin进行更精确的nbit的细量化过程,采用粗细斜坡相结合的形式,再将主体的两步式量化结果再与qbit的tdc量化结果相结合,两路输出再通过数据选择器进行逻辑判决,得到最终的模数转换结果out。值得说明的是,该发明所采用的两步式包括差分形式的粗斜坡和细斜坡的两步式量化,以及差分量化与的时间数字转换技术相结合的两步式量化。

27.数字逻辑电路的数字控制信号时序示意图如图4所示:其工作周期分为共模信号转换和实际信号转换。vsig的共模信号的转换由斜坡信号中的小斜坡实现,值得说明的是,vin和vcm是包含在vsig中的实际量化信号和共模信号。实际信号的转换由斜坡信号的主斜坡实现。

28.图4中,输入信号vsig、斜坡信号vramp接入adc中。在开始量化前,ramp_h信号对计数器复位,配合初值端口将计数器复位并置初值。此后斜坡信号开始工作,三个信号被时序约束的情况下,比较器翻转2次,比较器逻辑电路整合成脉宽经由计数器完成量化。计数器counter1和counter2的对应的输出n2与y2为单斜式adc数字逻辑电路的高权重的模数转换结果。

29.比较器cmp1和cmp2的输出端start1和start2同时对应连接时间数字转换tdc1和tdc2电路。差动斜坡电路的输出作为高权重的模数转换结果n2和y2,时间数字转换tdc电路的输出n1和y1作为低权重的模数转换结果,分别对应通过累加器得到输出out1和out2,再通过二选一数据选择器mux判决出整体电路模数转换的结果out。

30.以12bit量化精度为例,对于传统两步式单斜模数转换电路而言,实际的最优量化时间为26+26,对于本发明而言,将12bit分为5bit粗量化、5bit细量化与2bit时间数字转换,实际的最优量化时间为24+23,可达到的速度增益为75%,值得说明的是,这种速度优势在越高精度的adc量化中越明显。

31.本发明将单斜式模数转换电路的量化时间消耗大大压缩,为高性能cmos图像传感器列级高速高精度量化提供了解决方案。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1