视频转码系统、方法、GPU以及电子设备和存储介质与流程

视频转码系统、方法、gpu以及电子设备和存储介质

技术领域

1.本公开涉及计算机技术领域,尤其涉及一种视频转码系统、方法、gpu以及电子设备和存储介质。

背景技术:

2.传统方法使用中央处理器(central processing unit,cpu)进行视频转码处理,会占用较多的cpu资源,特别是在图形类视频处理或者云游戏场景下,会影响计算性能。使用图形处理器(graphics processing unit,gpu)芯片中专用的视频转码计算单元进行视频转码处理,会相对节省计算资源,提高整体计算性能。因此越来越多的场景下使用gpu芯片中专用的视频转码计算单元进行大量的视频转码服务。相关技术中,利用cpu调度、高速串行计算机扩展总线标准(peripheral component interconnect express、pcie)控制数据传输的方法实现多个gpu芯片上的视频转码任务,控制过程复杂、转码效率较低,无法充分发挥多个gpu芯片的视频转码能力。

技术实现要素:

3.本公开提出了一种视频转码系统、方法、gpu以及电子设备和存储介质的技术方案。

4.根据本公开的一方面,提供了一种视频转码系统,所述系统包括:多个gpu,其中,所述多个gpu之间通过视频转码互连总线连接,所述多个gpu中包括一个主控gpu;所述主控gpu,用于在所述多个gpu之间进行视频转码任务的分配;所述多个gpu之间基于所述视频转码互连总线,对所述视频转码任务对应的转码处理数据进行传输。

5.在一种可能的实现方式中,所述主控gpu中包括:配置模块;所述配置模块,用于对所述多个gpu中执行所述视频转码任务对应的转码处理数据,进行内存地址信息的配置以及视频帧级别的同步。

6.在一种可能的实现方式中,针对任意一个gpu,基于所述配置模块配置的内存地址信息,利用所述视频转码互连总线从其它gpu的ddr内存中读取需要进行转码的转码处理数据。

7.在一种可能的实现方式中,所述主控gpu,还用于在所述多个gpu中的第一gpu的运行负载超过预设阈值的情况下,将所述第一gpu对应的处于未处理状态的视频转码任务,分配至所述多个gpu中的第二gpu,其中,所述第二gpu的运行负载未超过所述预设阈值。

8.在一种可能的实现方式中,所述视频转码任务包括下述至少一种:解码任务、渲染任务、视频处理任务、编码任务。

9.在一种可能的实现方式中,所述多个gpu位于一个电路板;或,所述多个gpu位于多个电路板。

10.根据本公开的一方面,提供了一种gpu,所述gpu包括主控gpu,所述主控gpu通过视频转码互连总线与从属gpu连接,所述主控gpu包括:任务分配模块,用于在所述主控gpu以

及所述从属gpu之间进行视频转码任务的分配;配置模块,用于对所述主控gpu以及所述从属gpu执行所述视频转码任务对应的转码处理数据,进行内存地址信息的配置以及视频帧级别的同步。

11.在一种可能的实现方式中,所述gpu还包括:转码模块,用于执行所述视频转码任务,以及将得到的转码处理数据存储在所述gpu的ddr内存中;所述主控gpu,还用于基于所述配置模块配置的内存地址信息以及视频帧级别的同步,通过所述视频转码互连总线,从每个所述gpu的ddr内存中读取对应的转码处理数据进行转码处理后,得到转码结果;数据传输模块,用于通过pcie总线或以太网,输出所述转码结果。

12.在一种可能的实现方式中,所述gpu还包括:转码模块,用于执行所述视频转码任务,以及将得到的转码处理数据存储在所述gpu的ddr内存中;每个所述gpu,分别对所述任务分配模块分配的所述视频转码任务处理完毕后,得到对应的转码结果;数据传输模块,用于通过pcie总线或以太网,输出每个所述gpu对应的所述转码结果。

13.根据本公开的一方面,提供了一种视频转码方法,所述方法应用于gpu,所述gpu包括主控gpu,所述主控gpu通过视频转码互连总线与从属gpu连接,所述方法包括:基于所述主控gpu,在所述主控gpu以及所述从属gpu之间进行视频转码任务的分配;基于所述主控gpu,对所述主控gpu以及所述从属gpu执行所述视频转码任务对应的转码处理数据,进行内存地址信息的配置以及视频帧级别的同步。

14.在一种可能的实现方式中,所述方法还包括:执行所述视频转码任务,以及将得到的转码处理数据存储在所述gpu的ddr内存中;基于配置的内存地址信息以及视频帧级别的同步,通过所述视频转码互连总线,从每个所述gpu的ddr内存中读取对应的转码处理数据进行转码处理后,得到转码结果;通过pcie总线或以太网,输出所述转码结果。

15.在一种可能的实现方式中,所述方法还包括:执行所述视频转码任务,以及将得到的转码处理数据存储在所述gpu的ddr内存中;每个所述gpu,分别对分配的所述视频转码任务处理完毕后,得到对应的转码结果;通过pcie总线或以太网,输出每个所述gpu对应的所述转码结果。

16.根据本公开的一方面,提供了一种电子设备,包括:处理器;用于存储处理器可执行指令的存储器;其中,所述处理器被配置为调用所述存储器存储的指令,以运行上述系统、或者运行上述gpu、或者执行上述方法。

17.根据本公开的一方面,提供了一种计算机可读存储介质,其上存储有计算机程序指令,所述计算机程序指令被处理器执行时运行上述系统、或者运行上述gpu、或者实现上述方法。

18.在本公开实施例中,视频转码系统包括多个gpu,多个gpu之间通过视频转码互连总线连接,通过多个gpu中的主控gpu,在多个gpu之间进行视频转码任务的分配,充分利用不同gpu的视频转码能力,各个gpu之间基于视频转码互连总线,对视频转码任务对应的转码处理数据进行高速传输,无需通过pcie总线进行不同gpu之间的数据传输,有效提高了数据传输速度,进而提高了视频转码系统的转码效率。

19.应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,而非限制本公开。根据下面参考附图对示例性实施例的详细说明,本公开的其它特征及方面将变得清楚。

附图说明

20.此处的附图被并入说明书中并构成本说明书的一部分,这些附图示出了符合本公开的实施例,并与说明书一起用于说明本公开的技术方案。

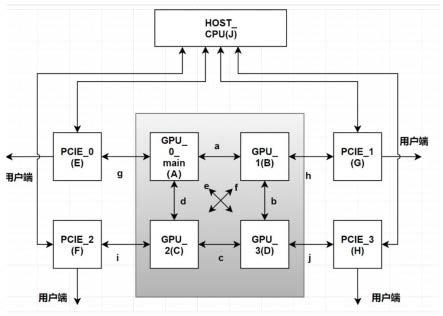

21.图1示出相关技术中的视频转码系统的示意图;

22.图2示出根据本公开实施例的视频转码系统的示意图;

23.图3示出根据本公开实施例的主控gpu的示意图;

24.图4示出根据本公开实施例的从属gpu的示意图;

25.图5示出根据本公开实施例的一种视频转码方法的流程图;

26.图6示出根据本公开实施例的一种电子设备的框图;

27.图7示出根据本公开实施例的一种电子设备的框图。

具体实施方式

28.以下将参考附图详细说明本公开的各种示例性实施例、特征和方面。附图中相同的附图标记表示功能相同或相似的元件。尽管在附图中示出了实施例的各种方面,但是除非特别指出,不必按比例绘制附图。

29.在这里专用的词“示例性”意为“用作例子、实施例或说明性”。这里作为“示例性”所说明的任何实施例不必解释为优于或好于其它实施例。

30.本文中术语“和/或”,仅仅是一种描述关联对象的关联关系,表示可以存在三种关系,例如,a和/或b,可以表示:单独存在a,同时存在a和b,单独存在b这三种情况。另外,本文中术语“至少一种”表示多种中的任意一种或多种中的至少两种的任意组合,例如,包括a、b、c中的至少一种,可以表示包括从a、b和c构成的集合中选择的任意一个或多个元素。

31.另外,为了更好地说明本公开,在下文的具体实施方式中给出了众多的具体细节。本领域技术人员应当理解,没有某些具体细节,本公开同样可以实施。在一些实例中,对于本领域技术人员熟知的方法、手段、元件和电路未作详细描述,以便于凸显本公开的主旨。

32.随着网络服务器端对视频转码需求的爆发式增长,gpu芯片中的视频转码计算能力越来越至关重要。特别是在多路视频同时进行转码服务的情况:例如一路原始视频码流经过解码处理后,再使用gpu进行分辨率缩放处理,最后编码成不同标准、不同分辨率的多个编码码流以适应服务器上的多用户需求,在此情况下解码与编码的计算比例为1:n;多路原始视频码流经过多路解码通道解码后,将多路数据合成一路进行编码的情况,解码与编码的计算比例为m:1;多路原始视频码流进行解码后,再编码成不同视频分辨率、不同视频格式的多路编码码流再传输到用户端的情况,解码与编码的计算比例为m:n。

33.由于gpu芯片的资源和面积的限制,只能在gpu芯片上设置固定算力的视频编解码计算单元。针对上述存在大量视频编解码任务的情况,相关技术中需要cpu进行复杂的任务调度分配和内存管理。

34.单个gpu芯片进行视频编解码处理计算的控制流程相对简单,但处理能力和数据带宽无法满足大量视频编解码任务实时处理的要求。

35.多个gpu芯片并行进行视频编解码处理计算时,相关技术中,需要cpu控制pcie总线,实现不同gpu芯片之间转码处理数据的传输和同步。但是,由于pcie受版本因素的影响,需要兼容更早版本的协议,导致在数据传输过程中需要路由、奇偶校验相关等较多负载信

息,使得视频转码过程中传输转码处理数据的有效率较低。

36.图1示出相关技术中的视频转码系统的示意图。如图1所示,4个gpu芯片之间通过pcie总线实现互相通信和数据传输。但是,在pcie总线传输转码处理数据时,需要把转码处理数据从一个gpu芯片的ddr内存传输到另一个gpu芯片的ddr内存之后,该芯片才可以对自身ddr内存中的转码处理数据进行转码处理,导致视频转码系统需要额外的数据存储空间,且占用总线带宽较大。当视频转码任务是复杂的编解码任务时,相关技术中采用pcie总线进行数据传输的方式无法高效完成多种编解码任务的处理。

37.为了在复杂视频转码场景下,高效完成多种视频编解码任务,本公开实施例提供了一种视频转码系统。下面对本公开实施例提供的视频转码系统进行详细描述。

38.图2示出根据本公开实施例的视频转码系统的示意图。图2所示,视频转码系统包括:多个gpu,其中,多个gpu之间通过视频转码互连总线连接,多个gpu中包括一个主控gpu;主控gpu,用于在多个gpu之间进行视频转码任务的分配;多个gpu之间基于视频转码互连总线,对视频转码任务对应的转码处理数据进行传输。

39.这里的视频转码互连总线是一种快速的串行传输的总线通信协议,具有高带宽、低延迟、低功耗的数据传输特性。基于视频转码互连总线,可以有效实现不同gpu芯片之间的数据互连,从而有效提高视频转码系统在复杂视频转码场景下的数据传输效率、视频转码效率。

40.根据本公开的实施例,视频转码系统包括多个gpu,多个gpu之间通过视频转码互连总线连接,通过多个gpu中的主控gpu,在多个gpu之间进行视频转码任务的分配,充分利用不同gpu的视频转码能力,各个gpu之间基于视频转码互连总线,对视频转码任务对应的转码处理数据进行高速传输,无需通过pcie总线进行不同gpu之间的数据传输,有效提高了数据传输速度,进而提高了视频转码系统的转码效率。

41.在一种可能的实现方式中,视频转码系统还包括:cpu;cpu,用于在多个gpu中配置主控gpu。

42.以上述图2为例,如图2所示,视频转码系统中包括:4个gpu:gpu_0(a)、gpu_1(b)、gpu_2(c)、gpu_3(d),以及1个cpu(j)。其中,cpu(j)可以配置gpu_0(a)为主控gpu,即gpu_0_main(a)。主控gpu以外的其它gpu均为从属gpu。

43.gpu_0(a)可以在4个gpu之间进行视频转码任务的分配。4个gpu之间基于视频转码互连总线a、b、c、d、e、f连接。基于视频转码互连总线a、b、c、d、e、f,可以实现4个gpu之间对视频转码任务对应的转码处理数据的互连和传输。

44.在一种可能的实现方式中,主控gpu中包括:配置模块;配置模块,用于对多个gpu中执行视频转码任务对应的转码处理数据,进行内存地址信息的配置以及视频帧级别的同步。

45.图3示出根据本公开实施例的主控gpu的示意图。如图3所示,主控gpu中包括:负责视频编码的视频转码单元a1(encoder_core(a1))、负责视频解码的视频转码单元a2(decoder_core(a2))、负责计算的gpu计算单元a3(gpu_core(a3))、负责数据存的ddr内存单元a5、以及配置模块a4。

46.在图3所示的主控gpu为图2所示的主控gpu_0(a)的情况下,基于主控gpu_0(a)中的配置模块a4,可以对图2所示的4个gpu:gpu_0(a)、gpu_1(b)、gpu_2(c)、gpu_3(d)中执行

视频转码任务对应的转码处理数据,进行内存地址信息的配置以及视频帧级别的同步。

47.在一种可能的实现方式中,针对任意一个gpu,基于配置模块配置的内存地址信息,利用视频转码互连总线从其它gpu的ddr内存中读取需要进行转码的转码处理数据。

48.主控gpu可以基于配置模块,将需要进行转码的转码处理数据的内存地址信息,配置给执行视频转码任务的从属gpu,以使得从属gpu可以获得该内存地址信息,并根据该内存地址信息直接从其它gpu的ddr内存中读取该转码处理数据,而无需先将该转码处理数据传输至自身的ddr内存中,从而有效实现了不同gpu之间ddr内存资源共享,充分利用了不同gpu上的内存资源,提高了内存资源的灵活应用,减少了系统带宽的压力。

49.其中,内存地址信息可以包括首地址信息和地址长度信息,或者,内存地址信息还可以根据实际情况设置为其它格式,本公开对此不作具体限定。

50.图4示出根据本公开实施例的从属gpu的示意图。如图4所示,从属gpu中包括:负责视频编码的视频转码单元b1(encoder_core(b1))、负责视频解码的视频转码单元b2(decoder_core(b2))、负责计算的gpu计算单元b3(gpu_core(b3))、负责数据存的ddr内存单元b4。图2所示从属gpu_1(b)、从属gpu_2(c)、从属gpu_3(d)均可以具有图4所示的结构,此处不作赘述。

51.以上述图2为例,需要进行转码的转码处理数据存储在从属gpu_1(b)的ddr内存中,主控gpu_0(a)将从属gpu_1(b)中存储该转码处理数据的内存地址信息,配置给需要执行视频转码任务的从属gpu_2(c),以使得从属gpu_2(c)可以基于从属gpu_2(c)与从属gpu_1(b)之间的视频转码互连总线f,直接访问从属gpu_1(b)的ddr内存中读取该转码处理数据进行处理。

52.在一种可能的实现方式中,视频转码任务包括:解码任务、渲染任务、视频处理任务、编码任务。

53.在复杂视频转码场景下,视频转码任务可以包括:解码任务、渲染任务(对解码后数据进行渲染处理)、视频处理任务(对解码后数据和/或渲染后数据进行视频处理)、编码任务。视频处理任务可以包括缩放、边缘增强、背景模糊、对比度调整、色彩增强等处理等,本公开对此不作具体限定。视频转码任务除了上述任务以外,还可以包括其它图形处理任务,本公开对此不作具体限定。

54.在一种可能的实现方式中,主控gpu,还用于在多个gpu中的第一gpu的运行负载超过预设阈值的情况下,将第一gpu对应的处于未处理状态的视频转码任务,分配至多个gpu中的第二gpu,其中,第二gpu的运行负载未超过预设阈值。

55.利用硬件调度的方式,可以充分利用不同gpu的转码计算能力,避免一个gpu上运行负载过大,其它gpu处于空载的情况,从而避免计算资源的浪费,提高了系统的转码效率。

56.其中,预设阈值的具体取值可以根据实际情况确定,本公开对此不作具体限定。

57.在一种可能的实现方式中,多个gpu位于一个电路板;或,多个gpu位于多个电路板。

58.下面对利用本公开提供的视频转码系统,在多种不同的视频转码场景下的具体转码过程进行详细描述。

59.第一种视频转码场景:对多路原始视频码流进行解码,并根据用户需求对解码后数据进行gpu计算处理后,再合成一路数据进行编码的场景。

60.首先,视频转码系统的cpu配置多个gpu中的主控gpu和从属gpu。

61.以上述图2为例,cpu(j)配置gpu_0(a)为主控gpu,即gpu_0_main(a)。gpu_1(b)、gpu_2(c)、gpu_3(d)均为从属gpu。

62.第二步,主控gpu执行对输入的原始视频码流进行解码处理,以及将解码后数据以视频帧为单位存储到自身的ddr内存中。从属gpu也执行对输入的原始视频码流进行解码处理,以及将解码后数据以视频帧为单位存储到自身的ddr内存中。

63.第三步,根据用户需求,主控gpu对解码后数据进行渲染和/或缩放等gpu计算处理。从属gpu也根据用户需求对相应的解码后数据进行渲染和/或缩放等gpu计算处理。

64.第四步,由于不同的gpu视频解码、渲染和/或缩放计算的速度不同,因此,主控gpu对所有gpu中的转码处理数据进行内存地址信息的配置以及视频帧级别的同步。

65.以上述图2为例,主控gpu:gpu_0_main(a)对从属gpu:gpu_1(b)、gpu_2(c)、gpu_3(d)进行内存地址信息的配置以及视频帧级别的同步。

66.例如,主控gpu把需要进行转码的转码处理数据的内存地址信息,配置给执行转码处理的从属gpu。其中,内存地址信息包括首地址信息和地址长度信息等。

67.基于主控gpu的配置,不同gpu可以互相访问,以获取到需要的转码处理数据。

68.第五步,所有gpu会同时进行视频帧级别的视频解码、渲染和/或缩放等gpu计算处理,并把转码结果以视频帧为单位,存储到自身的ddr内存中。

69.第六步,通过视频转码互联总线把存储在不同gpu的ddr内存中的转码处理数据传输给主控gpu,完成最后的合成编码。

70.以上述图2为例,4个gpu完成同步转码计算之后,从属gpu:gpu_1(b)、gpu_2(c)、gpu_3(d),通过与主控gpu:gpu_0_main(a)之间的视频转码互连总线a、e、d,将各自ddr内存中的转码处理数据传输到主控gpu:gpu_0_main(a)。

71.主控gpu:gpu_0_main(a)对汇总后的转码处理数据进行编码处理,得到最终的转码结果。

72.第七步,视频转码完成后,通过pcie总线把最终的转码结果传输给用户。

73.以上述图2为例,主控gpu:gpu_0_main(a)将最终的转码结果,基于pcie总线g,传输到用户端。

74.视频转码完成后,还可以通过以太网(ethernet)把最终的转码结果传输给用户,本公开对此不作具体限定。

75.第二种视频转码场景:对一路原始视频码流进行解码,并根据用户需求对解码后数据进行gpu计算处理后,再编码为多种视频格式、不同分辨率的码流的场景。

76.首先,视频转码系统的cpu配置多个gpu中的主控gpu和从属gpu。

77.以上述图2为例,cpu(j)配置gpu_0(a)为主控gpu,即gpu_0_main(a)。gpu_1(b)、gpu_2(c)、gpu_3(d)均为从属gpu。

78.第二步,主控gpu执行对输入的原始视频码流进行解码处理,以及将解码后数据以视频帧为单位存储到自身的ddr内存中。

79.以上述图2为例,主控gpu:gpu_0_main(a)对原始视频码流进行解码处理,以及将解码后数据存储到gpu_0_main(a)的ddr内存中。

80.第三步,由于不同的gpu视频解码、渲染和/或缩放计算的速度不同,因此,主控gpu

对所有gpu中的转码处理数据进行内存地址信息的配置以及视频帧级别的同步。

81.以上述图2为例,主控gpu:gpu_0_main(a)对从属gpu:gpu_1(b)、gpu_2(c)、gpu_3(d)进行内存地址信息的配置以及视频帧级别的同步。

82.例如,主控gpu把需要进行转码的转码处理数据的内存地址信息,配置给执行转码处理的从属gpu。其中,内存地址信息包括首地址信息和地址长度信息等。

83.基于主控gpu的配置,不同gpu可以互相访问,以获取到需要的转码处理数据。

84.第四步,主控gpu通过视频转码互联总线把解码数据传输给从属gpu,同时根据用户需求,主控gpu对解码后数据进行渲染或者缩放等gpu计算处理,从属gpu也对视频转码互联总线传输过来的视频数据进行渲染或者缩放等gpu计算处理。

85.第五步,所有执行转码任务的gpu分别对经过渲染或者缩放等gpu计算处理后的计算结果进行编码处理,根据不同用户的需求,编码成不同分辨率、视频格式的码流,得到各自的转码结果,最后通过pcie总线分别把转码结果传输给用户。

86.以上述图2为例,根据用户需求,主控gpu:gpu_0_main(a)从gpu_0_main(a)的ddr内存中读取解码后数据进行渲染和/或缩放等gpu计算,以及将计算结果存储到gpu_0_main(a)的ddr空间中,然后再从gpu_0_main(a)的ddr内存中读取计算结果进行视频编码。

87.由于主控gpu:gpu_0_main(a)对从属gpu:gpu_1(b)、gpu_2(c)、gpu_3(d)进行了内存地址信息的配置以及视频帧级别的同步,以使得gpu_1(b)、gpu_2(c)、gpu_3(d)可以从gpu_0_main(a)的ddr内存中获取到正确的转码处理数据。gpu_0_main(a)通过与gpu_1(b)、gpu_2(c)、gpu_3(d)之间的视频转码互联总线a、e、d,完成与gpu_1(b)、gpu_2(c)、gpu_3(d)的数据传输。

88.根据用户需求,gpu_1(b)、gpu_2(c)、gpu_3(d)对获取到的转码处理数据进行渲染、缩放变换等gpu计算,以及将计算结果存储到各自的ddr内存中。根据用户需求以及与gpu_0_main(a)之间的视频帧级别的同步信息,gpu_1(b)、gpu_2(c)、gpu_3(d)分别从各自的ddr内存中读取计算结果进行视频编码。

89.最后,gpu_0_main(a)、gpu_1(b)、gpu_2(c)、gpu_3(d)分别通过pcie总线g、h、i、j,传输到用户端。

90.视频转码完成后,还可以通过以太网(ethernet)把最终的转码结果传输给用户,本公开对此不作具体限定。

91.第三种视频转码场景:对多路原始视频码流进行解码,并根据用户需求对解码后数据进行gpu计算处理后,再编码为多种视频格式、不同分辨率的码流的场景。

92.首先,视频转码系统的cpu配置多个gpu中的主控gpu和从属gpu。

93.以上述图2为例,cpu(j)配置gpu_0(a)为主控gpu,即gpu_0_main(a)。gpu_1(b)、gpu_2(c)、gpu_3(d)均为从属gpu。

94.第二步,主控gpu执行对输入的原始视频码流进行解码处理,以及将解码后数据以视频帧为单位存储到自身的ddr内存中。从属gpu也执行对输入的原始视频码流进行解码处理,以及将解码后数据以视频帧为单位存储到到自身的ddr内存中。

95.第三步,根据用户需求,主控gpu对解码后数据进行渲染或者缩放等gpu计算处理。从属gpu也根据用户需求对相应的解码后数据进行渲染或者缩放等gpu计算处理。

96.第四步,由于不同的gpu视频解码、渲染和/或缩放计算的速度不同,因此,主控gpu

对所有gpu中的转码处理数据进行内存地址信息的配置以及视频帧级别的同步。

97.以上述图2为例,主控gpu:gpu_0_main(a)对从属gpu:gpu_1(b)、gpu_2(c)、gpu_3(d)进行内存地址信息的配置以及视频帧级别的同步。

98.例如,主控gpu把需要进行转码的转码处理数据的内存地址信息,配置给执行转码处理的从属gpu。其中,内存地址信息包括首地址信息和地址长度信息等。

99.基于主控gpu的配置,不同gpu可以互相访问,以获取到需要的转码处理数据。

100.第五步,当所有gpu完成一帧视频数据的视频解码、渲染或者缩放等gpu渲染计算后,把计算结果以视频帧为单位存储到各自的ddr内存中。

101.第六步,所有执行转码任务的gpu分别对经过渲染或者缩放等gpu计算处理的计算结果进行编码处理,根据不同用户的需求,编码成不同分辨率、视频格式的码流。

102.第七步,当有gpu处于视频转码任务空闲的状态,主控gpu会配置视频转码任务多的gpu通过视频转码互联总线传输转码处理数据给转码任务空闲的gpu。

103.在一示例中,主控gpu可以根据各gpu的运行负载,以及视频转码任务的当前状态,确定gpu是否处于转码任务空闲,以及是否处于负载较大,从而基于各gpu的实际负载情况,进行视频转码任务的调度。

104.以上述图2为例,在调度过程中,gpu_0_main(a)、gpu_1(b)、gpu_2(c)、gpu_3(d),通过视频转码互连总线a、b、c、d、e、f传输视频转码任务对应的转码处理数据。

105.第七步,所有gpu完成视频转码后,通过pcie总线把最终的转码结果传输给用户。

106.以上述图2为例,gpu_0_main(a)、gpu_1(b)、gpu_2(c)、gpu_3(d)分别通过pcie总线g、h、i、j,传输到用户端。

107.视频转码完成后,还可以通过以太网(ethernet)把最终的转码结果传输给用户,本公开对此不作具体限定。

108.本公开实施例提供的视频转码系统,使用视频转码互连总线,对不同gpu间的转码处理数据进行高效的传输,无需通过pcie总线进行芯片间数据传输,大大提高了视频转码系统的转码计算能力,也使得视频转码系统的实时性得到了提高。

109.本公开实施例提供的视频转码系统,通过主控gpu对所有从属gpu进行内存地址信息的配置以及视频帧级别的同步,通过主控gpu对从属gpu这种灵活的配置方式,可以实现不同gpu之间的ddr内存资源共享。此外,也可以实现需要进行转码处理的gpu可以互相访问对方的ddr内存,充分利用不同gpu上的内存资源,提高了视频转码系统内存的灵活应用,减少了系统带宽的压力。

110.本公开实施例还提供了一种gpu,gpu包括主控gpu,主控gpu通过视频转码互连总线与从属gpu连接,主控gpu包括:任务分配模块,用于在主控gpu以及从属gpu之间进行视频转码任务的分配;配置模块,用于对主控gpu以及从属gpu执行视频转码任务对应的转码处理数据,进行内存地址信息的配置以及视频帧级别的同步。

111.主控gpu以及从属gpu的具体结构,以及相互之间的连接关系可以参照上述相关描述,此处不作赘述。

112.在一种可能的实现方式中,gpu还包括:转码模块,用于执行视频转码任务,以及将得到的转码处理数据存储在gpu的ddr内存中;主控gpu,还用于基于配置模块配置的内存地址信息以及视频帧级别的同步,通过视频转码互连总线,从每个gpu的ddr内存中读取对应

的转码处理数据进行转码处理后,得到转码结果;数据传输模块,用于通过pcie总线或以太网,输出转码结果。

113.gpu执行上述转码任务的过程可以参照上述第一种视频转码场景的详细描述,此处不作赘述。

114.在一种可能的实现方式中,gpu还包括:转码模块,用于执行视频转码任务,以及将得到的转码处理数据存储在gpu的ddr内存中;每个gpu,分别对任务分配模块分配的视频转码任务处理完毕后,得到对应的转码结果;数据传输模块,用于通过pcie总线或以太网,输出每个gpu对应的转码结果。

115.gpu执行上述转码任务的过程可以参照上述第二、三种视频转码场景的详细描述,此处不作赘述。

116.图5示出根据本公开实施例的一种视频转码方法的流程图。该视频转码方法应用于gpu,gpu包括主控gpu,主控gpu通过视频转码互连总线与从属gpu连接。主控gpu以及从属gpu的具体结构,以及相互之间的连接关系可以参照上述相关描述,此处不作赘述。如图5所示,该视频转码方法包括:

117.在步骤s51中,基于主控gpu,在主控gpu以及从属gpu之间进行视频转码任务的分配;

118.在步骤s52中,基于主控gpu,对主控gpu以及从属gpu执行视频转码任务对应的转码处理数据,进行内存地址信息的配置以及视频帧级别的同步。

119.根据本公开实施例,基于主控gpu,在主控gpu以及与主控gpu通过视频转码互连总线连接的从属gpu之间进行视频转码任务的分配,充分利用不同gpu的视频转码能力,各个gpu之间基于视频转码互连总线,对视频转码任务对应的转码处理数据进行高速传输,无需通过pcie总线进行不同gpu之间的数据传输,有效提高了数据传输速度,进而提高了视频转码效率。

120.在一种可能的实现方式中,该视频转码方法还包括:执行视频转码任务,以及将得到的转码处理数据存储在gpu的ddr内存中;基于配置的内存地址信息以及视频帧级别的同步,通过视频转码互连总线,从每个gpu的ddr内存中读取对应的转码处理数据进行转码处理后,得到转码结果;通过pcie总线或以太网,输出转码结果。

121.gpu执行上述转码任务的过程可以参照上述第一种视频转码场景的详细描述,此处不作赘述。

122.在一种可能的实现方式中,该视频转码方法还包括:执行视频转码任务,以及将得到的转码处理数据存储在gpu的ddr内存中;每个gpu,分别对分配的视频转码任务处理完毕后,得到对应的转码结果;通过pcie总线或以太网,输出每个gpu对应的转码结果。

123.gpu执行上述转码任务的过程可以参照上述第二、三种视频转码场景的详细描述,此处不作赘述。

124.可以理解,本公开提及的上述各个方法实施例,在不违背原理逻辑的情况下,均可以彼此相互结合形成结合后的实施例,限于篇幅,本公开不再赘述。本领域技术人员可以理解,在具体实施方式的上述方法中,各步骤的具体执行顺序应当以其功能和可能的内在逻辑确定。

125.此外,本公开还提供了电子设备、计算机可读存储介质、程序,上述均可用来实现

本公开提供的任一种视频转码系统、方法以及gpu,相应技术方案和描述和参见方法部分的相应记载,不再赘述。

126.该方法与计算机系统的内部结构存在特定技术关联,且能够解决如何提升硬件运算效率或执行效果的技术问题(包括减少数据存储量、减少数据传输量、提高硬件处理速度等),从而获得符合自然规律的计算机系统内部性能改进的技术效果。

127.在一些实施例中,本公开实施例提供的装置具有的功能或包含的模块可以用于执行上文方法实施例描述的方法,其具体实现可以参照上文方法实施例的描述,为了简洁,这里不再赘述。

128.本公开实施例还提出一种计算机可读存储介质,其上存储有计算机程序指令,所述计算机程序指令被处理器执行时运行上述的系统、或者运行上述的gpu、或者实现上述方法。计算机可读存储介质可以是易失性或非易失性计算机可读存储介质。

129.本公开实施例还提出一种电子设备,包括:处理器;用于存储处理器可执行指令的存储器;其中,所述处理器被配置为调用所述存储器存储的指令,以运行上述的系统、或者运行上述的gpu、或者执行上述方法。

130.本公开实施例还提供了一种计算机程序产品,包括计算机可读代码,或者承载有计算机可读代码的非易失性计算机可读存储介质,当所述计算机可读代码在电子设备的处理器中运行时,所述电子设备中的处理器执行上述方法。

131.电子设备可以被提供为终端、服务器或其它形态的设备。

132.图6示出根据本公开实施例的一种电子设备的框图。参照图6,电子设备800可以是用户设备(user equipment,ue)、移动设备、用户终端、终端、蜂窝电话、无绳电话、个人数字处理(personal digital assistant,pda)、手持设备、计算设备、车载设备、可穿戴设备等终端设备。

133.参照图6,电子设备800可以包括以下一个或多个组件:处理组件802,存储器804,电源组件806,多媒体组件808,音频组件810,输入/输出(i/o)接口812,传感器组件814,以及通信组件816。

134.处理组件802通常控制电子设备800的整体操作,诸如与显示,电话呼叫,数据通信,相机操作和记录操作相关联的操作。处理组件802可以包括一个或多个处理器820来执行指令,以完成上述的方法的全部或部分步骤。此外,处理组件802可以包括一个或多个模块,便于处理组件802和其他组件之间的交互。例如,处理组件802可以包括多媒体模块,以方便多媒体组件808和处理组件802之间的交互。

135.存储器804被配置为存储各种类型的数据以支持在电子设备800的操作。这些数据的示例包括用于在电子设备800上操作的任何应用程序或方法的指令,联系人数据,电话簿数据,消息,图片,视频等。存储器804可以由任何类型的易失性或非易失性存储设备或者它们的组合实现,如静态随机存取存储器(sram),电可擦除可编程只读存储器(eeprom),可擦除可编程只读存储器(eprom),可编程只读存储器(prom),只读存储器(rom),磁存储器,快闪存储器,磁盘或光盘。

136.电源组件806为电子设备800的各种组件提供电力。电源组件806可以包括电源管理系统,一个或多个电源,及其他与为电子设备800生成、管理和分配电力相关联的组件。

137.多媒体组件808包括在所述电子设备800和用户之间的提供一个输出接口的屏幕。

在一些实施例中,屏幕可以包括液晶显示器(lcd)和触摸面板(tp)。如果屏幕包括触摸面板,屏幕可以被实现为触摸屏,以接收来自用户的输入信号。触摸面板包括一个或多个触摸传感器以感测触摸、滑动和触摸面板上的手势。所述触摸传感器可以不仅感测触摸或滑动动作的边界,而且还检测与所述触摸或滑动操作相关的持续时间和压力。在一些实施例中,多媒体组件808包括一个前置摄像头和/或后置摄像头。当电子设备800处于操作模式,如拍摄模式或视频模式时,前置摄像头和/或后置摄像头可以接收外部的多媒体数据。每个前置摄像头和后置摄像头可以是一个固定的光学透镜系统或具有焦距和光学变焦能力。

138.音频组件810被配置为输出和/或输入音频信号。例如,音频组件810包括一个麦克风(mic),当电子设备800处于操作模式,如呼叫模式、记录模式和语音识别模式时,麦克风被配置为接收外部音频信号。所接收的音频信号可以被进一步存储在存储器804或经由通信组件816发送。在一些实施例中,音频组件810还包括一个扬声器,用于输出音频信号。

139.i/o接口812为处理组件802和外围接口模块之间提供接口,上述外围接口模块可以是键盘,点击轮,按钮等。这些按钮可包括但不限于:主页按钮、音量按钮、启动按钮和锁定按钮。

140.传感器组件814包括一个或多个传感器,用于为电子设备800提供各个方面的状态评估。例如,传感器组件814可以检测到电子设备800的打开/关闭状态,组件的相对定位,例如所述组件为电子设备800的显示器和小键盘,传感器组件814还可以检测电子设备800或电子设备800一个组件的位置改变,用户与电子设备800接触的存在或不存在,电子设备800方位或加速/减速和电子设备800的温度变化。传感器组件814可以包括接近传感器,被配置用来在没有任何的物理接触时检测附近物体的存在。传感器组件814还可以包括光传感器,如互补金属氧化物半导体(cmos)或电荷耦合装置(ccd)图像传感器,用于在成像应用中使用。在一些实施例中,该传感器组件814还可以包括加速度传感器,陀螺仪传感器,磁传感器,压力传感器或温度传感器。

141.通信组件816被配置为便于电子设备800和其他设备之间有线或无线方式的通信。电子设备800可以接入基于通信标准的无线网络,如无线网络(wi-fi)、第二代移动通信技术(2g)、第三代移动通信技术(3g)、第四代移动通信技术(4g)、通用移动通信技术的长期演进(lte)、第五代移动通信技术(5g)或它们的组合。在一个示例性实施例中,通信组件816经由广播信道接收来自外部广播管理系统的广播信号或广播相关信息。在一个示例性实施例中,所述通信组件816还包括近场通信(nfc)模块,以促进短程通信。例如,在nfc模块可基于射频识别(rfid)技术,红外数据协会(irda)技术,超宽带(uwb)技术,蓝牙(bt)技术和其他技术来实现。

142.在示例性实施例中,电子设备800可以被一个或多个应用专用集成电路(asic)、数字信号处理器(dsp)、数字信号处理设备(dspd)、可编程逻辑器件(pld)、现场可编程门阵列(fpga)、控制器、微控制器、微处理器或其他电子元件实现,用于执行上述方法。

143.在示例性实施例中,还提供了一种非易失性计算机可读存储介质,例如包括计算机程序指令的存储器804,上述计算机程序指令可由电子设备800的处理器820执行以完成上述方法。

144.本公开涉及增强现实领域,通过获取现实环境中的目标对象的图像信息,进而借助各类视觉相关算法实现对目标对象的相关特征、状态及属性进行检测或识别处理,从而

得到与具体应用匹配的虚拟与现实相结合的ar效果。示例性的,目标对象可涉及与人体相关的脸部、肢体、手势、动作等,或者与物体相关的标识物、标志物,或者与场馆或场所相关的沙盘、展示区域或展示物品等。视觉相关算法可涉及视觉定位、slam、三维重建、图像注册、背景分割、对象的关键点提取及跟踪、对象的位姿或深度检测等。具体应用不仅可以涉及跟真实场景或物品相关的导览、导航、讲解、重建、虚拟效果叠加展示等交互场景,还可以涉及与人相关的特效处理,比如妆容美化、肢体美化、特效展示、虚拟模型展示等交互场景。可通过卷积神经网络,实现对目标对象的相关特征、状态及属性进行检测或识别处理。上述卷积神经网络是基于深度学习框架进行模型训练而得到的网络模型。

145.图7示出根据本公开实施例的一种电子设备的框图。参照图7,电子设备1900可以被提供为一服务器或终端设备。参照图7,电子设备1900包括处理组件1922,其进一步包括一个或多个处理器,以及由存储器1932所代表的存储器资源,用于存储可由处理组件1922的执行的指令,例如应用程序。存储器1932中存储的应用程序可以包括一个或一个以上的每一个对应于一组指令的模块。此外,处理组件1922被配置为执行指令,以执行上述方法。

146.电子设备1900还可以包括一个电源组件1926被配置为执行电子设备1900的电源管理,一个有线或无线网络接口1950被配置为将电子设备1900连接到网络,和一个输入输出(i/o)接口1958。电子设备1900可以操作基于存储在存储器1932的操作系统,例如微软服务器操作系统(windows server

tm

),苹果公司推出的基于图形用户界面操作系统(mac os x

tm

),多用户多进程的计算机操作系统(unix

tm

),自由和开放原代码的类unix操作系统(linux

tm

),开放原代码的类unix操作系统(freebsd

tm

)或类似。

147.在示例性实施例中,还提供了一种非易失性计算机可读存储介质,例如包括计算机程序指令的存储器1932,上述计算机程序指令可由电子设备1900的处理组件1922执行以完成上述方法。

148.本公开可以是系统、方法和/或计算机程序产品。计算机程序产品可以包括计算机可读存储介质,其上载有用于使处理器实现本公开的各个方面的计算机可读程序指令。

149.计算机可读存储介质可以是可以保持和存储由指令执行设备使用的指令的有形设备。计算机可读存储介质例如可以是(但不限于)电存储设备、磁存储设备、光存储设备、电磁存储设备、半导体存储设备或者上述的任意合适的组合。计算机可读存储介质的更具体的例子(非穷举的列表)包括:便携式计算机盘、硬盘、随机存取存储器(ram)、只读存储器(rom)、可擦式可编程只读存储器(eprom或闪存)、静态随机存取存储器(sram)、便携式压缩盘只读存储器(cd-rom)、数字多功能盘(dvd)、记忆棒、软盘、机械编码设备、例如其上存储有指令的打孔卡或凹槽内凸起结构、以及上述的任意合适的组合。这里所使用的计算机可读存储介质不被解释为瞬时信号本身,诸如无线电波或者其他自由传播的电磁波、通过波导或其他传输媒介传播的电磁波(例如,通过光纤电缆的光脉冲)、或者通过电线传输的电信号。

150.这里所描述的计算机可读程序指令可以从计算机可读存储介质下载到各个计算/处理设备,或者通过网络、例如因特网、局域网、广域网和/或无线网下载到外部计算机或外部存储设备。网络可以包括铜传输电缆、光纤传输、无线传输、路由器、防火墙、交换机、网关计算机和/或边缘服务器。每个计算/处理设备中的网络适配卡或者网络接口从网络接收计算机可读程序指令,并转发该计算机可读程序指令,以供存储在各个计算/处理设备中的计

算机可读存储介质中。

151.用于执行本公开操作的计算机程序指令可以是汇编指令、指令集架构(isa)指令、机器指令、机器相关指令、微代码、固件指令、状态设置数据、或者以一种或多种编程语言的任意组合编写的源代码或目标代码,所述编程语言包括面向对象的编程语言—诸如smalltalk、c++等,以及常规的过程式编程语言—诸如“c”语言或类似的编程语言。计算机可读程序指令可以完全地在用户计算机上执行、部分地在用户计算机上执行、作为一个独立的软件包执行、部分在用户计算机上部分在远程计算机上执行、或者完全在远程计算机或服务器上执行。在涉及远程计算机的情形中,远程计算机可以通过任意种类的网络—包括局域网(lan)或广域网(wan)—连接到用户计算机,或者,可以连接到外部计算机(例如利用因特网服务提供商来通过因特网连接)。在一些实施例中,通过利用计算机可读程序指令的状态信息来个性化定制电子电路,例如可编程逻辑电路、现场可编程门阵列(fpga)或可编程逻辑阵列(pla),该电子电路可以执行计算机可读程序指令,从而实现本公开的各个方面。

152.这里参照根据本公开实施例的方法、装置(系统)和计算机程序产品的流程图和/或框图描述了本公开的各个方面。应当理解,流程图和/或框图的每个方框以及流程图和/或框图中各方框的组合,都可以由计算机可读程序指令实现。

153.这些计算机可读程序指令可以提供给通用计算机、专用计算机或其它可编程数据处理装置的处理器,从而生产出一种机器,使得这些指令在通过计算机或其它可编程数据处理装置的处理器执行时,产生了实现流程图和/或框图中的一个或多个方框中规定的功能/动作的装置。也可以把这些计算机可读程序指令存储在计算机可读存储介质中,这些指令使得计算机、可编程数据处理装置和/或其他设备以特定方式工作,从而,存储有指令的计算机可读介质则包括一个制造品,其包括实现流程图和/或框图中的一个或多个方框中规定的功能/动作的各个方面的指令。

154.也可以把计算机可读程序指令加载到计算机、其它可编程数据处理装置、或其它设备上,使得在计算机、其它可编程数据处理装置或其它设备上执行一系列操作步骤,以产生计算机实现的过程,从而使得在计算机、其它可编程数据处理装置、或其它设备上执行的指令实现流程图和/或框图中的一个或多个方框中规定的功能/动作。

155.附图中的流程图和框图显示了根据本公开的多个实施例的系统、方法和计算机程序产品的可能实现的体系架构、功能和操作。在这点上,流程图或框图中的每个方框可以代表一个模块、程序段或指令的一部分,所述模块、程序段或指令的一部分包含一个或多个用于实现规定的逻辑功能的可执行指令。在有些作为替换的实现中,方框中所标注的功能也可以以不同于附图中所标注的顺序发生。例如,两个连续的方框实际上可以基本并行地执行,它们有时也可以按相反的顺序执行,这依所涉及的功能而定。也要注意的是,框图和/或流程图中的每个方框、以及框图和/或流程图中的方框的组合,可以用执行规定的功能或动作的专用的基于硬件的系统来实现,或者可以用专用硬件与计算机指令的组合来实现。

156.该计算机程序产品可以具体通过硬件、软件或其结合的方式实现。在一个可选实施例中,所述计算机程序产品具体体现为计算机存储介质,在另一个可选实施例中,计算机程序产品具体体现为软件产品,例如软件开发包(software development kit,sdk)等等。

157.上文对各个实施例的描述倾向于强调各个实施例之间的不同之处,其相同或相似

之处可以互相参考,为了简洁,本文不再赘述。

158.本领域技术人员可以理解,在具体实施方式的上述方法中,各步骤的撰写顺序并不意味着严格的执行顺序而对实施过程构成任何限定,各步骤的具体执行顺序应当以其功能和可能的内在逻辑确定。

159.若本技术技术方案涉及个人信息,应用本技术技术方案的产品在处理个人信息前,已明确告知个人信息处理规则,并取得个人自主同意。若本技术技术方案涉及敏感个人信息,应用本技术技术方案的产品在处理敏感个人信息前,已取得个人单独同意,并且同时满足“明示同意”的要求。例如,在摄像头等个人信息采集装置处,设置明确显著的标识告知已进入个人信息采集范围,将会对个人信息进行采集,若个人自愿进入采集范围即视为同意对其个人信息进行采集;或者在个人信息处理的装置上,利用明显的标识/信息告知个人信息处理规则的情况下,通过弹窗信息或请个人自行上传其个人信息等方式获得个人授权;其中,个人信息处理规则可包括个人信息处理者、个人信息处理目的、处理方式以及处理的个人信息种类等信息。

160.以上已经描述了本公开的各实施例,上述说明是示例性的,并非穷尽性的,并且也不限于所披露的各实施例。在不偏离所说明的各实施例的范围和精神的情况下,对于本技术领域的普通技术人员来说许多修改和变更都是显而易见的。本文中所用术语的选择,旨在最好地解释各实施例的原理、实际应用或对市场中的技术的改进,或者使本技术领域的其它普通技术人员能理解本文披露的各实施例。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1