一种UART控制器及数据传输有效性检测方法与流程

一种uart控制器及数据传输有效性检测方法

技术领域

1.本发明涉及一种uart控制器及数据传输有效性检测方法。

背景技术:

2.目前,在uart串口通信数据传输中,为了验证输出传输的正确性,在部分芯片与芯片数据通信过程中主要通过奇偶校验位来确保数据传输的有效性。uart串口通信数据传输只能一位一位的进行发送与接收,在每帧数据传输过程中,主要利用停止位来代表一帧数据传输完毕。例如当在使用偶校验方法来验证数据传输的正确性时,校验位会计算一帧数据传输中,数据位的“1”的个数,若“1”的个数为偶数,则校验位将输出成功,数据可继续进行传输。奇校验方法与偶校验方法类似,计算的是一帧数据中的“0”的个数。

3.但是,在uart串口通信数据传输中,通过奇偶校验位来确保数据传输的有效性不能检测出所有数据传输错误的情况,例如当一帧数据在传输时,若有两个、四个等偶数个bit位的数据传输错误,奇偶校验结果则会有误,因为奇偶校验位只会计算一帧数据中“1”或“0”的个数,偶数个bit位的数据发生传输错误,奇偶校验位则检测不出数据是否传输错误,且奇偶校验位只能用来检测,没有对帧数据进行修正的功能。而且,在众多芯片与芯片通信时,uart串口没有加入奇偶校验来验证数据传输的正确性。同时,在uart串口通信数据传输时,由于uart采用全双工、异步传输方式,抗干扰能力相对较差,易导致数据传输错误,且在芯片进行串口通信时,由于芯片之间使用的晶振不同,如果传输的数据内容过大,或者双方芯片通信距离过长,就会存在误差累积,影响数据传输的准确性,对芯片之间通信的数据传输准确性造成了很大的影响。

技术实现要素:

4.本发明所要解决的技术问题是,克服现有技术的不足,提供一种uart控制器及数据传输有效性检测方法,解决uart串口在数据传输过程中,当无奇偶校验位或者当一帧数据在传输时有偶数个bit位的数据传输错误,导致无法检测出数据传输错误的问题。解决当传输的数据过大或芯片通信距离过长时,数据存在误差累积,导致无法及时发现并中断数据传输的问题。解决uart串口在数据传输过程中,因抗干扰能力较差,导致的数据传输错误,无法及时中断的问题。

5.为了解决上述技术问题,本发明的技术方案是:

6.本发明一方面提供一种uart控制器,它包括:

7.接收器,所述接收器用于接收外部数据;

8.发送器,所述发送器用于向外部发送数据;

9.uart数据收发控制单元,所述uart数据收发控制单元用于控制接收器和发送器进行收发数据,并适时执行中断控制;

10.波特率生成器,所述波特率生成器用于控制收发数据的速率;

11.数据比较单元,所述数据比较单元用于根据uart数据收发控制单元发出的数据采

集指令采集接收器和发送器当前收发的数据,进行接收器和发送器每帧数据的比较。

12.进一步,所述uart数据收发控制单元包括数据接收控制单元、数据发送控制单元以及中断控制单元;

13.所述数据接收控制单元用于向接收器发送数据接收指令;

14.所述数据发送控制单元用于向发送器发送数据发送指令;

15.所述中断控制单元用于向接收器和发送器发送中断控制指令。

16.进一步,所述波特率生成器包括数据接收波特率控制单元和数据发送波特率控制单元;

17.所述数据接收波特率控制单元用于控制接收器接收数据的速率;

18.所述数据发送波特率控制单元用于控制发送器发送数据的速率。

19.进一步,所述数据比较单元包括数据fifo接收缓存寄存器、数据fifo发送缓存寄存器和两个级联的四位数值比较器。

20.本发明另一方面提供一种uart控制器的数据传输有效性检测方法,它包括:

21.步骤s1、uart数据收发控制单元发出数据接收指令,接收器接收外部芯片传输过来的数据;

22.步骤s2、uart数据收发控制单元发出数据比较指令,采集接收器接收的帧数据,放入到数据比较单元中的数据fifo接收缓存寄存器中;

23.步骤s3、uart数据收发控制单元发出数据发送指令,发送器将传输的数据向外发送;

24.步骤s4、uart数据收发控制单元发出数据比较指令,采集发送器发送的帧数据,放入到数据比较单元中的数据fifo发送缓存寄存器中;

25.步骤s5、利用数据比较单元的四位数值比较器对接收和发送的数据进行比较,并将比较结果及时反馈给uart数据收发控制单元,uart数据收发控制单元做出数据继续传输或中断操作,并控制数据比较单元进行复位清空数据fifo接收缓存寄存器和数据fifo发送缓存寄存器中。

26.进一步,所述步骤s1具体包括如下步骤:

27.uart数据收发控制单元接到外部数据接收指令后,发送数据接收指令给接收器,利用rx接收数据线接收到通信数据,接收一帧数据完毕之后,接收器向uart数据收发控制单元发送帧数据接收完毕指令。

28.进一步,所述接收一帧数据完毕的判断条件为接收器接收的帧数据的停止位启动。

29.进一步,所述步骤s3具体包括如下步骤:

30.uart数据收发控制单元向发送器发送数据发送指令,当发送器接收到uart数据收发控制单元要发送帧数据的指令后,发送器通过tx发送数据线进行每一帧数据的发送操作,发送一帧数据完毕之后,发送器向uart数据收发控制单元发送帧数据发送完毕指令。

31.进一步,所述发送一帧数据完毕的判断条件为发送器发送的帧数据的停止位启动。

32.进一步,所述步骤s5中,利用数据比较单元的四位数值比较器对接收和发送的数据进行比较,并将比较结果及时反馈给uart数据收发控制单元,具体包括如下步骤:

33.利用数据比较单元的四位数值比较器对接收器接收的一帧数据和发送器发送的一帧数据进行比较;

34.若接收器接收的一帧数据和发送器发送的一帧数据完全一致,数据比较单元输出高电平,则继续进行数据收发;

35.若接收器接收的一帧数据和发送器发送的一帧数据不一致,数据比较单元输出低电平,则中断数据收发。

36.采用了上述技术方案,本发明是通过在uart控制器内部增加数据比较单元,对发送器和接收器的数据进行抽样采集比较,给予uart数据收发控制单元数据收发情况及时反馈,解决了部分芯片与芯片之间数据传输无奇偶校验位或奇偶校验位识别不出数据传输有误的问题,大大地避免因数据传输错误对芯片之间通信的影响。通过在uart串口控制器内部加入数据比较单元,用来比较发送时的一帧数据和接收完毕时的同一帧数据,可以很好地避免uart串口在数据传输时奇偶校验位检测不出数据传输错误的问题。数据比较单元可根据需求对接收器和发送器传输的帧数据抽样采集然后进行比较,避免了数据传输时数据采集的时间冗长,导致传输速度过慢的问题。

附图说明

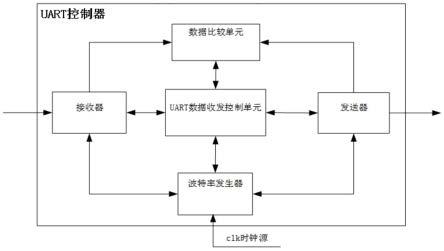

37.图1为本发明的一种uart控制器的原理框图;

38.图2为本发明的uart控制器的数据传输有效性检测方法的流程图。

具体实施方式

39.为了使本发明的内容更容易被清楚地理解,下面根据具体实施例并结合附图,对本发明作进一步详细的说明。

40.实施例一

41.如图1所示,本实施例提供一种uart控制器,它包括:接收器、发送器、uart数据收发控制单元、波特率生成器和数据比较单元。uart控制器具有两根外部收发数据线,一根rx用于接收数据,一根tx用于发送数据。

42.接收器用于接收外部数据,发送器用于向外部发送数据。

43.uart数据收发控制单元用于控制接收器和发送器进行收发数据,并适时执行中断控制。uart数据收发控制单元包括数据接收控制单元、数据发送控制单元以及中断控制单元;数据接收控制单元用于向接收器发送数据接收指令;数据发送控制单元用于向发送器发送数据发送指令;中断控制单元用于向接收器和发送器发送中断控制指令。

44.波特率生成器用于控制收发数据的速率,波特率生成器需连接时钟源。波特率生成器包括数据接收波特率控制单元和数据发送波特率控制单元;数据接收波特率控制单元用于控制接收器接收数据的速率;数据发送波特率控制单元用于控制发送器发送数据的速率。

45.数据比较单元用于根据uart数据收发控制单元发出的数据采集指令采集接收器和发送器当前收发的数据,进行接收器和发送器每帧数据的比较。数据比较单元包括数据fifo接收缓存寄存器、数据fifo发送缓存寄存器和两个级联的四位数值比较器。一般每帧数据是5到8个bit数据,根据每帧数据传输的位数,现有的数值比较器有四位数值比较器,

可进行2个四位数值比较器级联,即可进行5到8位的bit数据比较。

46.实施例二

47.如图2所示,本实施例提供一种uart控制器的数据传输有效性检测方法,它包括:

48.步骤s1、uart数据收发控制单元发出数据接收指令,接收器接收外部芯片传输过来的数据(接收方式为一帧一帧接收);

49.步骤s2、uart数据收发控制单元发出数据比较指令,采集接收器接收的帧数据,放入到数据比较单元中的数据fifo接收缓存寄存器中;

50.步骤s3、uart数据收发控制单元发出数据发送指令,发送器将传输的数据向外发送(发送方式为一帧一帧发送);

51.步骤s4、uart数据收发控制单元发出数据比较指令,采集发送器发送的帧数据,放入到数据比较单元中的数据fifo发送缓存寄存器中;

52.步骤s5、利用数据比较单元的四位数值比较器对接收和发送的数据进行比较,并将比较结果及时反馈给uart数据收发控制单元,uart数据收发控制单元做出数据继续传输或中断操作,并控制数据比较单元进行复位清空数据fifo接收缓存寄存器和数据fifo发送缓存寄存器中。

53.具体地,步骤s1具体包括如下步骤:

54.uart数据收发控制单元接到外部数据接收指令后,发送数据接收指令给接收器,利用rx接收数据线接收到通信数据,接收一帧数据完毕之后,接收器向uart数据收发控制单元发送帧数据接收完毕指令。其中,接收一帧数据完毕的判断条件为接收器接收的帧数据的停止位启动。uart串口的每帧数据一般是8位,最后一位是停止位。

55.具体地,步骤s3具体包括如下步骤:

56.uart数据收发控制单元向发送器发送数据发送指令,当发送器接收到uart数据收发控制单元要发送帧数据的指令后,发送器通过tx发送数据线进行每一帧数据的发送操作,发送一帧数据完毕之后,发送器向uart数据收发控制单元发送帧数据发送完毕指令。其中,发送一帧数据完毕的判断条件为发送器发送的帧数据的停止位启动。

57.具体地,步骤s5中,利用数据比较单元的四位数值比较器对接收和发送的数据进行比较,并将比较结果及时反馈给uart数据收发控制单元,具体包括如下步骤:

58.利用数据比较单元的四位数值比较器对接收器接收的一帧数据和发送器发送的一帧数据进行比较;

59.若接收器接收的一帧数据和发送器发送的一帧数据完全一致,数据比较单元输出高电平,则继续进行数据收发;

60.若接收器接收的一帧数据和发送器发送的一帧数据不一致,数据比较单元输出低电平,则中断数据收发。

61.假设接收器接收到11010101,发送器发送11010101,比较结果一致,输出高电平;如果发送器发送到结果是11011101,就是跟接收器结果不一致,就输出比较结果为低电平就是0,那中断单元进行中断数据收发。

62.本发明的工作原理如下:

63.如图2所示,uart控制器内部的uart数据收发控制单元接到外部数据接收指令后,发送数据接收指令给uart控制器内部的接收器,利用uart控制器的rx接收数据线接收到通

信数据,接收一帧数据完毕之后,接收器向uart数据收发控制单元发送帧数据接收完毕指令,再由uart数据收发控制单元向发送器发送数据发送指令,当发送器接收到uart数据收发控制单元要发送帧数据的指令后,发送器通过tx发送数据线进行每帧数据的发送操作。

64.在每帧数据传输时,当接收器和发送器中的帧数据的停止位启动后,uart数据收发控制单元开始向数据比较单元发送数据采集指令,接收到采集指令,数据比较单元开始采集接收器和发送器的每帧的数据位传输的数据,经过2个级联的四位数值比较器比较之后,将数据比较结果发送给uart数据收发控制单元,由uart数据收发控制单元根据比较结果来控制数据收发是否中断。

65.若数据比较结果无误,则继续进行数据收发,若有误,则中断数据收发。

66.同时,uart数据收发控制单元反馈数据比较复位信号给数据比较单元,复位清空之前比较数据内容,以便下次继续进行帧数据抽样采集。波特率发生器根据芯片之间数据传输的需求来控制数据传输的速率。

67.为了不影响数据传输的速度,uart数据收发控制单元对数据比较单元进行单独控制,更好地对发送器和接收器的数据进行抽样采集,且接收器和发送器数据采集的时间要分别在接收器接收每帧数据完毕之后的停止位及发送器发送数据完毕之后的停止位进行每帧的数据采集。

68.以上所述的具体实施例,对本发明解决的技术问题、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本发明的具体实施例而已,并不用于限制本发明,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1