以太网卡的制作方法

1.本技术涉及通讯信息技术领域,尤其涉及一种以太网卡。

背景技术:

2.网卡即网络接口控制器,又被称为网络适配器或局域网接收器,是构成计算机网络系统中最基本的、最重要的、最不可缺少的连接设备。现有的以太网卡不能稳定的接收电源的供电。

技术实现要素:

3.有鉴于此,本技术提出了一种以太网卡,其能够稳定的接收电源的供电,使得网卡能够稳定的工作。

4.根据本技术的一方面,提供了一种以太网卡,包括:板卡;

5.所述板卡上配置有处理器、通讯模块、pcle4.0接口、存储模块和时钟模块;

6.所述处理器为e810处理器;

7.所述通讯模块、所述pcle4.0接口、所述存储模块和所述时钟模块均与所述处理器电连接;

8.所述通讯模块通过qsfp28接口与所述处理器电连接;

9.所述板卡上还配置有电源输入模块、第一电平转换芯片、第二电平转换芯片、第三电平转换芯片、第四电平转换芯片和第五电平转换芯片;

10.所述电源输入模块的输入端适用于与供电电源电连接,所述电源输出模块的输出端与所述第一电平转换芯片的输入端、所述第二电平转换芯片的输入端、所述第三电平转换芯片的输入端和所述第四电平转换芯片的输入端均电连接;

11.所述第一电平转换芯片的输出端与所述第五电平转换芯片的输入端、所述存储模块、所述时钟模块和所述通讯模块、所述pcle4.0接口均电连接;

12.所述第二电平转换芯片的输出端、所述第三电平转换芯片的输出端、所述第四电平转换芯片的输出端和所述第五电平转换芯片的输出端均电连接至所述处理器。

13.在一种可能的实现方式中,所述第一电平转换芯片的vin引脚与所述电源输入模块的输出端电连接,用于接收所述电源输入模块输出的12v电压;

14.所述第一电平转换芯片的sw引脚外接第一电感后输出3.3v电压,作为所述第一电平转换芯片的输出端;

15.所述第一电平转换芯片的bst引脚和所述第一电平转换芯片的sw引脚之间串联有第一电阻和第一电容;

16.所述第一电平转换芯片的cr引脚和所述第一电感未与所述第一电平转换芯片的sw引脚连接的一端电连接,且串联有第二电容。

17.在一种可能的实现方式中,所述第一电平转换芯片的vin引脚和所述第一转换芯片的freq/mode引脚合并后与所述电源输入模块的输出端电连接;

18.所述第一电平转换芯片的vin引脚和所述第一电平转换芯片的freq/mode引脚之间串联有多个并联的电容和第二电阻;

19.所述第一电平转换芯片的输出端处外接有多个并联的电容,且多个并联的电容的另一端适用于接地。

20.在一种可能的实现方式中,所述第一电感未与所述第一电平转换芯片的sw引脚连接的一端和所述第一电平转换芯片的fb引脚之间并联有第三电阻和第三电容;

21.所述第三电阻、所述第三电容与所述第一电平转换芯片的fb引脚连接的一端还电连接有第四电阻;

22.所述第四电阻的另一端接地;

23.所述第一电平转换芯片的vcc引脚和所述第一电平转换芯片的pg引脚之间串联有第五电阻。

24.在一种可能的实现方式中,,所述第二电平转换芯片的vin引脚与所述电源输入模块的输出端电连接,用于接收所述电源输入模块输出的12v电压;

25.所述第二电平转换芯片的sw引脚外接第二电感后输出1.1v电压,作为所述第二电平转换芯片的输出端;

26.所述第二电平转换芯片的bst引脚和所述第二电平转换芯片的sw引脚之间串联有第六电阻和第四电容;

27.所述第二电平转换芯片的cr引脚和所述第二电感未与所述第二电平转换芯片的sw引脚连接的一端电连接,且串联有第五电容。

28.在一种可能的实现方式中,所述第三电平转换芯片的vin引脚与所述电源输入模块的输出端电连接,用于接收所述电源输入模块输出的12v电压;

29.所述第三电平转换芯片的sw引脚外接第三电感后输出0.9v电压,作为所述第三电平转换芯片的输出端;

30.所述第三电平转换芯片的bst引脚和所述第三电平转换芯片的sw引脚之间电连接有第六电容。

31.在一种可能的实现方式中,所述第四电平转换芯片的vin引脚与所述电源输入模块的输出端电连接,用于接收所述电源输入模块输出的12v电压;

32.所述第四电源转换芯片的sw引脚外接第四电感后输出0.8v电压,作为所述第四电平转换芯片的输出端;

33.所述第四电平转换芯片的bst引脚和所述第四电平转换芯片的sw引脚之间电连接有第七电容。

34.在一种可能的实现方式中,所述第五电平转换芯片的vin引脚与所述第一电平转换芯片的输出端电连接,用于接收所述第一电平转换芯片的输出端输出的3.3v电压;

35.所述第五电平转换芯片的vout引脚输出1.8v电压,作为所述第五电平转换芯片的输出端;

36.所述第五电平转换芯片vout引脚与第五电平转换芯片bypass引脚之间依次串联有并联设置有两个以上的电容和第八电容。

37.在一种可能的实现方式中,所述通讯模块设置有两个,两个所述通讯模块均与所述第一电平转换芯片的输出端、所述处理器电连接。

38.在一种可能的实现方式中,所述存储模块为128mb的spi flash,且通过spi接口与所述处理器电连接。

39.本技术实施例以太网卡设置有板卡,板卡上设置有处理器、通讯模块、pcle4.0接口、存储模块、时钟模块、电源输入模块、第一电平转换芯片、第二电平转换芯片、第三电平转换芯片、第四电平转换芯片和第五电平转换芯片,其中,板卡其e810处理器,并通过电源输入模块将电源输入,并生成12v的电压。第一电平转换芯片、第二电平转换芯片、第三电平转换芯片和第四电平转换芯片接收电源输入模块的12v电压,且第一电平转换芯片将电压进行转换后输出给第一电平转换芯片以及通讯模块、pcle4.0接口、存储模块、时钟模块以对上述的电子器件进行供电。第二电平转换芯片、第三电平转换芯片和第四电平转换芯片将同一电压转换为不同电压后均输出至处理器,由此方便对处理器的不同状态进行供电。综上所述,本技术实施例以太网卡通过上述的电路结构能够稳定的接收电源的供电,使得网卡能够稳定的工作。

40.根据下面参考附图对示例性实施例的详细说明,本技术的其它特征及方面将变得清楚。

附图说明

41.包含在说明书中并且构成说明书的一部分的附图与说明书一起示出了本技术的示例性实施例、特征和方面,并且用于解释本技术的原理。

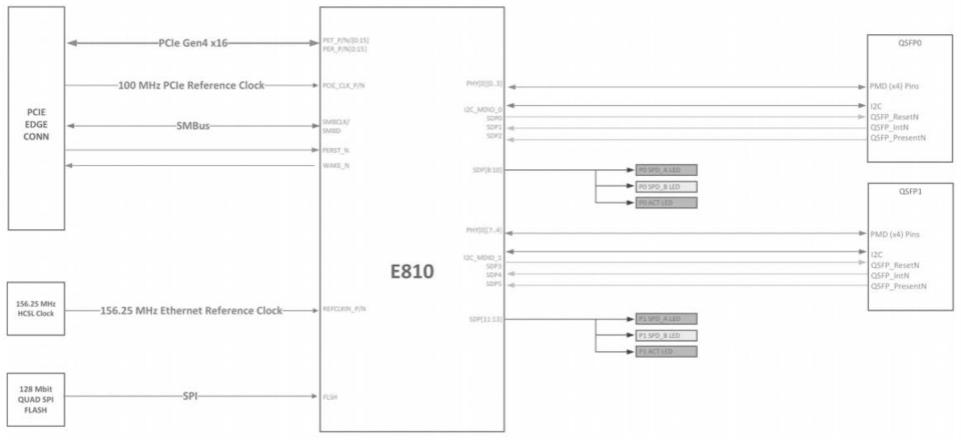

42.图1示出本技术实施例的以太网卡的板卡框图;

43.图2示出本技术实施例的以太网卡的第一电平转换芯片的电路图;

44.图3示出本技术实施例的以太网卡的第二电平转换芯片的电路图;

45.图4示出本技术实施例的以太网卡的第三电平转换芯片的电路图;

46.图5示出本技术实施例的以太网卡的第四电平转换芯片的电路图;

47.图6示出本技术实施例的以太网卡的第五电平转换芯片的电路图;

48.图7示出本技术实施例的以太网卡的存储模块的电路图;

49.图8示出本技术实施例的以太网卡的时钟模块的电路图;

50.图9示出本技术实施例的以太网卡的通讯模块的电路图;

51.图10示出本技术实施例的以太网卡的电源输入模块的电路图。

具体实施方式

52.以下将参考附图详细说明本技术的各种示例性实施例、特征和方面。附图中相同的附图标记表示功能相同或相似的元件。尽管在附图中示出了实施例的各种方面,但是除非特别指出,不必按比例绘制附图。

53.其中,需要理解的是,术语“中心”、“纵向”、“横向”、“长度”、“宽度”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”、“内”、“外”、“顺时针”、“逆时针”、“轴向”、“径向”、“周向”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明或简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。

54.此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性

或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征。在本发明的描述中,“多个”的含义是两个或两个以上,除非另有明确具体的限定。

55.在这里专用的词“示例性”意为“用作例子、实施例或说明性”。这里作为“示例性”所说明的任何实施例不必解释为优于或好于其它实施例。

56.另外,为了更好的说明本技术,在下文的具体实施方式中给出了众多的具体细节。本领域技术人员应当理解,没有某些具体细节,本技术同样可以实施。在一些实例中,对于本领域技术人员熟知的方法、手段、元件和电路未作详细描述,以便于凸显本技术的主旨。

57.图1示出本技术实施例的以太网卡的板卡框图。图2示出本技术实施例的以太网卡的第一电平转换芯片的电路图。图3示出本技术实施例的以太网卡的第二电平转换芯片的电路图。图4示出本技术实施例的以太网卡的第三电平转换芯片的电路图。图5示出本技术实施例的以太网卡的第四电平转换芯片的电路图。图6示出本技术实施例的以太网卡的第五电平转换芯片的电路图。图7示出本技术实施例的以太网卡的存储模块的电路图。图8示出本技术实施例的以太网卡的时钟模块的电路图。图9示出本技术实施例的以太网卡的通讯模块的电路图。图10示出本技术实施例的以太网卡的电源输入模块的电路图。如图1至图10所示,该以太网卡,包括:板卡,板卡上配置有处理器、通讯模块、pcle4.0接口、存储模块和时钟模块。处理器为e810处理器,电子器件包括通讯模块、pcle4.0接口、存储模块和时钟模块,通讯模块、pcle4.0接口、存储模块和时钟模块均与处理器电连接,且通讯模块通过qsfp28接口与处理器电连接。板卡上还配置有电源输入模块、第一电平转换芯片、第二电平转换芯片、第三电平转换芯片、第四电平转换芯片和第五电平转换芯片。电源输入模块的输入端适用于与供电电源电连接,电源输出模与第一电平转换芯片的输入端、第二电平转换芯片的输入端、第三电平转换芯片的输入端和第四电平转换芯片的输入端均电连接。第一电平转换芯片的输出端与第五电平转换芯片的输入端、存储模块、时钟模块和通讯模块、pcle4.0接口均电连接。第二电平转换芯片的输出端、第三电平转换芯片的输出端、第四电平转换芯片的输出端和第五电平转换芯片的输出端均电连接至处理器。

58.本技术实施例以太网卡设置有板卡,板卡上设置有处理器、通讯模块、pcle4.0接口、存储模块、时钟模块、电源输入模块、第一电平转换芯片、第二电平转换芯片、第三电平转换芯片、第四电平转换芯片和第五电平转换芯片,其中,板卡其e810处理器,并通过电源输入模块将电源输入,并生成12v的电压。第一电平转换芯片、第二电平转换芯片、第三电平转换芯片和第四电平转换芯片接收电源输入模块的12v电压,且第一电平转换芯片将电压进行转换后输出给第一电平转换芯片以及通讯模块、pcle4.0接口、存储模块、时钟模块以对上述的电子器件进行供电。第二电平转换芯片、第三电平转换芯片和第四电平转换芯片将同一电压转换为不同电压后均输出至处理器,由此方便对处理器的不同状态进行供电。综上所述,本技术实施例以太网卡通过上述的电路结构可以使得能够稳定的接收电源的供电,使得网卡能够稳定的工作。

59.此处,应当指出的是,在一种可能的实现方式中,板卡上贴有散热片,由此可以避免运行过程中温度过高,加强了本技术实施例的散热性,且板卡可以采用6-8层的pcb板。

60.此处,还应当指出的是,在一种可能的实现方式中,板卡的表面还喷涂有锡层,由此可以放置板卡裸铜氧化和保持焊锡性。

61.此处,还应当指出的是,在一种可能的实现方式中,板卡的尺寸为167.5mm x63.9mm。

62.此处,还应当指出的是,在一种可能的实现方式中,通讯模块、pcle4.0接口均采用5μ沉金,接触更可靠,损耗更小,可有效降低丢包和数据延迟。

63.在一种可能的实现方式中,第一电平转换芯片的vin引脚与电源输入模块的输出端电连接,用于接收电源输入模块输出的12v电压。第一电平转换芯片的sw引脚外接第一电感l2后输出3.3v电压,作为第一电平转换芯片的输出端。第一电平转换芯片的bst引脚和第一电平转换芯片的sw引脚之间串联有第一电阻r360和第一电容c419。第一电平转换芯片的cr引脚和第一电感未与第一电平转换芯片的sw引脚连接的一端电连接,且串联有第二电容c420。

64.此处,应当指出的是,在一种可能的实现方式中,第一电感l2的型号为:4.7uh-fmds6024-4r7m。

65.更进一步的,在一种可能的实现方式中,第一电平转换芯片的vin引脚和第一转换芯片的freq/mode引脚合并后与电源输入模块的输出端电连接。第一电平转换芯片的vin引脚和第一转换芯片的freq/mode引脚之间串联有多个并联的电容和第二电阻r90。第一电平转换芯片的输出端处外接有多个并联的电容,且多个并联的电容的另一端适用于接地。

66.在一种可能的实现方式中,第一电感l2未与第一电平转换芯片的sw引脚连接的一端和第一电平转换芯片的fb引脚之间并联有第三电阻r104和第三电容c130。第三电阻r104、第三电容c130与第一电平转换芯片的fb引脚连接的一端还电连接有第四电阻r88,第四电阻r88的另一端接地。第一电平转换芯片的vcc引脚和第一电平转换芯片的pg引脚之间串联有第五电阻r359。

67.此处,应当指出的是,在一种可能的实现方式中,第一电平转换芯片的ss引脚处外接有电容c418,第一电平转换芯片的gnd引脚接地,电容c418的另一端电连接在第一电平转换芯片的gnd引脚处。

68.此处,还应当指出的是,在一种可能的实现方式中,第一电平转换芯片的vcc引脚处还外接有电容c204,且电容c204的另一端接地。

69.在一种可能的实现方式中,第二电平转换芯片的vin引脚与电源输入模块的输出端电连接,用于接收电源输入模块输出的12v电压。第二电平转换芯片的sw引脚外接第二电感l13后输出1.1v电压,作为第二电平转换芯片的输出端。第二电平转换芯片的bst引脚和第二电平转换芯片的sw引脚之间串联有第六电阻r365和第四电容c433。第二电平转换芯片的cr引脚和第二电感未与第二电平转换芯片的sw引脚连接的一端电连接,且串联有第五电容c434。

70.此处,应当指出的是,在一种可能的实现方式中,第二电感l13的型号为:2.2uh-fmds6024-2r2m。

71.此处,还应当指出的是,在一种可能的实现方式中,第二电平转换芯片的vin引脚和第二电平转换芯片的freq/mode引脚合并后与电源输入模块的输出端电连接。且第二电平转换芯片的vin引脚和第二电平转换芯片的freq/mode引脚之间串联有多个并联的电容和电阻r363。第二电平转换芯片的输出端处外接有多个并联的电容,且多个并联的电容的另一端适用于接地。

72.此处,还应当指出的是,在一种可能的实现方式中,第二电感l13为由第二电平转换芯片的sw引脚连接的一端和第二电平转换芯片的fb引脚之间并联有电阻r364和电容c426。且电阻r364、电容c426与第二电平转换芯片的fb引脚连接的一端还电连接有电阻r361,且电阻r361的另一端接地。第二电平转换芯片的vcc引脚和第二电平转换芯片的pg引脚之间串联有电阻r362。

73.此处,还应当指出的是,在一种可能的实现方式中,第二电平转换芯片的vcc引脚处还外接有电容c424,电容c424的另一端接地。

74.此处,还应当指出的是,在一种可能的实现方式中,第二电平转换芯片的ss引脚处外接有电容c423,第二电平转换芯片的gnd引脚接地,电容c423的另一端电连接在第二电平转换芯片的gnd引脚处。

75.在一种可能的实现方式中,第三电平转换芯片的vin引脚与电源输入模块的输出端电连接,用于接收电源输入模块输出的12v电压。第三电平转换芯片的sw引脚外接第三电感l3后输出0.9v电压,作为第三电平转换芯片的输出端。第三电平转换芯片的bst引脚和第三电平转换芯片的sw引脚之间电连接有第六电容c440。

76.此处,应当指出的是,在一种可能的实现方式中,第三电感l13的型号为:0.57μh-ihlp4040dzerr56md。

77.此处,应当指出的是,在一种可能的实现方式中,第三电平转换芯片的vin引脚处外接有多个并联设置的电容,且多个并联设置的电容的另一端接地。第三电平转换芯片的输出端处外接有多个并联设置的电容,且此处的并联设置的电容的一端与第三电感l13电连接,另一端接地。

78.此处,还应当指出的是,在一种可能的实现方式中,第三电平转换芯片的sw引脚和第三电平转换芯片的fb引脚之间还电连接有电阻r378和电容c443,且电阻r378和电容c443的一端与第三电感l3电连接,另一端与电阻r377电连接,电阻r377的另一端接地。

79.此处,还应当指出的是,在一种可能的实现方式中,第三电平转换芯片的pgood引脚处外接有串联设置的电阻r379和电容c439,第三电平转换芯片的vcc引脚电连接在电阻r379和电容c439之间。第三电平转换芯片的mode引脚处外接有电阻r376,第三电平转换芯片的cs引脚处外接有电阻r380。第三电平转换芯片的tpk/ref引脚外接有并联设置在电容c441和电容c442。且电容c439、电阻r376、电阻r380、并联设置的电容c441和电容c442的另一端、第三电平转换芯片的rgnd引脚、第三电平转换芯片的agnd引脚合并后接地。

80.在一种可能的实现方式中,第四电平转换芯片的vin引脚与电源输入模块的输出端电连接,用于接收电源输入模块输出的12v电压。第四电源转换芯片的sw引脚外接第四电感l14后输出0.8v电压,作为第四电平转换芯片的输出端。第四电平转换芯片的bst引脚和第四电平转换芯片的sw引脚之间电连接有第七电容c456。

81.此处,应当指出的是,在一种可能的实现方式中,第四电感l14的型号为:0.57μh-ihlp4040dzerr56md1。

82.此处,还应当指出的是,在一种可能的实现方式中,第四电平转换芯片的vin引脚处外接有多个并联设置的电容,且多个并联设置的电容的另一端接地。第四电平转换芯片的输出端处外接有多个并联设置的电容,且此处的并联设置的电容的一端与第四电感l14电连接,另一端接地。

83.此处,还应当指出的是,在一种可能的实现方式中,第四电平转换芯片的sw引脚和第四电平转换芯片的fb引脚之间还电连接有电阻r385和电容c458,且电阻r385和电容c458的一端与第四电感l14电连接,另一端与电阻r384电连接,电阻r384的另一端接地。

84.此处,还应当指出的是,在一种可能的实现方式中,第四电平转换芯片的pgood引脚处外接有串联设置的电阻r381和电容c449,第四电平转换芯片的vcc引脚电连接在电阻r381和电容c449之间。第四电平转换芯片的mode引脚处外接有电阻r383,第四电平转换芯片的cs引脚处外接有电阻r382。第四电平转换芯片的tpk/ref引脚外接有并联设置在电容c455和电容c457。且电容c449、电阻r381、电阻r381、并联设置的电容c455和电容c457的另一端、第四电平转换芯片的rgnd引脚、第四电平转换芯片的agnd引脚合并后接地。

85.在一种可能的实现方式中,第五电平转换芯片的vin引脚与第一电平转换芯片的输出端电连接,用于接收第一电平转换芯片的输出端输出的3.3v电压。第五电平转换芯片的vout引脚输出1.8v电压,作为第五电平转换芯片的输出端。第五电平转换芯片vout引脚与第五电平转换芯片bypass引脚之间依次串联有并联设置有两个以上的电容和第八电容c462。

86.此处,应当指出的是,在一种可能的实现方式中,第五电平转换芯片vout引脚与第五电平转换芯片bypass引脚之间依次串联有并联设置有电容c120和电容c466。

87.此处,还应当指出的是,在一种可能的实现方式中,第五电平转换芯片的vin引脚处外接有并联设置的电容ct15和电容c162。第五电平转换芯片的gnd引脚和并联设置的电容ct15和电容c162的另一端合并后接地。

88.在一种可能的实现方式中,通讯模块设置有两个,两个通讯模块均与第一电平转换芯片的输出端和处理器电连接。且通讯模块均为100g的网络接口,用于网络通信用。

89.在一种可能的实现方式中,存储模块为128mb的spi flash,且通过spi接口与处理器电连接。

90.此处,应当指出的是,在一种可能的实现方式中,存储模块包括存储芯片,存储芯片的cs#引脚、wp#引脚和hold#引脚均与第一电平转换芯片的输出端电连接,用于接入3.3v电压。存储芯片的sck引脚处外接有电阻r78。存储芯片的wp#引脚和第一电平转换芯片的输出端之间电连接有电阻r184,存储芯片的cs#引脚和第一电平转换芯片的输出端之间电连接有电阻r72。存储芯片的vcc引脚处外接有电容c160。且存储芯片的hold#引脚和第一电平转换芯片的输出端之间电连接有电阻r183,且电阻r183未与存储芯片的hold#引脚电连接的一端电连接在存储芯片的vcc引脚和电容c160之间。存储芯片的sck引脚处外接有电阻r182。

91.此处,还应当指出的是,在一种可能的实现方式中,时钟模块包括时钟发生器,其生成1路156.25m差分时钟。且时钟发生器的vcc引脚与第一电平转换芯片的输出端电连接,用于接收3.3v电压,且时钟发生器的vcc引脚还外接有电容c282。时钟发生器的oe引脚处外接有电阻r255,时钟发生器的output引脚处外接有电阻r269,时钟发生器的output-n引脚处外接有电阻r263。

92.以上已经描述了本技术的各实施例,上述说明是示例性的,并非穷尽性的,并且也不限于所披露的各实施例。在不偏离所说明的各实施例的范围和精神的情况下,对于本技术领域的普通技术人员来说许多修改和变更都是显而易见的。本文中所用术语的选择,旨

在最好地解释各实施例的原理、实际应用或对市场中的技术的改进,或者使本技术领域的其它普通技术人员能理解本文披露的各实施例。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1