一种基于忆阻器的多功能PUF电路及其使用方法

一种基于忆阻器的多功能puf电路及其使用方法

技术领域

1.本发明属于硬件安全技术领域。具体涉及一种基于忆阻器的多功能puf电路及其使用方法。

背景技术:

2.随着集成电路技术的快速发展,电子设备给人们的生产和生活带来了巨大的便利,但同时所面临的安全问题也日益突出。例如,电子设备在硬件上极易受到硬件克隆、硬件木马和硬件篡改的威胁,会给物联网、医疗设备、汽车电子、航空航天等领域的安全带来影响。因此,物理不可克隆函数(physically unclonable function,puf)在硬件安全领域作为一种全新的硬件安全保护方案备受人们的广泛关注。

3.puf电路具有输入和输出信号,它的输入信号被称作激励(challenge),输出信号被称作响应(response)。一个激励和其对应的响应称为激励响应对(challenge response pairs,crps)。puf具有随机性和唯一性等特性,同一工艺下生产出的元器件在参数上具有随机差异,生产厂家利用这种元器件的参数差异制作出的puf电路是独一无二的,因此puf电路是不可克隆的。另外puf不仅具有功耗低、结构简单、安全性高等优势,而且在解决硬件认证和加密等安全问题方面有着独特的优势。

4.puf电路根据crps的数量可以分为强puf电路和弱puf电路,强puf电路一般应用在身份认证中,弱puf电路一般应用在密钥生成中。基于忆阻器的puf电路大多数都是强puf电路,对含有强puf电路的电子设备进行身份认证后该puf电路将处于闲置状态,如果该puf电路既具有puf又具有trng(true random number generator)的功能,在完成身份认证后还可以将该puf电路作为trng来使用,这将提高该puf电路的利用率。

5.目前,既可以作为puf又可以作为trng使用的puf电路的研究处于起步阶段。kumar rai等人(rai v k,tripathy s,mathew j.design and analysis of reconfigurable cryptographic primitives:trng and puf[j].journal of hardware and systems security,2021,5(3):247-259.)在传统环形振荡puf电路的基础上提出了一种既可以作为puf又可以作为trng使用的puf电路。该puf电路的基本结构由两个相同的环形振荡器、两个d触发器、一个nmos管和模式选择开关组成。当该puf电路工作在puf模式时,第一个d触发器的输出端将不断产生固定的比特流。在第二个d触发器的时钟端施加时钟信号后,在一个时钟周期中,当时钟信号由低电平变为高电平状态时第二个d触发器的输出端将输出一位puf响应。由于反相器在不同环境下的参数具有差异性,因此在不同环境下相同激励所产生的puf电路的输出也可能不相同,因此,该puf电路作为puf使用时其可靠性较低。当该puf电路工作在trng模式时,该puf电路所施加的激励全为低电平,启动信号施加后,两个环形振荡器各以一个固定的频率开始振荡运行,导致第一个d触发器输出一个固定的比特流,因此该puf电路不能作为trng来使用。

[0006]

nafis irtija等人(irtija n,tsiropoulou e e,minwalla c,et al.true random number generation with the shift-register reconvergent-fanout(sirf)puf

[c]//2022ieee international symposium on hardware oriented security and trust(host).ieee,2022:101-104.)在puf电路的基础上设计了一种真随机数发生器,该电路由门阵列、移位寄存器、时间-数据转换器(time-to-digital-converter,tdc)、比特流发生器(bitgen)模块组成。当该电路作为puf使用时,由于同一工艺生产出的门电路在参数上存在随机差异,导致脉冲信号经过门阵列后会产生随机延迟,延迟时间就是puf电路的响应。由于该电路以门阵列作为脉冲信号的延迟路径,并且使用高精度tdc转换器来采集脉冲信号的延迟时间,因此硬件消耗大。当该电路作为trng使用时,首先在puf模式下工作,得到多组信号激励下脉冲信号的延迟时间,将这些延迟时间存入ram中,然后通过sirf(shift-register reconvergent-fanout)算法将延迟时间进行配对以产生随机差异,再将随机差异通过gpevcm算法(global-process-environmental-variation-calibration-method)进行校准,以减小环境对延迟时间的影响,并将gpevcm校准后的随机差异值输入到bitgen模块中,bitgen模块将产生随机的比特流,最后将随机的比特流存入ram中并且作为trng的输出。如此循环,bitgen模块将不断输出真随机数。由于该电路采用了多种算法,因此结构复杂且硬件消耗大。

[0007]“一种基于物理不可克隆函数puf的真随机数发生器”(cn111966329a)专利技术,该技术在传统环形振荡电路中增加了两个寄存器,这两个寄存器分别用于存储两个计数器中的数值,然后将寄存器中的低位作为trng的输出,高位送入比较器进行比较得到puf的响应,因此该电路虽可同时作为trng和puf来使用。但是不能持续地产生真随机数,只有在每次施加激励后才能输出一个真随机数,并且当两个振荡环路的振荡频率较为接近时,两个计数器中的数值也会较为接近,从而导致寄存器中的高位可能相同,并最终导致puf的唯一性偏低。

技术实现要素:

[0008]

本发明旨在克服现有技术的缺陷,目的是提供一种结构简单、成本低的基于忆阻器的多功能puf电路,该电路具有puf功能和trng功能,作为puf使用时具有良好的性能指标,作为trng使用时能够持续的产生真随机数。

[0009]

为实现上述目的,本发明采用的技术方案是:所述基于忆阻器的多功能puf电路(以下简称“多功能puf电路”)由移位寄存器电路、复位电路、仲裁器电路、延迟电路和模式控制电路组成。

[0010]

所述为多功能puf电路中:i为1与n之间的任一自然数,n为大于等于3的自然数。

[0011]

移位寄存器电路的端子ar与仲裁器电路的端子v

out

连接,移位寄存器电路的端子a

clk2

与延迟电路的端子a

clk1

连接,移位寄存器电路的端子a

r11

、

……

、a

r1i

、

……

、a

r1n

与模式控制电路的端子a

r21

、

……

、a

r2i

、

……

、a

r2n

对应连接。

[0012]

复位电路的端子a

rst2

与延迟电路的端子a

rst1

连接,复位电路的端子a

rs1

与仲裁器电路的端子a

d4

和延迟电路的端子a

d2

分别连接,复位电路的端子a

rs2

与仲裁器电路的端子a

dclk4

和延迟电路的端子a

dclk2

分别连接。

[0013]

仲裁器电路的端子a

d3

与延迟电路的端子a

d1

连接,仲裁器电路的端子a

dclk3

与延迟电路的端子a

dclk1

连接,仲裁器电路的端子a

c41

与模式控制电路的端子a

c2i

和延迟电路的端子a

c3i

分别连接,仲裁器电路的端子a

md3

与模式控制电路的端子a

md1

、延迟电路的端子a

md2

分别

连接,仲裁器电路的端子a

gnd2

与延迟电路的端子a

gnd1

连接。

[0014]

延迟电路的端子a

c31

、

……

、a

c3i

、

……

、a

c3n

与模式控制电路的端子a

c21

、

……

、a

c2i

、

……

、a

c2n

对应连接。

[0015]

多功能puf电路的输入端子v

clk

、v

rst

、v

vdd

、v

mode

、gnd、v

puf

、v

trng

、v

rt

、v

ctrl

与移位寄存器电路的端子a

clk2

、复位电路的端子a

rst2

、复位电路的端子a

vdd

、仲裁器电路的端子a

md3

、仲裁器电路的端子a

gnd2

、延迟电路的端子a

puf

、延迟电路的端子a

trng

、延迟电路的端子a

rt

、延迟电路的端子a

ctrl

对应连接。

[0016]

多功能puf电路的输入端子v

c1

、

……

、v

ci

、

……

、v

cn

与模式控制电路的端子a

c11

、

……

、a

c1i

、

……

、a

c1n

对应连接。

[0017]

多功能puf电路的输出端子v

out

与仲裁器电路的端子a

out

连接。

[0018]

所述移位寄存器电路由n个d触发器组成,第1d触发器的端子d与移位寄存器电路的端子ar连接;第1d触发器的端子q与端子a

r11

连接、

……

、第id触发器的端子q与端子a

r1i

连接、

……

、第nd触发器的端子q与端子a

r1n

连接;第1d触发器的端子q与第2d触发器的端子d连接、

……

、第i-1d触发器的端子q与第id触发器的端子d连接、

……

、第n-1d触发器的端子q与第nd触发器的端子d连接;第1d触发器的端子clk、

……

、第id触发器的端子clk、

……

、第nd触发器的端子clk与移位寄存器电路端子a

clk2

分别连接。

[0019]

所述复位电路由第1复位电路nmos管和第2复位电路nmos管组成,第1复位电路nmos管的栅极和第2复位电路nmos管的栅极与复位电路的端子a

rst2

分别连接,第1复位电路nmos管的漏极和第2复位电路nmos管的漏极与复位电路的端子a

vdd

分别连接,第1复位电路nmos管的源级与复位电路的端子a

rs2

连接,第2复位电路nmos管的源级与复位电路的端子a

rs1

连接。

[0020]

所述仲裁器电路由第1仲裁器电路d触发器、第1仲裁器电路选通器、第2仲裁器电路选通器、分路器、第2仲裁器电路d触发器组成;第1仲裁器电路d触发器的端子q与第1仲裁器电路选通器的端子1_chan连接,第1仲裁器电路选通器的端子0_chan与分路器的端子0_chan连接,第1仲裁器电路选通器的端子out与第2仲裁器电路选通器的端子0_chan连接,第2仲裁器电路选通器的端子sel与分路器的端子sel连接,第2仲裁器电路选通器的端子1_chan与分路器的端子1_chan连接,分路器的端子in与第2仲裁器电路d触发器的端子q连接。

[0021]

第1仲裁器电路d触发器的端子d、端子clk与仲裁器电路的端子a

d3

、a

dclk3

对应连接,第2仲裁器电路d触发器的端子d、端子clk与仲裁器电路的端子a

d4

、a

dclk4

对应连接,第1仲裁器电路d触发器的端子sel与仲裁器电路的端子a

c41

连接,第2仲裁器电路选通器的端子sel、分路器的端子sel分别与仲裁器电路的端子a

md3

连接。

[0022]

第2仲裁器电路选通器的端子out与仲裁器电路的端子a

out

连接。

[0023]

分路器由第1分路器选通器和第2分路器选通器组成;第1分路器选通器的端子1_chan与第2分路器选通器的端子0_chan连接,第1分路器选通器的端子0_chan与第2分路器选通器的端子1_chan连接,第1分路器选通器的端子sel与第2分路器选通器端子sel连接。

[0024]

第1分路器选通器的端子1_chan、端子sel、端子0_chan、端子out与分路器的端子in、端子sel、端子a

gnd3

、端子1_chan对应连接,第2分路器选通器的端子out与分路器的端子0_chan连接。

[0025]

所述延迟电路由第1选通器、第1延迟电路分路器、第2延迟电路分路器、第1nmos

管、第2nmos管、第3nmos管、第4nmos管、第5nmos管、n个延迟单元、第6nmos管、第7nmos管、第8nmos管、第9nmos管、第2选通器、第10nmos管、第3选通器、第4选通器、第5选通器组成。

[0026]

第1延迟电路分路器和第2延迟电路分路器与仲裁器电路中的分路器相同。

[0027]

第1选通器的端子sel与第1延迟电路分路器的端子sel连接,第1选通器的端子out与第1延迟电路分路器的端子in连接,第1延迟电路分路器的端子0_chan与第2延迟电路分路器的端子in连接,第1延迟电路分路器的端子1_chan与第1nmos管的栅极、第1nmos管的漏极、第2nmos管的栅极、第2nmos管的漏极分别连接,第1延迟电路分路器的端子a

gnd3

与第2延迟电路分路器的端子a

gnd3

、第5nmos管的源级、第6nmos管的源级、第9nmos管的源级、第10nmos管的源级、第2选通器的端子1_chan、第4选通器的端子0_chan、第5选通器的端子1_chan分别连接。

[0028]

第2延迟电路分路器的端子sel与第i延迟单元的端子v

c1i

、第2选通器的端子sel、第4选通器的端子sel分别连接,第2延迟电路分路器的端子1_chan与第7nmos管的栅极、第7nmos管的漏极、第8nmos管的栅极、第8nmos管的漏极分别连接,第2延迟电路分路器的端子0_chan与第3nmos管的栅极、第3nmos管的漏极、第4nmos管的栅极、第4nmos管的漏极分别连接,第1nmos管的源级与第3nmos管的源级、第5nmos管的漏极、第1延迟单元的端子v

rdly1

分别连接,第2nmos管的源级与第4nmos管的源级、第10nmos管的漏极、第1延迟单元(509)的端子v

rdly2

分别连接,第7nmos管的源级与第6nmos管的漏极、第n延迟单元的端子v

odly1

分别连接,第8nmos管的源级与第9nmos管的漏极、第n延迟单元的端子v

odly2

分别连接,第5nmos管的栅极与第10nmos管的栅极、第3选通器的端子out分别连接,第1延迟单元的端子v

odly1

、端子v

odly2

与第2延迟单元的端子v

rdly1

、端子v

rdly2

对应连接、

……

、第i-1延迟单元的端子v

odly1

、端子v

odly2

与第i延迟单元的端子v

rdly1

、端子v

rdly2

对应连接、

……

、第n-1延迟单元的端子v

odly1

、端子v

odly2

与第n延迟单元的端子v

rdly1

、端子v

rdly2

对应连接,第6nmos管的栅极与第9nmos管的栅极、第2选通器的端子out分别连接,第2选通器的端子0_chan与第4选通器的端子1_chan、第5选通器的端子out分别连接,第3选通器的端子0_chan与第4选通器的端子out连接。

[0029]

延迟电路的端子a

trng

、a

puf

、a

d1

、a

dclk1

、a

ctrl

、a

clk1

、a

gnd1

、a

rt

、a

rst1

、a

d2

、a

dclk2

与第1选通器的端子0_chan、第1选通器的端子1_chan、第1延迟单元的端子v

rdly1

、第1延迟单元的端子v

rdly2

、第5选通器的端子sel、第5选通器的端子0_chan、第5选通器的端子1_chan、第3选通器的端子1_chan、第3选通器的端子sel、第n延迟单元的端子v

odly1

、第n延迟单元的端子v

odly2

对应连接。

[0030]

延迟电路的端子a

c31

、

……

、延迟电路的端子a

c3i

、

……

、延迟电路的端子a

c3n

与第1延迟单元的端子v

c11

、

……

、第i延迟单元的端子v

c1i

、

……

、第n延迟单元的端子v

c1n

对应连接。

[0031]

延迟单元(509)由第1忆阻器、第1延迟单元选通器、第2延迟单元选通器、第2忆阻器组成;第1忆阻器的端子a

m1

与第1延迟单元选通器的端子0_chan、第2延迟单元选通器的端子1_chan分别连接,第2忆阻器的端子a

m1

与第1延迟单元选通器的端子1_chan、第2延迟单元选通器的端子0_chan分别连接,第1延迟单元选通器的端子sel与第2延迟单元选通器的端子sel连接。

[0032]

延迟单元的端子v

rdly1

、端子v

rdly2

、端子v

c1i

、端子v

odly1

、端子v

odly2

与第1忆阻器的端

子a

m0

、第2忆阻器的端子a

m0

、第1延迟单元选通器的端子sel、第1延迟单元选通器的端子out、第2延迟单元选通器的端子out对应连接。

[0033]

模式控制电路由n个模式控制电路选通器组成;第1模式控制电路选通器的端子sel、

……

、第i模式控制电路选通器的端子sel、

……

、第n模式控制电路选通器的端子sel分别与模式控制电路的端子a

md1

连接;模式控制电路的端子a

c11

、端子a

r21

、端子a

c21

与第1模式控制电路选通器的端子1_chan、端子0_chan、端子out对应连接,

……

,模式控制电路的端子a

c1i

、端子a

r2i

、端子a

c2i

与第i模式控制电路选通器的端子1_chan、端子0_chan、端子out对应连接,

……

,模式控制电路的端子a

c1n

、端子a

r2n

、端子a

c2n

与第n模式控制电路选通器的端子1_chan、端子0_chan、端子out对应连接。

[0034]

所述延迟电路中每个延迟单元各自的第1忆阻器和第2忆阻器的初始状态均为高阻态。

[0035]

所述的基于忆阻器的多功能puf电路的使用方法的步骤是:

[0036]

步骤1、选择工作模式

[0037]

在多功能puf电路的电压输入端子v

mode

与端子gnd之间施加电压信号u

mode

,若施加的电压信号u

mode

为高电平电压信号时,多功能puf电路处于puf工作模式;若施加的电压信号u

mode

为低电平电压信号时,多功能puf电路处于trng工作模式。

[0038]

步骤2、多功能puf电路处于puf工作模式

[0039]

步骤2.1、所有忆阻器复位

[0040]

在多功能puf电路的电压输入端子v

ctrl

、v

rst

、v

rt

、v

vdd

与端子gnd之间施加对应的高电平电压信号u

ctrl

、u

rst

、u

rt

、u

vdd

,在多功能puf电路的电压输入端子v

c1

、

……

、v

ci

、

……

、v

cn

与端子gnd之间施加对应的低电平的激励电压信号u

c1

、

……

、u

ci

、

……

、u

cn

,在多功能puf电路的电压输入端子v

puf

与端子gnd之间施加低电平的电压信号u

puf

;延迟电路中每个延迟单元各自的第1忆阻器和第2忆阻器均复位为高阻态。

[0041]

步骤2.2、施加激励,输出响应

[0042]

在多功能puf电路的电压输入端子v

puf

、v

rst

、v

ctrl

与端子gnd之间施加对应的高电平电压信号u

puf

、u

rst

、u

ctrl

,在多功能puf电路的电压输入端子v

c1

、

……

、v

ci

、

……

、v

cn

与端子gnd之间施加对应的高电平或低电平的激励电压信号u

c1

、

……

、u

ci

、

……

、u

cn

,在多功能puf电路的电压输入端子v

rst

与端子gnd之间施加低电平电压信号u

rst

;

[0043]

此时,仲裁器电路的端子v

out

输出响应电压。

[0044]

步骤3、多功能puf电路处于trng工作模式

[0045]

步骤3.1、重复步骤2.1和步骤2.2,得到一位响应。

[0046]

步骤3.2、在多功能puf电路的电压输入端子v

clk

与端子gnd之间施加低电平电压信号u

clk

,施加的低电平电压信号u

clk

的持续时间为t

dmax

(脉冲信号在延迟电路中的最大延迟时间),再于多功能puf电路的电压输入端子v

clk

与端子gnd之间施加高电平电压信号u

clk

,将步骤3.1得到的一位响应存入移位寄存器电路中。

[0047]

步骤3.3、步骤3.1和步骤3.2重复n次,每次得到的响应依次存入移位寄存器电路中。

[0048]

步骤3.4、随机比特流输出

[0049]

在多功能puf电路的电压输入端子v

trng

与端子gnd之间施加高电平电压信号u

trng

,

在多功能puf电路的电压输入端子v

ctrl

、v

rst

与端子gnd之间施加对应的低电平电压信号u

ctrl

、u

rst

,在多功能puf电路的电压输入端子v

clk

与端子gnd之间施加时钟电压信号u

clk

。

[0050]

此时,仲裁器电路的端子v

out

将不断输出随机比特流。

[0051]

由于采用上述技术方案,本发明具有如下积极效果:

[0052]

本发明只需要在现有的基于忆阻器的仲裁器puf电路上增加移位寄存器电路和模式控制电路,能使本发明具有puf和trng两种功能;由于现有的基于忆阻器的仲裁器puf电路不仅具有良好的性能指标,且结构简单和成本低,故基于忆阻器的多功能puf电路具有良好的性能指标、结构简单和成本低。

[0053]

本发明中,当基于忆阻器的多功能puf电路处于trng工作模式时,基于忆阻器的多功能puf电路能够将输出结果反馈回来作为激励信号施加在基于忆阻器的多功能puf电路上,随着时钟电压信号u

clk

不断的变化,每个延迟单元中第1忆阻器和第2忆阻器的阻值将随机的减小或增大,使基于忆阻器的多功能puf电路的输出是随机的。因此,随着时钟电压信号u

clk

不断的变化,基于忆阻器的多功能puf电路处于trng工作模式时能够不断的输出随机的比特流。

[0054]

因此,本发明具有结构简单和成本低的特点,所提供的基于忆阻器的多功能puf电路具有puf和trng两种功能,当基于忆阻器的多功能puf电路作为puf使用时具有良好的性能指标,当基于忆阻器的多功能puf电路作为trng使用时能够持续的产生真随机数。

附图说明

[0055]

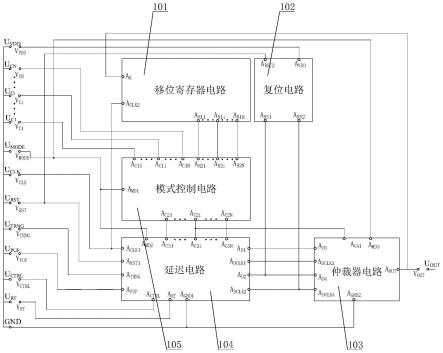

图1为本发明的一种结构示意图;

[0056]

图2为图1中移位寄存器电路101的一种结构示意图;

[0057]

图3为图1中复位电路102的一种结构示意图;

[0058]

图4为图1中仲裁器电路103的一种结构示意图;

[0059]

图5为图4中分路器404的一种结构示意图;

[0060]

图6为图1中延迟电路104的一种结构示意图;

[0061]

图7为图6中延迟单元609的一种结构示意图;

[0062]

图8为图1中模式控制电路105的一种结构示意图。

具体实施方式

[0063]

下面结合附图和具体实施方式对本发明作进一步的描述,并非对其保护范围的限制。

[0064]

实施例1

[0065]

一种基于忆阻器的多功能puf电路及其使用方法。

[0066]

所述基于忆阻器的多功能puf电路(以下简称“多功能puf电路”,下同)由移位寄存器电路101、复位电路102、仲裁器电路103、延迟电路104和模式控制电路105组成。

[0067]

如图1所示,移位寄存器电路101的端子ar与仲裁器电路103的端子v

out

连接,移位寄存器电路101的端子a

clk2

与延迟电路104的端子a

clk1

连接,移位寄存器电路101的端子a

r11

、a

r12

、

……

、a

r18

、a

r19

与模式控制电路105的端子a

r21

、a

r22

、

……

、a

r28

、a

r29

对应连接。

[0068]

如图1所示,复位电路102的端子a

rst2

与延迟电路104的端子a

rst1

连接,复位电路102

的端子a

rs1

与仲裁器电路103的端子a

d4

和延迟电路104的端子a

d2

分别连接,复位电路102的端子a

rs2

与仲裁器电路103的端子a

dclk4

和延迟电路104的端子a

dclk2

分别连接。

[0069]

如图1所示,仲裁器电路103的端子a

d3

与延迟电路104的端子a

d1

连接,仲裁器电路103的端子a

dclk3

与延迟电路104的端子a

dclk1

连接,仲裁器电路103的端子a

c41

与模式控制电路105的端子a

c25

和延迟电路104的端子a

c35

分别连接,仲裁器电路103的端子a

md3

与模式控制电路105的端子a

md1

、延迟电路104的端子a

md2

分别连接,仲裁器电路103的端子a

gnd2

与延迟电路104的端子a

gnd1

连接。

[0070]

如图1所示,延迟电路104的端子a

c31

、a

c32

、

……

、a

c38

、a

c39

与模式控制电路105的端子a

c21

、a

c22

、

……

、a

c28

、a

c29

对应连接。

[0071]

如图1所示,多功能puf电路的输入端子v

clk

、v

rst

、v

vdd

、v

mode

、gnd、v

puf

、v

trng

、v

rt

、v

ctrl

与移位寄存器电路101的端子a

clk2

、复位电路102的端子a

rst2

、复位电路102的端子a

vdd

、仲裁器电路103的端子a

md3

、仲裁器电路103的端子a

gnd2

、延迟电路104的端子a

puf

、延迟电路104的端子a

trng

、延迟电路104的端子a

rt

、延迟电路104的端子a

ctrl

对应连接。

[0072]

如图1所示,多功能puf电路的输入端子v

c1

、v

c2

、

……

、v

c8

、v

c9

与模式控制电路105的端子a

c11

、a

c12

、

……

、a

c18

、a

c19

对应连接。

[0073]

如图1所示,多功能puf电路的输出端子v

out

与仲裁器电路103的输出端子a

out

连接。

[0074]

如图2所示,所述移位寄存器电路101由9个d触发器201组成;第1d触发器201的端子d与移位寄存器电路101的端子ar连接;第1d触发器201的端子q与端子a

r11

连接、第2d触发器201的端子q与端子a

r12

连接、

……

、第8d触发器201的端子q与端子a

r18

连接、第9d触发器201的端子q与端子a

r19

连接;第1d触发器201的端子q与第2d触发器201的端子d连接、第2d触发器201的端子q与第3d触发器201的端子d连接、

……

、第8d触发器201的端子q与第9d触发器201的端子d连接;第1d触发器201的端子clk、第2d触发器201的端子clk、

……

、第8d触发器201的端子clk、第9d触发器201的端子clk与移位寄存器电路101端子a

clk2

分别连接。

[0075]

如图3所示,所述复位电路102由第1复位电路nmos管301和第2复位电路nmos管302组成,第1复位电路nmos管301的栅极和第2复位电路nmos管302的栅极与复位电路102的端子a

rst2

分别连接,第1复位电路nmos管301的漏极和第2复位电路nmos管302的漏极与复位电路102的端子a

vdd

分别连接,第1复位电路nmos管301的源级与复位电路102的端子a

rs2

连接,第2复位电路nmos管302的源级与复位电路102的端子a

rs1

连接。

[0076]

如图4所示,所述仲裁器电路103由第1仲裁器电路d触发器401、第1仲裁器电路选通器402、第2仲裁器电路选通器403、分路器404、第2仲裁器电路d触发器405组成;第1仲裁器电路d触发器401的端子q与第1仲裁器电路选通器402的端子1_chan连接,第1仲裁器电路选通器402的端子0_chan与分路器404的端子0_chan连接,第1仲裁器电路选通器402的端子out与第2仲裁器电路选通器403的端子0_chan连接,第2仲裁器电路选通器403的端子sel与分路器404的端子sel连接,第2仲裁器电路选通器403的端子1_chan与分路器404的端子1_chan连接,分路器404的端子in与第2仲裁器电路d触发器405的端子q连接。

[0077]

如图4所示,第1仲裁器电路d触发器401的端子d、端子clk与仲裁器电路103的端子a

d3

、a

dclk3

对应连接,第2仲裁器电路d触发器405的端子d、端子clk与仲裁器电路103的端子a

d4

、a

dclk4

对应连接,第1仲裁器电路d触发器402的端子sel与仲裁器电路103的端子a

c41

连接,第2仲裁器电路选通器403的端子sel、分路器404的端子sel分别与仲裁器电路103的端

子a

md3

连接。

[0078]

第2仲裁器电路选通器403的端子out与仲裁器电路103的端子a

out

连接。

[0079]

如图5所示,分路器404由第1分路器选通器501和第2分路器选通器502组成;第1分路器选通器501的端子1_chan与第2分路器选通器502的端子0_chan连接,第1分路器选通器501的端子0_chan与第2分路器选通器502的端子1_chan连接,第1分路器选通器501的端子sel与第2分路器选通器502端子sel连接。

[0080]

如图5所示,第1分路器选通器501的端子1_chan、端子sel、端子0_chan、端子out与分路器404的端子in、端子sel、端子a

gnd3

、端子1_chan对应连接,第2分路器选通器502的端子out与分路器404的端子0_chan连接。

[0081]

如图6所示,所述延迟电路104由第1选通器601、第1延迟电路分路器602、第2延迟电路分路器603、第1nmos管604、第2nmos管605、第3nmos管606、第4nmos管607、第5nmos管608、9个延迟单元609、第6nmos管610、第7nmos管611、第8nmos管612、第9nmos管613、第2选通器614、第10nmos管615、第3选通器616、第4选通器617、第5选通器618组成。

[0082]

第1延迟电路分路器602和第2延迟电路分路器603与仲裁器电路103中的分路器404相同。

[0083]

第1选通器601的端子sel与第1延迟电路分路器602的端子sel连接,第1选通器601的端子out与第1延迟电路分路器602的端子in连接,第1延迟电路分路器602的端子0_chan与第2延迟电路分路器603的端子in连接,第1延迟电路分路器602的端子1_chan与第1nmos管604的栅极、第1nmos管604的漏极、第2nmos管605的栅极、第2nmos管605的漏极分别连接,第1延迟电路分路器602的端子a

gnd3

与第2延迟电路分路器603的端子a

gnd3

、第5nmos管608的源级、第6nmos管610的源级、第9nmos管613的源级、第10nmos管615的源级、第2选通器614的端子1_chan、第4选通器617的端子0_chan、第5选通器618的端子1_chan分别连接。

[0084]

第2延迟电路分路器603的端子sel与第5延迟单元609的端子v

c15

、第2选通器614的端子sel、第4选通器617的端子sel分别连接,第2延迟电路分路器603的端子1_chan与第7nmos管611的栅极、第7nmos管611的漏极、第8nmos管612的栅极、第8nmos管612的漏极分别连接,第2延迟电路分路器603的端子0_chan与第3nmos管606的栅极、第3nmos管606的漏极、第4nmos管607的栅极、第4nmos管607的漏极分别连接,第1nmos管604的源级与第3nmos管606的源级、第5nmos管608的漏极、第1延迟单元609的端子v

rdly1

分别连接,第2nmos管605的源级与第4nmos管607的源级、第10nmos管615的漏极、第1延迟单元509的端子v

rdly2

分别连接,第7nmos管611的源级与第6nmos管610的漏极、第9延迟单元609的端子v

odly1

分别连接,第8nmos管612的源级与第9nmos管613的漏极、第9延迟单元609的端子v

odly2

分别连接,第5nmos管608的栅极与第10nmos管615的栅极、第3选通器616的端子out分别连接。

[0085]

第1延迟单元609的端子v

odly1

、端子v

odly2

与第2延迟单元609的端子v

rdly1

、端子v

rdly2

对应连接、第2延迟单元609的端子v

odly1

、端子v

odly2

与第3延迟单元609的端子v

rdly1

、端子v

rdly2

对应连接、

……

、第7延迟单元609的端子v

odly1

、端子v

odly2

与第8延迟单元609的端子v

rdly1

、端子v

rdly2

对应连接、第8延迟单元609的端子v

odly1

、端子v

odly2

与第9延迟单元609的端子v

rdly1

、端子v

rdly2

对应连接;第6nmos管610的栅极与第9nmos管613的栅极、第2选通器614的端子out分别连接,第2选通器614的端子0_chan与第4选通器617的端子1_chan、第5选通器618的端子out分别连接,第3选通器616的端子0_chan与第4选通器617的端子out连接。

[0086]

如图6所示,延迟电路104的端子a

trng

、a

puf

、a

d1

、a

dclk1

、a

ctrl

、a

clk1

、a

gnd1

、a

rt

、a

rst1

、a

d2

、a

dclk2

与第1选通器601的端子0_chan、第1选通器601的端子1_chan、第1延迟单元609的端子v

rdly1

、第1延迟单元609的端子v

rdly2

、第5选通器618的端子sel、第5选通器618的端子0_chan、第5选通器618的端子1_chan、第3选通器616的端子1_chan、第3选通器616的端子sel、第9延迟单元609的端子v

odly1

、第9延迟单元609的端子v

odly2

对应连接。

[0087]

延迟电路104的端子a

c31

、延迟电路104的端子a

c32

、

……

、延迟电路104的端子a

c38

、延迟电路104的端子a

c39

与第1延迟单元609的端子v

c11

、第1延迟单元609的端子v

c12

、

……

、第8延迟单元609的端子v

c18

、第9延迟单元609的端子v

c19

对应连接。

[0088]

如图7所示,延迟单元509由第1忆阻器701、第1延迟单元选通器702、第2延迟单元选通器703、第2忆阻器704组成;第1忆阻器701的端子a

m1

与第1延迟单元选通器702的端子0_chan、第2延迟单元选通器703的端子1_chan分别连接,第2忆阻器704的端子a

m1

与第1延迟单元选通器702的端子1_chan、第2延迟单元选通器703的端子0_chan分别连接,第1延迟单元选通器702的端子sel与第2延迟单元选通器703的端子sel连接。

[0089]

如图7所示,延迟单元609的端子v

rdly1

、端子v

rdly2

、端子v

c1i

、端子v

odly1

、端子v

odly2

与第1忆阻器701的端子a

m0

、第2忆阻器704的端子a

m0

、第1延迟单元选通器702的端子sel、第1延迟单元选通器702的端子out、第2延迟单元选通器703的端子out对应连接。

[0090]

如图8所示,模式控制电路105由9个模式控制电路选通器801组成;第1模式控制电路选通器801的端子sel、第2模式控制电路选通器801的端子sel、

……

、第8模式控制电路选通器801的端子sel、第9模式控制电路选通器801的端子sel分别与模式控制电路105的端子a

md1

连接;模式控制电路105的端子a

c11

、端子a

r21

、端子a

c21

与第1模式控制电路选通器801的端子1_chan、端子0_chan、端子out对应连接,模式控制电路105的端子a

c12

、端子a

r22

、端子a

c22

与第2模式控制电路选通器801的端子1_chan、端子0_chan、端子out对应连接,

……

,模式控制电路105的端子a

c18

、端子a

r28

、端子a

c28

与第8模式控制电路选通器801的端子1_chan、端子0_chan、端子out对应连接,模式控制电路105的端子a

c19

、端子a

r29

、端子a

c29

与第9模式控制电路选通器801的端子1_chan、端子0_chan、端子out对应连接。

[0091]

所述延迟电路104中每个延迟单元609各自的第1忆阻器701和第2忆阻器704的初始状态均为高阻态。

[0092]

一种基于忆阻器的多功能puf电路的使用方法的步骤是:

[0093]

步骤1、选择工作模式

[0094]

在多功能puf电路的电压输入端子v

mode

与端子gnd之间施加电压信号u

mode

,若施加的电压信号u

mode

为3.3v的高电平电压信号时,多功能puf电路处于puf工作模式;若施加的电压信号u

mode

为0v的低电平电压信号时,多功能puf电路处于trng工作模式。

[0095]

步骤2、多功能puf电路处于puf工作模式

[0096]

步骤2.1、所有忆阻器复位

[0097]

在多功能puf电路的电压输入端子v

ctrl

、v

rst

、v

rt

、v

vdd

与端子gnd之间施加对应的高电平电压信号u

ctrl

=3.3v、u

rst

=3.3v、u

rt

=3.3v、u

vdd

=3.3v,在多功能puf电路的电压输入端子v

c1

、v

c2

、

……

、v

c8

、v

c9

与端子gnd之间施加对应的低电平的激励电压信号u

c1

=0v、u

c2

=0v、

……

、u

c8

=0v、u

c9

=0v,在多功能puf电路的电压输入端子v

puf

与端子gnd之间施加低电平的电压信号u

puf

=0v。

[0098]

步骤2.1中延迟电路104中每个延迟单元609各自的第1忆阻器701和第2忆阻器704均复位为高阻态:

[0099]

第1延迟单元609中第1忆阻器701、第2延迟单元609中第1忆阻器701、

……

、第8延迟单元609中第1忆阻器701、第9延迟单元609中第1忆阻器的阻值依次为11466ω、10652ω、10476ω、8614ω、9324ω、9993ω、10516ω、11899ω、8861ω。

[0100]

第1延迟单元609中第2忆阻器704、第2延迟单元609中第2忆阻器704、

……

、第8延迟单元609中第2忆阻器704、第9延迟单元604中第2忆阻器的阻值依次为10861ω、9473ω、10167ω、9546ω、11373ω、10179ω、9999ω、11884ω、11030ω。

[0101]

步骤2.2、施加激励,输出响应

[0102]

在多功能puf电路的电压输入端子v

puf

、v

rst

、v

ctrl

与端子gnd之间施加对应的高电平电压信号u

puf

=3.3v、u

rst

=3.3v、u

ctrl

=3.3v,在多功能puf电路的电压输入端子v

c1

、v

c2

、

……

、v

c8

、v

c9

与端子gnd之间施加对应的激励电压信号u

c1

=0v、u

c2

=3.3v、u

c3

=3.3v、u

c4

=0v、u

c5

=0v、u

c6

=3.3v、u

c7

=3.3v、u

c8

=3.3v、u

c9

=0v、在多功能puf电路的电压输入端子v

rst

与端子gnd之间施加低电平电压信号u

rst

=0v。

[0103]

在步骤2.2中,延迟电路104根据输入的激励电压信号使第1延迟单元609中第1忆阻器701与第2延迟单元609中第1忆阻器701、第3延迟单元609中第2忆阻器704、第4延迟单元609中第1忆阻器701、第5延迟单元609中第1忆阻器701、第6延迟单元609中第1忆阻器701、第7延迟单元609中第2忆阻器704、第8延迟单元609中第1忆阻器701、第9延迟单元609中第2忆阻器704串联,第1延迟单元609中第2忆阻器704与第2延迟单元609中第2忆阻器704、第3延迟单元609中第1忆阻器701、第4延迟单元609中第2忆阻器704、第5延迟单元609中第2忆阻器704、第6延迟单元609中第2忆阻器704、第7延迟单元609中第1忆阻器701、第8延迟单元609中第2忆阻器702、第9延迟单元609中第1忆阻器701串联,延迟电路104中一组串联的忆阻器与第6nmos管610的寄生电容组成rc延迟电路,延迟电路104中另一组串联的忆阻器与第9个nmos管613的寄生电容组成rc延迟电路,高电平电压信号u

puf

经过延迟电路104中的两条rc延迟电路后会产生随机延迟,延迟时间分别为694.109ns,702.4ns;此时,仲裁器电路103的端子v

out

输出响应电压为3.3v。

[0104]

步骤3、多功能puf电路处于trng工作模式

[0105]

步骤3.1、重复步骤2.1和步骤2.2,得到一位响应电压。

[0106]

步骤3.2、在多功能puf电路的电压输入端子v

clk

与端子gnd之间施加低电平电压信号u

clk

=0v,施加的低电平电压信号u

clk

的持续时间为t

dmax

(脉冲信号在延迟电路104中的最大延迟时间),再于多功能puf电路的电压输入端子v

clk

与端子gnd之间施加高电平电压信号u

clk

=3.3v;将步骤3.1得到的一位响应存入移位寄存器电路101中。

[0107]

步骤3.3、将步骤3.1和步骤3.2重复9次,每次得到的响应依次存入移位寄存器电路101中。

[0108]

本步骤中,每次重复过程中向电压输入端子v

c1

、v

c2

、

……

、v

c8

、v

c9

施加的激励电压信号:

[0109]

第1次施加的激励电压信号对应地为u

c1

=0v、u

c2

=0v、u

c3

=0v、u

c4

=0v、u

c5

=0v、u

c6

=3.3v、u

c7

=0v、u

c8

=3.3v、u

c9

=3.3v;

[0110]

第2次施加的激励电压信号对应地为u

c1

=0v、u

c2

=0v、u

c3

=0v、u

c4

=3.3v、u

c5

=

0v、u

c6

=0v、u

c7

=3.3v、u

c8

=0v、u

c9

=3.3v;

[0111]

第3次施加的激励电压信号对应地为u

c1

=3.3v、u

c2

=0v、u

c3

=3.3v、u

c4

=0v、u

c5

=0v、u

c6

=0v、u

c7

=0v、u

c8

=3.3v、u

c9

=3.3v;

[0112]

第4次施加的激励电压信号对应地为u

c1

=3.3v、u

c2

=0v、u

c3

=0v、u

c4

=0v、u

c5

=0v、u

c6

=3.3v、u

c7

=0v、u

c8

=3.3v、u

c9

=0v;

[0113]

第5次施加的激励电压信号对应地为u

c1

=0v、u

c2

=3.3v、u

c3

=3.3v、u

c4

=0v、u

c5

=0v、u

c6

=3.3v、u

c7

=3.3v、u

c8

=3.3v、u

c9

=0v;

[0114]

第6次施加的激励电压信号对应地为u

c1

=0v、u

c2

=3.3v、u

c3

=3.3v、u

c4

=3.3v、u

c5

=0v、u

c6

=3.3v、u

c7

=3.3v、u

c8

=3.3v、u

c9

=3.3v;

[0115]

第7次施加的激励电压信号对应地为u

c1

=0v、u

c2

=3.3v、u

c3

=3.3v、u

c4

=0v、u

c5

=0v、u

c6

=0v、u

c7

=3.3v、u

c8

=3.3v、u

c9

=3.3v;

[0116]

第8次施加的激励电压信号对应地为u

c1

=0v、u

c2

=3.3v、u

c3

=0v、u

c4

=3.3v、u

c5

=3.3v、u

c6

=0v、u

c7

=3.3v、u

c8

=0v、u

c9

=0v;

[0117]

第9次施加的激励电压信号对应地为u

c1

=0v、u

c2

=3.3v、u

c3

=0v、u

c4

=3.3v、u

c5

=0v、u

c6

=3.3v、u

c7

=3.3v、u

c8

=0v、u

c9

=0v。

[0118]

将步骤3.1重复9次,得到的响应电压信号依次为:第1次得到的响应电压信号为v

out

=0v;第2次得到的响应电压信号为v

out

=3.3v;第3次得到的响应电压信号为v

out

=0v;第4次得到的响应电压信号为v

out

=0v;第5次得到的响应电压信号为v

out

=0v;第6次得到的响应电压信号为v

out

=3.3v;第7次得到的响应电压信号为v

out

=0v;第8次得到的响应电压信号为v

out

=3.3v;第9次得到的响应电压信号为v

out

=3.3v。

[0119]

此时,移位寄存器电路101端子a

r11

、

……

、a

r1i

、

……

、a

r19

输出的电压信号对应地为a

r11

=0v、a

r12

=3.3v、a

r13

=0v、a

r14

=0v、a

r15

=0v、a

r16

=3.3v、a

r17

=0v、a

r18

=3.3v、a

r19

=3.3v。

[0120]

步骤3.4、随机比特流输出

[0121]

在多功能puf电路的电压输入端子v

trng

与端子gnd之间施加高电平电压信号u

trng

=3.3v,在多功能puf电路的电压输入端子v

ctrl

、v

rst

与端子gnd之间施加对应的低电平电压信号u

ctrl

=0v、u

rst

=0v,在多功能puf电路的电压输入端子v

clk

与端子gnd之间施加频率为1000khz的时钟电压信号u

clk

。

[0122]

本步骤中,延迟电路104中每个延迟单元609各自的第1忆阻器701和第2忆阻器704的阻值会根据移位寄存器电路101端子a

r15

输出的电压信号变化而变化。若移位寄存器电路101端子a

r15

输出的电压信号a

r15

=3.3v,则延迟电路104中每个延迟单元609各自的第1忆阻器701和第2忆阻器704的阻值会随机增大;若移位寄存器电路101端子a

r15

输出的电压信号a

r15

=0v,则延迟电路104中每个延迟单元609各自的第1忆阻器701和第2忆阻器704的阻值会随机减小。

[0123]

若时钟电压信号u

clk

=3.3v时,延迟电路104中每个延迟单元609各自的第1忆阻器701和第2忆阻器704的阻值会随机改变;若时钟电压信号u

clk

=0v时,仲裁器电路103的端子v

out

将输出一位响应,若时钟电压信号由u

clk

=0v变为u

clk

=3.3v时,将仲裁器电路103的端子v

out

输出的一位响应电压存入到移位寄存器电路101中。随着时钟电压信号u

clk

的不断变化,仲裁器电路103的端子v

out

将不断输出随机比特流。当时钟电压信号u

clk

经过20个时钟周

期后,仲裁器电路103的端子v

out

将输出20位随机比特流,仲裁器电路103的端子v

out

将输出20位随机比特流。

[0124]

所述20位随机比特流依次为:

[0125]

第1个比特流为u

out

=0v;第2个比特流为u

out

=0v;第3个比特流为u

out

=3.3v;第4个比特流为u

out

=3.3v;第5个比特流为u

out

=0v;第6个比特流为u

out

=0v;第7个比特流为u

out

=3.3v;第8个比特流为u

out

=0v;第9个比特流为u

out

=0v;第10个比特流为u

out

=3.3v;第11个比特流为u

out

=3.3v;第12个比特流为u

out

=3.3v;第13个比特流为u

out

=3.3v;第14个比特流为u

out

=3.3v;第15个比特流为u

out

=0v;第16个比特流为u

out

=3.3v;第17个比特流为u

out

=0v;第18个比特流为u

out

=0v;第19个比特流为u

out

=3.3v;第20个比特流为u

out

=3.3v。

[0126]

实施例2

[0127]

一种基于忆阻器的多功能puf电路及其使用方法。

[0128]

所述基于忆阻器的多功能puf电路由移位寄存器电路101、复位电路102、仲裁器电路103、延迟电路104和模式控制电路105组成。

[0129]

如图1所示,移位寄存器电路101的端子ar与仲裁器电路103的端子v

out

连接,移位寄存器电路101的端子a

clk2

与延迟电路104的端子a

clk1

连接,移位寄存器电路101的端子a

r11

、a

r12

、a

r13

与模式控制电路105的端子a

r21

、a

r22

、a

r23

对应连接。

[0130]

如图1所示,复位电路102的端子a

rst2

与延迟电路104的端子a

rst1

连接,复位电路102的端子a

rs1

与仲裁器电路103的端子a

d4

和延迟电路104的端子a

d2

分别连接,复位电路102的端子a

rs2

与仲裁器电路103的端子a

dclk4

和延迟电路104的端子a

dclk2

分别连接。

[0131]

如图1所示,仲裁器电路103的端子a

d3

与延迟电路104的端子a

d1

连接,仲裁器电路103的端子a

dclk3

与延迟电路104的端子a

dclk1

连接,仲裁器电路103的端子a

c41

与模式控制电路105的端子a

c22

和延迟电路104的端子a

c32

分别连接,仲裁器电路103的端子a

md3

与模式控制电路105的端子a

md1

、延迟电路104的端子a

md2

分别连接,仲裁器电路103的端子a

gnd2

与延迟电路104的端子a

gnd1

连接。

[0132]

如图1所示,延迟电路104的端子a

c31

、a

c32

、a

c33

与模式控制电路105的端子a

c21

、a

c22

、a

c23

对应连接。

[0133]

如图1所示,多功能puf电路的输入端子v

clk

、v

rst

、v

vdd

、v

mode

、gnd、v

puf

、v

trng

、v

rt

、v

ctrl

与移位寄存器电路101的端子a

clk2

、复位电路102的端子a

rst2

、复位电路102的端子a

vdd

、仲裁器电路103的端子a

md3

、仲裁器电路103的端子a

gnd2

、延迟电路104的端子a

puf

、延迟电路104的端子a

trng

、延迟电路104的端子a

rt

、延迟电路104的端子a

ctrl

对应连接。

[0134]

如图1所示,多功能puf电路的输入端子v

c1

、v

c2

、v

c3

与模式控制电路105的端子a

c11

、a

c12

、a

c13

对应连接。

[0135]

如图1所示,多功能puf电路的输出端子v

out

与仲裁器电路103的输出端子a

out

连接。

[0136]

如图2所示,所述移位寄存器电路101由3个d触发器201组成,第1d触发器201的端子d与移位寄存器电路101的端子ar连接;第1d触发器201的端子q与端子a

r11

连接、第2d触发器201的端子q与端子a

r12

连接、第3d触发器201的端子q与端子a

r13

连接;第1d触发器201的端子q与第2d触发器201的端子d连接、第2d触发器201的端子q与第3d触发器201的端子d连接;第1d触发器201的端子clk、第2d触发器201的端子clk、第3d触发器201的端子clk与移位寄

存器电路101端子a

clk2

分别连接。

[0137]

如图3所示,所述复位电路102由第1复位电路nmos管301和第2复位电路nmos管302组成,第1复位电路nmos管301的栅极和第2复位电路nmos管302的栅极与复位电路102的端子a

rst2

分别连接,第1复位电路nmos管301的漏极和第2复位电路nmos管302的漏极与复位电路102的端子a

vdd

分别连接,第1复位电路nmos管301的源级与复位电路102的端子a

rs2

连接,第2复位电路nmos管302的源级与复位电路102的端子a

rs1

连接。

[0138]

如图4所示,所述仲裁器电路103由第1仲裁器电路d触发器401、第1仲裁器电路选通器402、第2仲裁器电路选通器403、分路器404、第2仲裁器电路d触发器405组成;第1仲裁器电路d触发器401的端子q与第1仲裁器电路选通器402的端子1_chan连接,第1仲裁器电路选通器402的端子0_chan与分路器404的端子0_chan连接,第1仲裁器电路选通器402的端子out与第2仲裁器电路选通器403的端子0_chan连接,第2仲裁器电路选通器403的端子sel与分路器404的端子sel连接,第2仲裁器电路选通器403的端子1_chan与分路器404的端子1_chan连接,分路器404的端子in与第2仲裁器电路d触发器405的端子q连接。

[0139]

如图4所示,第1仲裁器电路d触发器401的端子d、端子clk与仲裁器电路103的端子a

d3

、a

dclk3

对应连接,第2仲裁器电路d触发器405的端子d、端子clk与仲裁器电路103的端子a

d4

、a

dclk4

对应连接,第1仲裁器电路d触发器402的端子sel与仲裁器电路103的端子a

c41

连接,第2仲裁器电路选通器403的端子sel、分路器404的端子sel分别与仲裁器电路103的端子a

md3

连接。

[0140]

第2仲裁器电路选通器403的端子out与仲裁器电路103的端子a

out

连接。

[0141]

如图5所示,分路器404由第1分路器选通器501和第2分路器选通器502组成;第1分路器选通器501的端子1_chan与第2分路器选通器502的端子0_chan连接,第1分路器选通器501的端子0_chan与第2分路器选通器502的端子1_chan连接,第1分路器选通器501的端子sel与第2分路器选通器502端子sel连接。

[0142]

如图5所示,第1分路器选通器501的端子1_chan、端子sel、端子0_chan、端子out与分路器404的端子in、端子sel、端子a

gnd3

、端子1_chan对应连接,第2分路器选通器502的端子out与分路器404的端子0_chan连接。

[0143]

如图6所示,所述延迟电路104由第1选通器601、第1延迟电路分路器602、第2延迟电路分路器603、第1nmos管604、第2nmos管605、第3nmos管606、第4nmos管607、第5nmos管608、3个延迟单元609、第6nmos管610、第7nmos管611、第8nmos管612、第9nmos管613、第2选通器614、第10nmos管615、第3选通器616、第4选通器617、第5选通器618组成。

[0144]

第1延迟电路分路器602和第2延迟电路分路器603与仲裁器电路103中的分路器404相同。

[0145]

第1选通器601的端子sel与第1延迟电路分路器602的端子sel连接,第1选通器601的端子out与第1延迟电路分路器602的端子in连接,第1延迟电路分路器602的端子0_chan与第2延迟电路分路器603的端子in连接,第1延迟电路分路器602的端子1_chan与第1nmos管604的栅极、第1nmos管604的漏极、第2nmos管605的栅极、第2nmos管605的漏极分别连接,第1延迟电路分路器602的端子a

gnd3

与第2延迟电路分路器603的端子a

gnd3

、第5nmos管608的源级、第6nmos管610的源级、第9nmos管613的源级、第10nmos管615的源级、第2选通器614的端子1_chan、第4选通器617的端子0_chan、第5选通器618的端子1_chan分别连接。

[0146]

第2延迟电路分路器603的端子sel与第2延迟单元609的端子v

c12

、第2选通器614的端子sel、第4选通器617的端子sel分别连接,第2延迟电路分路器603的端子1_chan与第7nmos管611的栅极、第7nmos管611的漏极、第8nmos管612的栅极、第8nmos管612的漏极分别连接,第2延迟电路分路器603的端子0_chan与第3nmos管606的栅极、第3nmos管606的漏极、第4nmos管607的栅极、第4nmos管607的漏极分别连接,第1nmos管604的源级与第3nmos管606的源级、第5nmos管608的漏极、第1延迟单元609的端子v

rdly1

分别连接,第2nmos管605的源级与第4nmos管607的源级、第10nmos管615的漏极、第1延迟单元509的端子v

rdly2

分别连接,第7nmos管611的源级与第6nmos管610的漏极、第n延迟单元609的端子v

odly1

分别连接,第8nmos管612的源级与第9nmos管613的漏极、第n延迟单元609的端子v

odly2

分别连接,第5nmos管608的栅极与第10nmos管615的栅极、第3选通器616的端子out分别连接,第1延迟单元609的端子v

odly1

、端子v

odly2

与第2延迟单元609的端子v

rdly1

、端子v

rdly2

对应连接、第2延迟单元609的端子v

odly1

、端子v

odly2

与第3延迟单元609的端子v

rdly1

、端子v

rdly2

对应连接,第6nmos管610的栅极与第9nmos管613的栅极、第2选通器614的端子out分别连接,第2选通器614的端子0_chan与第4选通器617的端子1_chan、第5选通器618的端子out分别连接,第3选通器616的端子0_chan与第4选通器617的端子out连接。

[0147]

如图6所示,延迟电路104的端子a

trng

、a

puf

、a

d1

、a

dclk1

、a

ctrl

、a

clk1

、a

gnd1

、a

rt

、a

rst1

、a

d2

、a

dclk2

与第1选通器601的端子0_chan、第1选通器601的端子1_chan、第1延迟单元609的端子v

rdly1

、第1延迟单元609的端子v

rdly2

、第5选通器618的端子sel、第5选通器618的端子0_chan、第5选通器618的端子1_chan、第3选通器616的端子1_chan、第3选通器616的端子sel、第n延迟单元609的端子v

odly1

、第n延迟单元609的端子v

odly2

对应连接。

[0148]

延迟电路104的端子a

c31

、延迟电路104的端子a

c32

、延迟电路104的端子a

c33

与第1延迟单元609的端子v

c11

、第2延迟单元609的端子v

c12

、第3延迟单元609的端子v

c13

对应连接。

[0149]

如图7所示,延迟单元509由第1忆阻器701、第1延迟单元选通器702、第2延迟单元选通器703、第2忆阻器704组成;第1忆阻器701的端子a

m1

与第1延迟单元选通器702的端子0_chan、第2延迟单元选通器703的端子1_chan分别连接,第2忆阻器704的端子a

m1

与第1延迟单元选通器702的端子1_chan、第2延迟单元选通器703的端子0_chan分别连接,第1延迟单元选通器702的端子sel与第2延迟单元选通器703的端子sel连接。

[0150]

如图7所示,延迟单元609的端子v

rdly1

、端子v

rdly2

、端子v

c1i

、端子v

odly1

、端子v

odly2

与第1忆阻器701的端子a

m0

、第2忆阻器704的端子a

m0

、第1延迟单元选通器702的端子sel、第1延迟单元选通器702的端子out、第2延迟单元选通器703的端子out对应连接。

[0151]

如图8所示,模式控制电路105由n个模式控制电路选通器801组成;第1模式控制电路选通器801的端子sel、第2模式控制电路选通器801的端子sel、第3模式控制电路选通器801的端子sel分别与模式控制电路105的端子a

md1

连接;模式控制电路105的端子a

c11

、端子a

r21

、端子a

c21

与第1模式控制电路选通器801的端子1_chan、端子0_chan、端子out对应连接,模式控制电路105的端子a

c12

、端子a

r22

、端子a

c22

与第2模式控制电路选通器801的端子1_chan、端子0_chan、端子out对应连接,模式控制电路105的端子a

c13

、端子a

r23

、端子a

c23

与第3模式控制电路选通器801的端子1_chan、端子0_chan、端子out对应连接。

[0152]

所述基于忆阻器的多功能puf电路的使用方法的步骤是:

[0153]

步骤1、选择工作模式

[0154]

在多功能puf电路的电压输入端子v

mode

与端子gnd之间施加电压信号u

mode

,若施加的电压信号u

mode

=3.3v时,多功能puf电路处于puf工作模式;若施加的电压信号u

mode

=0v时,多功能puf电路处于trng工作模式。

[0155]

步骤2、多功能puf电路处于puf工作模式

[0156]

步骤2.1、所有忆阻器复位

[0157]

在多功能puf电路的电压输入端子v

ctrl

、v

rst

、v

rt

、v

vdd

与端子gnd之间施加对应的高电平电压信号u

ctrl

=3.3v、u

rst

=3.3v、u

rt

=3.3v、u

vdd

=3.3v,在多功能puf电路的电压输入端子v

c1

、v

c2

、v

c3

与端子gnd之间施加对应的低电平的激励电压信号u

c1

=0v、u

c2

=0v、u

c3

=0v,在多功能puf电路的电压输入端子v

puf

与端子gnd之间施加低电平的电压信号u

puf

。

[0158]

延迟电路104中每个延迟单元609各自的第1忆阻器701和第2忆阻器704均复位为高阻态,其中:

[0159]

第1延迟单元609中第1忆阻器701、第2延迟单元609中第1忆阻器701、第3延迟单元609中第1忆阻器的阻值依次为8567ω、11663ω、11838ω。

[0160]

第1延迟单元609中第2忆阻器704、第2延迟单元609中第2忆阻器704、第3延迟单元604中第2忆阻器的阻值依次为9687ω、11169ω、10623ω。

[0161]

步骤2.2、施加激励,输出响应

[0162]

在多功能puf电路的电压输入端子v

puf

、v

rst

、v

ctrl

与端子gnd之间施加对应的高电平电压信号u

puf

=3.3v、u

rst

=3.3v、u

ctrl

=3.3v,在多功能puf电路的电压输入端子v

c1

、v

c2

、v

c3

与端子gnd之间施加对应的高电平或低电平的激励电压信号u

c1

=3.3v、u

c2

=0v、u

c3

=3.3v,在多功能puf电路的电压输入端子v

rst

与端子gnd之间施加低电平电压信号u

rst

=0v;

[0163]

本步骤中,延迟电路104根据输入的激励电压信号,使得:

[0164]

第1延迟单元609中第1忆阻器701与第2延迟单元609中第2忆阻器704、第3延迟单元609中第2忆阻器704串联,第1延迟单元609中第2忆阻器704与第2延迟单元609中第1忆阻器701、第3延迟单元609中第1忆阻器701串联。

[0165]

延迟电路104中一组串联的忆阻器与第6nmos管610的寄生电容组成rc延迟电路;延迟电路104中另一组串联的忆阻器与第9个nmos管613的寄生电容组成rc延迟电路;高电平电压信号u

puf

经过延迟电路104中的两条rc延迟电路后会产生随机延迟,延迟时间分别为229.063ns,247.316ns。此时仲裁器电路103的端子v

out

输出响应电压为3.3v。

[0166]

步骤3、多功能puf电路处于trng工作模式

[0167]

步骤3.1、重复步骤2.1和步骤2.2,得到一位响应电压。

[0168]

步骤3.2、在多功能puf电路的电压输入端子v

clk

与端子gnd之间施加低电平电压信号u

clk

=0v,施加的低电平电压信号u

clk

的持续时间为t

dmax

脉冲信号在延迟电路104中的最大延迟时间,再于多功能puf电路的电压输入端子v

clk

与端子gnd之间施加高电平电压信号u

clk

=3.3v,将步骤3.1得到的一位响应存入移位寄存器电路101中。

[0169]

步骤3.3、将步骤3.1和步骤3.2重复3次,每次得到的响应依次存入移位寄存器电路101中。

[0170]

本步骤中,每次重复过程中向电压输入端子v

c1

、v

c2

、v

c3

施加的激励电压信号:

[0171]

第1次施加的激励电压信号对应地为u

c1

=3.3v、u

c2

=0v、u

c3

=0v;

[0172]

第2次施加的激励电压信号对应地为u

c1

=0v、u

c2

=3.3v、u

c3

=3.3v;

[0173]

第3次施加的激励电压信号对应地为u

c1

=3.3v、u

c2

=0v、u

c3

=3.3v。

[0174]

步骤3.1重复3次得到的响应电压信号依次为:

[0175]

第1次得到的响应电压信号为v

out

=0v、第2次得到的响应电压信号为v

out

=3.3v、第3次得到的响应电压信号为v

out

=3.3v。

[0176]

此时,移位寄存器电路101端子a

r11

、a

r12

、a

r13

输出对应的电压信号为a

r11

=0v、a

r12

=3.3v、a

r13

=3.3v。

[0177]

步骤3.4、随机比特流输出

[0178]

在多功能puf电路的电压输入端子v

trng

与端子gnd之间施加高电平电压信号u

trng

=3.3v,在多功能puf电路的电压输入端子、v

ctrl

、v

rst

与端子gnd之间施加对应的低电平电压信号u

ctrl

=0v、u

rst

=0v,在多功能puf电路的电压输入端子v

clk

与端子gnd之间施加频率为1000khz的时钟电压信号u

clk

。

[0179]

本步骤中,延迟电路104中每个延迟单元609各自的第1忆阻器701和第2忆阻器704的阻值会根据移位寄存器电路101端子a

r12

输出的电压信号变化而变化。若移位寄存器电路101端子a

r12

输出的电压信号a

r12

=3.3v,则延迟电路104中每个延迟单元609各自的第1忆阻器701和第2忆阻器704的阻值会随机增大;若移位寄存器电路101端子a

r12

输出的电压信号a

r12

=0v,则延迟电路104中每个延迟单元609各自的第1忆阻器701和第2忆阻器704的阻值会随机减小。

[0180]

若时钟电压信号u

clk

=3.3v时,延迟电路104中每个延迟单元609各自的第1忆阻器701和第2忆阻器704的阻值会随机改变;若时钟电压信号u

clk

=0v时,仲裁器电路103的端子v

out

将输出一位响应,若时钟电压信号由u

clk

=0v变为u

clk

=3.3v时,将仲裁器电路103的端子v

out

输出的一位响应电压存入到移位寄存器电路101中。随着时钟电压信号u

clk

的不断变化,仲裁器电路103的端子v

out

将不断输出随机比特流。当时钟电压信号u

clk

经过20个时钟周期后,仲裁器电路103的端子v

out

将输出20位随机比特流,仲裁器电路103的端子v

out

将输出20位随机比特流。

[0181]

所述20位随机比特流依次为:

[0182]

第1个比特流为u

out

=0v;第2个比特流为u

out

=3.3v;第3个比特流为u

out

=0v;第4个比特流为u

out

=0v;第5个比特流为u

out

=0v;第6个比特流为u

out

=0v;第7个比特流为u

out

=3.3v;第8个比特流为u

out

=3.3v;第9个比特流为u

out

=0v;第10个比特流为u

out

=3.3v;第11个比特流为u

out

=3.3v;第12个比特流为u

out

=3.3v;第13个比特流为u

out

=3.3v;第14个比特流为u

out

=0v;第15个比特流为u

out

=3.3v;第16个比特流为u

out

=3.3v;第17个比特流为u

out

=0v;第18个比特流为u

out

=0v;第19个比特流为u

out

=3.3v;第20个比特流为u

out

=0v。

[0183]

本具体实施方式具有如下积极效果:

[0184]

本具体实施方式只需要在现有的基于忆阻器的仲裁器puf电路上增加移位寄存器电路101和模式控制电路105,能使本具体实施方式具有puf和trng两种功能;由于现有的基于忆阻器的仲裁器puf电路不仅具有良好的性能指标,且结构简单和成本低,故基于忆阻器的多功能puf电路具有良好的性能指标、结构简单和成本低。

[0185]

本具体实施方式中,当基于忆阻器的多功能puf电路处于trng工作模式时,基于忆阻器的多功能puf电路能够将输出结果反馈回来作为激励信号施加在基于忆阻器的多功能

puf电路上,随着时钟电压信号u

clk

不断的变化,每个延迟单元609中第1忆阻器701和第2忆阻器704的阻值将随机的减小或增大,使基于忆阻器的多功能puf电路的输出是随机的。因此,基于忆阻器的多功能puf电路处于trng工作模式时能够不断的输出随机的比特流。

[0186]

因此,本具体实施方式具有结构简单和成本低的特点,所提供的基于忆阻器的多功能puf电路具有puf和trng两种功能,当基于忆阻器的多功能puf电路作为puf使用时具有良好的性能指标,当基于忆阻器的多功能puf电路作为trng使用时能够持续的产生真随机数。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1