以太网寄存器级电路软硬件测试验证平台的制作方法

1.本发明涉及一种以太网寄存器级电路软硬件测试验证平台,本发明涉及软硬件之间数据交互的验证,通过微控制器和物理层收发器构建一个直连的以太网寄存器级的软硬件测试验证平台。

背景技术:

2.随着技术发展,业界对工业芯片和电路的需求日益增多,但设计一款电路及其生产测试,需要投入大量的金钱和时间。随着制造工艺的不断提升,半导体产业的发展对照摩尔定律越来越难实现。针对公司设计的一款带mac层的arm电路需要进行寄存器级的功能测试验证。

技术实现要素:

3.本发明的目的是提供一种以太网寄存器级电路软硬件测试平台,来解决上述问题。

4.为了实现上述目的,本发明采用的技术方案是:

5.一种自以太网寄存器级电路软硬件测试平台,包括两路调试串口;第一路调试串口包括依次连接的接口、外部phy和变压器,第一路调试串口的接口同待验证电路连接;第二路调试串口包括依次连接的单片机、外部phy和变压器;两路调试串口都接到路由器,与上位机进行通讯测试。

6.本发明技术方案的进一步改进为,单片机为stm32f407、外部phy为芯片dp83848、接口为rmii或mii。

7.由于采用了上述技术方案,本发明取得的技术效果有:

8.本发明是一种以太网寄存器级的软硬件测试验证平台,该以太网寄存器级软硬件测试验证平台不仅可以验证正确发送和接收的数据,而且可以验证错误发送和接收的数据,来对网络模块充分验证。

9.该平台可用于进行数据链路层验证,不仅可以构建正确的协议帧数据,还可以构建错误的协议帧数据,以全面验证网络模块。

附图说明

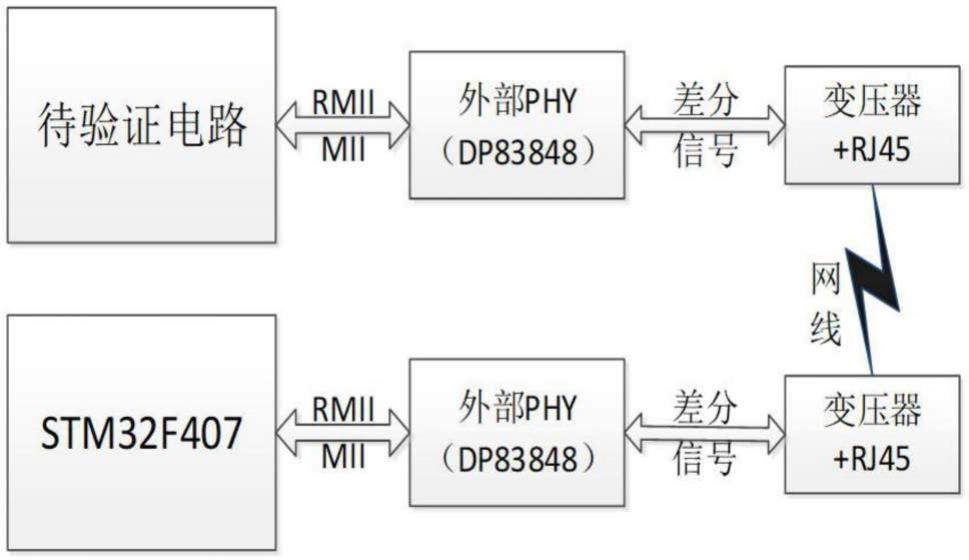

10.图1是本发明硬件测试验证平台整体框架示意图;

11.图2是本发明是带有dma、mac802.3控制器的stm32f107示意图;

12.图3是本发明mii接口示意图;

13.图4是本发明mii接口示意图;

14.图5是本发明dp83848原理图;

15.图6是本发明频率选择原理图;

16.图7是本发明测试时硬件连接示意框图。

具体实施方式

17.为使本发明实现的技术手段、创作特征、达成目的与功效易于明白了解,下面结合具体实施方式,进一步阐述本发明。

18.本发明旨在构建一个以太网以寄存器级的软硬件测试验证平台。

19.电路设计更多关注物理层、数据链路层。带mac层的arm电路,不仅需要验证正确发送接受数据,同时需要验证错误和接收数据。而发送和接收错误数据是电路实验的重点。因此构建一个寄存器级别的软硬件测试验证平台成为验证电路的一个迫切需求。

20.构建一个ieee802.3太网寄存器级软硬件测试验证平台包含smi、rmii、mii部分,mac部分,dma验证。

21.ieee802.3以太网寄存器级软硬件测试验证平台:

22.如图1所示,硬件测试验证平台整体框架如下,

23.主要包括两路调试串口;第一路调试串口包括依次连接的接口、外部phy和变压器,其中,第一路调试串口的接口用于通待验证电路连接,也就是同待测试的芯片连接。第二路调试串口包括依次连接的单片机stm32f407、外部phy和变压器。两路调试串口都接到路由器,与上位机进行通讯测试。两路调试串口的变压器可以通过网线连接起来。

24.独立于介质的接口(mii)用于mac与外接的phy互联,支持10mbit/s和100mbit/s数据传输模式。精简介质独立接口(rmii)规范降低了10/100mbit/s下微控制器以太网外设与外部phy间的引脚数。根据ieee802.3标准,mii接口需要16个数据和控制信号引脚,而rmii标准则将引脚数减少到了7个。

25.考虑到rmii硬件接口数为mii硬件接口数的一般,所以优先选择rmii。但在电路验证时,两种接口模式都要参与验证。图3为mii接口,图4为mii接口。

26.dp83848支持ieee802.3的mii和rmii接口,与待验证电路和stm32f407接口都匹配。通过smi接口对dp83848进行配置。并且dp83848具备发送和接收端口自动翻转功能,所以网线可交叉连接,也可直连连接,设计的原理图如图5所示。

27.采用mii接口,pyh的时钟频率要求25m,不需要与mac层时钟一致。采用rmii接口,pyh的时钟频率要求50m,需要与mac层时钟一致,通常从mac层获取该时钟源。由于mii和rmii时钟不同,采用跳线帽方式选择时钟。这里需要将50mhz时钟同时传送至stm32f407和dp83848,来同步源晶振产生的50hz频率。频率选择原理如图6所示。

28.测试验证平台环境搭建:

29.首先保证硬件正常工作。两路网络接口都接到路由器,与上位机进行通讯测试。从而确保硬件正确。硬件连接示意框图,如图7所示。

30.为了区分目标电路,这里在一台主机上采用两种不同的仿真器调试电路。仿真器分别为j-link ob v2.0和st-link/v2。

31.电路验证:

32.网线可以选择交叉连接或直接连接。

33.电路验证内容包含smi、rmii、mii验证,mac验证和dma验证。

34.使用专用dma控制器的mac802.3作为以太网外设。它同时支持mii和rmii,需验证两种接口是否工作正常。管脚连接如表1、表2所示。

35.表1

36.管脚功能pa2eth_mdiopc1eth_mdcpb5eth_pps_outpa0eth_mii_crspa3eth_miii_colpb10eth_mii_rx_erpb0eth_mii_rxd2pb1eth_miii_rxd3pc3eth_miii_tx_cikpc2eth_miii_txd2pb8eth_mii_txd3pa1eth_mii_rx_clk_ref_clkpa7eih_mii_rx_dv_crs_dvpc4eth mii_rxxd0pc5eth_mii_rxd1pb11eth_mii_tx_enpb12eth_mii_txd0pb13eth_miii_txd1pe14复位pe15休眠

37.表2

38.管脚功能pa1eth_rmii_ref_clkpa2eth_mdiopa7eth_rmii_crs_dvpb11eth_rmiii_tx_enpb12eth_rmiii_txd0pb13eth_rmii_txd1pc1eth_mdcpc4eth_rmiii_rxd0pc5eth_rmiii_rxxd1pe14复位pe15休眠

39.站管理接口(smi)控制电路通过时钟线、数据线访问dp83848的寄存器。配置dp83848验证smi接口。

40.mac过滤分为广播、单播、多播的目标地址过滤,源地址过滤。目标地址过滤主要设置寄存器中的相应的bit位,有pm、hpf、hu、daif、hm、pam、bfd。源地址过滤主要设置寄存器中的相应的bit位,有pm、saif、saf。

41.举例单播模式1,设置接收端pm设置为1。发送端发送地址设置为ff-ff-ff-ff-ff-ff。

42.验证结果是从串口打印出允许过滤的数据包,不允许的数据包将接收不到。其他过滤模式这里不再赘述。

43.dma具有自主的发送和接收引擎,还有一个csr(控制和状态寄存器)空间。发送引擎将数据从系统存储器传送到tx fifo,而接收引擎将数据从rx fifo传送到系统存储器。控制器在cpu无干预的情况下,利用描述符有效的将数据从源地址移动到目的地。dma专门为面向包的数据传送而设计。控制器可以编程去打断cpu,例如完成帧发送和接收传送操作时以及其它正常或错误的条件下。测试包括dma发送地址\接收地址、dma补足、dma终端、dma转发错误帧、描述符、ipv4有效及upd、ipv4有效负载错误、ip报头错误。

44.以上显示和描述了本发明的基本原理和主要特征和本发明的优点。本行业的技术人员应该了解,本发明不受上述实施例的限制,上述实施例和说明书中描述的只是说明本发明的原理,在不脱离本发明精神和范围的前提下,本发明还会有各种变化和改进,这些变化和改进都落入要求保护的本发明范围内。本发明要求保护范围由所附的权利要求书及其等效物界定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1