天线通道校正方法、装置、设备和存储介质与流程

1.本发明实施例涉及通信技术,尤其涉及一种天线通道校正方法、装置、设备和存储介质。

背景技术:

2.随着无线通信技术和设备的不断发展,多天线技术也得到了越来越多的应用,如宽带大规模多入多出(multi-input multi-output,mimo)系统的基站侧通常配置有阵元数量巨大的天线阵列。多天线系统可利用预编码(precoding)或波束赋形(beamforming)等技术,同时让多个用户设备(user equipment,ue)收发无线资源,从而增加频谱使用效率。

3.在应用多天线预编码和波束赋形技术时,各天线通道(简称通道)从基带到天线端口的幅度、相位和时延需保持一致。然而实际应用中,由于电路制造误差、机械震动、温湿度变化、通道间耦合等原因,不同天线通道间的幅度、相位和时延通常会存在较大的差异,这将极大降低整个系统的性能。因此,必须对各天线通道从基带到天线口的幅度、相位和时延不一致性进行校正,即天线通道校正。

4.目前,通常通过增加辅助校正通道对基站的发射(tx)/接收(rx)通道之间的幅度/相位/时延参数进行校正。由辅助校正通道向各接收通道注入特性已知的校正参考序列,通过适当的校正算法,从而实现接收通道的校正;将各发射通道的发送校正参考序列提取出来,由辅助校正通道接收检测,从而实现发射通道的校正。经过校正后的通道能够保持良好的一致性,能够保证多天线技术(预编码、波束赋形等)的应用。

5.但目前的通道校正方法,在进行rx校正时,辅助校正通道发送参考序列,分别输出到各个待校正通道,各个待校正通道可根据接收到的数据独立计算通道校正系数。而tx校正时,所有待校正通道可采用分时、分频发送相同校正参考序列的方式,辅助校正通道分时、分频计算通道校正系数;或者所有待校正通道同时发送正交的校正参考序列,由辅助校正通道接收到来自所有通道的合路信号,解正交后得到不同通道的信号,进而计算通道校正系数。

6.目前的通道校正方案中,tx通道校正总是需要利用更多的时间、频率资源计算通道校正系数,除此之外,可以发射正交的校正参考序列来解决这个问题,但是由于不确定性,会引入通道间干扰,降低通道校正系数的准确性。

技术实现要素:

7.本发明提供一种天线通道校正方法、装置、设备和存储介质,降低了天线通道校正的复杂度。

8.第一方面,本发明实施例提供了一种天线通道校正方法,包括:

9.通过多个待校正通道向辅助校正通道发送校正参考序列,并从辅助校正通道获取接收信号;

10.根据时域校正矩阵对接收信号进行处理,计算得到每一待校正通道的时域发射信

道响应,所述时域校正矩阵根据多个待校正通道中的时域主要组成径和对应的时延得到;

11.将每一待校正通道的时域发射信道响应转换为每一待校正通道的频域发射信道响应;

12.根据每一待校正通道的频域发射信道响应计算每一待校正通道的发射通道校正系数。

13.在第一方面一种可能的实现方式中,根据多个待校正通道中的时域主要组成径和对应的时延计算时域校正矩阵,包括:

14.使用如下公式计算时域校正矩阵f

[0015][0016]

其中,n

chan

为时域主要组成径的个数,ai为第i个时域主要组成径的幅度,φi为第i个时域主要组成径的相位,τi为第i个时域主要组成径的时延,(0:k-1)=[0,1,2,

…

,k-1]

t

,j为虚数单位,k为频域采样点数。

[0017]

在第一方面一种可能的实现方式中,k≥n

·nchan

,其中n为待校正通道的数量。

[0018]

在第一方面一种可能的实现方式中,根据时域校正矩阵对接收信号进行处理,计算得到每一待校正通道的时域发射信道响应,包括:

[0019]

对所述接收信号去除基础参考序列,得到去除基础参考序列后的接收信号;

[0020]

根据去除基础参考序列后的接收信号以及所述时域校正矩阵估计每一待校正通道的时域发射信道响应矩阵。

[0021]

在第一方面一种可能的实现方式中,接收信号y的信号模型为y=x

·

θ+u,x=[x0·

f,x1·

f,

…

,x

n-1

·

f],θ=[(c0)

t

,(c1)

t

,

…

,(c

n-1

)

t

]

t

,u为辅助校正通道的噪声;

[0022]

所述基础参考序列为:x

ref

=[diag(zcu)];

[0023]

所述去除基础参考序列后的接收信号为:y

de

=x

de

·

θ+u

de

,进而得到θ的估计值,进而得到θ的估计值所述每一待校正通道的时域发射信道响应cn通过公式求解得到;矩阵b通过求解得到;

[0024]

其中,y

de

=[diag(zcu)]-1

·

y,x

de

=[diag(zcu)]-1

·

x,u

de

=[diag(zcu)]-1

·

u,zc为zadoff-chu序列,zcu=e-jπuk(k+1)/m

,u为zc序列根索引,m为不小于k的最小质数,0≤k<k,diag表示进行对角化处理,diag表示进行对角化处理,n

shift

为循环移位长度;n表示待校正通道的通道序号,n=0~n-1;n为待校正通道的数量;σ2为噪声功率,i为单位矩阵。

[0025]

在第一方面一种可能的实现方式中,将每一待校正通道的时域发射信道响应转换为每一待校正通道的频域发射信道响应,包括:

[0026]

通过如下公式计算每一待校正通道的频域发射信道响应

[0027][0028]

在第一方面一种可能的实现方式中,根据每一待校正通道的频域发射信道响应计

算每一待校正通道的发射通道校正系数,包括:

[0029]

通过如下公式计算每一待校正通道的发射通道校正系数

[0030][0031]

在第一方面一种可能的实现方式中,通过多个待校正通道向辅助校正通道发送校正参考序列之前,还包括:

[0032]

确定天线通道校正为发射通道校正或接收通道校正;

[0033]

通过多个待校正通道向辅助校正通道发送校正参考序列,包括:

[0034]

当确定天线通道校正为发射通道校正时,通过多个待校正通道向辅助校正通道发送校正参考序列。

[0035]

在第一方面一种可能的实现方式中,确定天线通道校正为发射通道校正或接收通道校正之后,还包括:

[0036]

当确定天线通道校正为接收通道校正时,通过辅助校正通道向各待校正通道发送基础参考序列;

[0037]

根据每一待校正通道的接收信号得到每一待校正通道的频域接收信道响应;

[0038]

根据每一待校正通道的频域接收信道响应计算每一待校正通道的接收通道校正系数。

[0039]

第二方面,本发明实施例提供一种天线通道校正装置,包括:

[0040]

信号收发模块,用于通过多个待校正通道向辅助校正通道发送校正参考序列,并从辅助校正通道获取接收信号;

[0041]

信道估计模块,用于根据时域校正矩阵对接收信号进行处理,计算得到每一待校正通道的时域发射信道响应,所述时域校正矩阵根据多个待校正通道中的时域主要组成径和对应的时延得到;

[0042]

时频转换模块,用于将每一待校正通道的时域发射信道响应转换为每一待校正通道的频域发射信道响应;

[0043]

校正结果计算模块,用于根据每一待校正通道的频域发射信道响应计算每一待校正通道的发送通道校正系数。

[0044]

在第二方面一种可能的实现方式中,天线通道校正装置还包括:校正方式确定模块,用于确定天线通道校正为发射通道校正或接收通道校正;

[0045]

所述信号收发模块,具体用于当确定天线通道校正为发射通道校正时,通过多个待校正通道向辅助校正通道发送校正参考序列。

[0046]

第三方面,本发明实施例提供一种电子设备,包括:

[0047]

处理器,以及与处理器通信连接的存储器;存储器存储计算机执行指令;

[0048]

处理器执行存储器存储的计算机执行指令,以实现如第一方面任一项可能的实现方式的天线通道校正方法。

[0049]

第四方面,本发明实施例提供一种计算机可读存储介质,其特征在于,计算机可读存储介质中存储有计算机执行指令,计算机执行指令被处理器执行时用于实现如第一方面任一项可能的实现方式的天线通道校正方法。

[0050]

本发明实施例提供的天线通道校正方法、装置、设备和存储介质,通过多个待校正

通道向辅助校正通道发送校正参考序列,并从所述辅助校正通道获取接收信号;根据时域校正矩阵对所述接收信号进行处理,计算得到每一待校正通道的时域发射信道响应;所述时域校正矩阵根据多个待校正通道中的时域主要组成径和对应的时延计算;将每一待校正通道的时域发射信道响应转换为每一待校正通道的频域发射信道响应;根据每一待校正通道的频域发射信道响应计算每一待校正通道的发射通道校正系数。

[0051]

通过将发射通道的频域信道估计转换为时域信道估计,可以在校正参考序列非正交的条件下求解多通道的信道估计,同时采用本发明设计的时域校正矩阵和校正参考序列,避免了多参数信道估计中的大维矩阵求逆问题,能够快速求解多通道校正系数,进而简化了矩阵求逆的复杂度,提高了计算速度。

附图说明

[0052]

图1为天线通道校正原理示意图;

[0053]

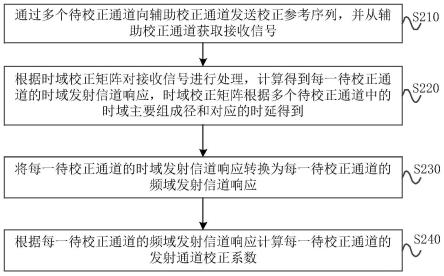

图2为本技术实施例提供的一种天线通道校正方法的流程图;

[0054]

图3为待校正通道脉冲响应示意图;

[0055]

图4为本技术实施例提供的另一种天线通道校正方法的流程图;

[0056]

图5为本技术实施例提供的再一种天线通道校正方法的流程图;

[0057]

图6为本技术实施例提供的一种天线通道校正装置的结构示意图;

[0058]

图7为本发明实施例提供的一种电子设备的结构示意图。

具体实施方式

[0059]

下面结合附图和实施例对本发明作进一步的详细说明。可以理解的是,此处所描述的具体实施例仅仅用于解释本发明,而非对本发明的限定。另外还需要说明的是,为了便于描述,附图中仅示出了与本发明相关的部分而非全部结构。

[0060]

图1为天线通道校正原理示意图。如图1所示,通道0-通道n-1为n个待校正通道,待校正通道的频域脉冲响应为h=[h0,h1,

…hk

,

…

,h

k-1

]

t

,其中k表示第k个频域采样点,通道校正的目的是使经过该通道后的信号,不发生幅度、相位和时延变化。因此在信号通过该通道前,利用频域校正系数w=[w0,w1,

…

,w

k-1

]

t

对信号进行滤波(点乘),满足条件的w=(ηhh)-1

·hh

。因此,通道校正的关键步骤是通过的频域信道估计,也就是计算频域通道校正系数。

[0061]

在进行天线通道校正时,一般需要使用辅助校正通道,辅助校正通道与各待校正通道通过功分-耦合电路连接,在进行发射通道校正时,由各待校正通道发送不同的校正参考序列其中diag表示进行对角化处理,k为频域采样点数,n表示第n个待校正通道。经过功分-耦合电路后输出到辅助校正通道,经过采样后获取经过多通道后的合路信号。进行发射通道校正的接收信号模型可以表示为:其中y表示辅助校正通道的接收信号,为各待校正通道的发射频域信道响应,u为辅助校正通道的噪声,n为待校正通道的数量。

[0062]

对于发射信号校正,由于接收的是合路信号,因此通常需要多通道发送相互正交

的校正参考序列,在接收侧解正交后分别进行信道估计,但由于干扰、频偏、时偏以及噪声等问题的存在,正交性会被一定程度的破坏,因此各通道参数的估计会被通道间干扰所影响。

[0063]

在进行接收通道校正时,辅助校正通道发送基础参考序列x=diag[x0,x1,

…

,x

k-1

],经过功分-耦合电路后分别输出到各待校正通道,经过采样后获取多个待校正通道的接收信号。接收信号的信号模型可以表示为其中yn表示第n个待校正通道的接收信号,为各待校正通道的接收频域信道响应,un为各待校正通道的噪声。

[0064]

对于接收通道校正,可以对每一路接收信号采用适当的信道估计方法,例如最小均方误差(minimum mean square error,mmse)估计,即可得到各通道的参数。

[0065]

为了解决天线发射通道校正存在的问题,本技术实施例提供一种天线通道校正方法,将发射通道的频域信道估计转换为时域信道估计,可以在校正参考序列非正交的条件下进行多通道的信道估计。同时设计了特殊的校正参考序列和时域校正矩阵,避免多参数信道估计中的大维矩阵求逆问题。

[0066]

图2为本技术实施例提供的一种天线通道校正方法的流程图,如图2所示,本实施例提供的天线通道校正方法包括:

[0067]

步骤s210,通过多个待校正通道向辅助校正通道发送校正参考序列,并从辅助校正通道获取接收信号。

[0068]

本实施例提供的天线通道校正方法用于进行天线发射通道的校正。对于天线通道校正而言,需要分别进行发射通道校正和接收通道校正,但根据前述分析可知,天线发射通道校正存在校正误差较大等问题,因此本实施例提供的天线通道校正方法用于进行天线发射通道的校正,对于天线的接收通道,可以采用现有任一种校正方法进行校正,或者根据本实施例提供的天线通道校正方法生成的校正参考序列进行天线接收通道的校正,对于天线接收通道的校正将在后面的实施例中进行说明。

[0069]

在本技术实施例中,对天线发射通道进行时域信道估计,再进一步地将时域信道估计结果转换为频域信道估计结果。

[0070]

与传统的发射通道校正方法相同,在进行发射通道校正时,通过多个待校正通道向辅助校正通道发送校正参考序列,并从辅助校正通道获取接收信号。每个待校正通道发送的校正参考序列不同,各待校正通道发送的校正参考序列为

[0071]

各待校正通道发送的校正参考序列可以根据基础参考序列生成,其中基础参考序列可以根据zc(zadoff-chu)序列生成。以基于zc序列产生基础参考序列为例,zc序列的生成可以为:

[0072]

zcu=e-jπuk(k+1)/m

[0073]

u为zc序列根索引,可配置为1,m为不小于k的最小质数,0≤k<k。

[0074]

在发射通道校正中,通过基础参考序列在时域上的循环移位生成每个通道的校正参考序列。循环移位长度n

shift

应大于每个通道主要组成径的时延拓展长度,以保证求解过程中的相关矩阵满秩,通道n的校正参考序列可以表示为其中

[0075]

步骤s220,根据时域校正矩阵对接收信号进行处理,计算得到每一待校正通道的时域发射信道响应,时域校正矩阵根据多个待校正通道中的时域主要组成径和对应的时延得到。

[0076]

接着,对接收信号进行信道估计,这里的信道估计是进行时域信道估计,得到每一待校正通道的时域发射信道响应。

[0077]

在多通道系统中,信号经过每个待校正通道中的通路通常可以认为是宽带系统,在时域上可以近似表示成单个强径信道与若干个连续相邻的时域采样点上的弱单径信道叠加,因此可以首先根据多个待校正通道中的时域主要组成径和对应的时延计算时域校正矩阵,时域校正矩阵是用于表征频域信道响应和时域信道响应之间的关系的参数。时域主要组成径为:时域上的某个时延对应的若干单径信道的叠加,即时域上某个时延对应的强单径信道和若干个连续相邻时域采样点上的弱单径信道的叠加。

[0078]

具体地,每个待校正通道的系统脉冲响应可用图3表示,图3为待校正通道脉冲响应示意图。如图3所示,n

chan

为时域主要组成径的个数,ai为第i个时域主要组成径的幅度,φi为第i个时域主要组成径的相位,τi为第i个时域主要组成径的时延,j为虚数单位,k为频域采样点数,那么通道n的频域模型可以表示为

[0079][0080]

其中:

[0081][0082][0083]

(0:k-1)=[0,1,2,

…

,k-1]

t

[0084]hn

为通道n的频域信道响应,f为时域校正矩阵,cn为通道n的时域信道响应。因此,对于发射通道的频域信道估计,可以转换成对通道的时域信道估计。预先配置时域主要组成径的个数n

chan

和对应的时延τi,保证选定的时延拓展大于待校正通道的时延拓展,进而可以确定时域校正矩阵f。待估计的时域参数主要有主要组成径的幅度响应ai和相位响应φi。

[0085]

在本技术实施例中,以最小均方误差(mmse)方法进行信道估计为例进行说明。无论是发射通道估计还是接收通道估计,各通道的接收信号模型可以表示为y=x

·

θ+u,这里的y表示接收信号,x表示已知信号,u表示通道噪声,θ为未知参数,也就是通道响应。采用mmse方法进行未知参数θ的估计:

[0086][0087]

其中r

θθ

为待估计参数θ之间的协方差矩阵,在没有通道先验信息的前提下配置为单位对角矩阵i,σ2为噪声功率。在本实施例中,以r

θθ

为单位对角矩阵进行未知参数估计。

[0088]

对于接收通道校正,每个待校正通道均采用相同的方式进行信道估计,需要重复n次操作,以分别获取即各待校正的频域接收信道响应。其中,x=x

ref

=diag(zcu),是待估计通道n的频域信道,u=un是待估计通道n的接收噪声,y=yn是待估计通道n的接收信号。

[0089]

对于发送通道校正,由于x是一般矩阵,所以(x

·rθθ

·

xh+σ2·

i)-1

的计算会变得非

常复杂(复杂度为矩阵维度的三次方倍o(n3)),尤其是当频域采样点数多、待校正通道数多、主要组成径n

chan

均非常大时,实时计算变得非常困难。正因如此,本技术实施例设计了特殊的参考校正序列和时域校正矩阵f,使得x具有特殊矩阵结构,从而使得发射通道校正所涉及的(x

·rθθ

·

xh+σ2·

i)-1

具有特殊矩阵结构,进而简化了矩阵求逆的复杂度,提高了计算速度。需要说明的是,频域采样点的个数k须大于通道数n与设定主要组成径个数n

chan

的乘积,即k≥n

·nchan

,以保证mmse参数估计解的存在性。

[0090]

对于发射通道校正,接收信号的通用模型中,y为辅助校正通道的接收信号,x=[x0·

f,x1·

f,

…

,x

n-1

·

f],θ=[(c0)

t

,(c1)

t

,

…

,(c

n-1

)

t

]

t

,u为辅助校正通道的噪声。其中c0,c1,

…

,c

n-1

为各通道的待估计参数。

[0091]

具体地,首先对接收信号的信号模型去除基础参考序列,多个待校正通道发送的校正参考序列根据基础参考序列生成。对接收信号y的信号模型y=x

·

θ+w两侧乘以基础参考序列x

ref

=[diag(zcu)]的逆得到y

de

=x

de

·

θ+u

de

,其中y

de

=[diag(zcu)]-1

·

y,x

de

=[diag(zcu)]-1

·

x,u

de

=[diag(zcu)]-1

·

u。

[0092]

然后通过最小均方误差方法估计各待校正通道的时域发射信道响应矩阵θ的估计值

[0093][0094]

其中其中n

shift

为循环移位长度;n表示待校正通道的通道序号,n=0~n-1;n为待校正通道的数量;σ2为噪声功率,i为单位矩阵。u为zc序列根索引。

[0095]

由于和f均可看成是离散傅里叶变换(discrete fourier transform,dft)矩阵,可以证明为hermitian-toeplitz矩阵,进而也为hermitian-toeplitz矩阵。设对等式两边同时左乘可得求解得到矩阵b,通过得到每一待校正通道的时域发射信道响应cn。为hermitian-toeplitz线性方程组,其复杂度为o(n2),对比于矩阵求逆的复杂度o(n3),复杂度大幅降低。

[0096]

步骤s230,将每一待校正通道的时域发射信道响应转换为每一待校正通道的频域发射信道响应。

[0097]

在得到每一待校正通道的时域发射信道响应后,可以将其转换为每一待校正通道的频域发射信道响应。

[0098]

具体地,可以通过如下公式计算每一待校正通道的频域发射信道响应重复n次操作。

[0099][0100]

步骤s240,根据每一待校正通道的频域发射信道响应计算每一待校正通道的发射

通道校正系数。

[0101]

最后,可以根据每一待校正通道的频域发射信道响应计算每一待校正通道的发射通道校正系数。具体地,通过如下公式计算每一待校正通道的发射通道校正系数w

tn

[0102][0103]

本实施例提供的天线通道校正方法,通过将发射通道的频域信道估计转换为时域信道估计,可以在校正参考序列非正交的条件下求解多通道的信道估计,同时采用本发明设计的时域校正矩阵f,以及参考校正序列设计的时域校正矩阵f,以及参考校正序列使得x具有特殊矩阵结构,避免了多参数信道估计中的大维矩阵求逆问题,能够快速求解多通道校正系数,进而简化了矩阵求逆的复杂度,提高了计算速度。

[0104]

采用本技术实施例提供的天线通道校正方法的相关设计,还可以进行接收通道的校正。那么,首先需要确定天线通道校正为发射通道校正或接收通道校正。当确定天线通道校正为发射通道校正时,通过多个待校正通道向辅助校正通道发送校正参考序列,也就是进行发射通道校正。当确定天线通道校正为接收通道校正时,通过辅助校正通道向各待校正通道发送基础参考序列,也就是进行接收通道校正,当然也可以采用上述设计的校正参考序列进行天线接收通道的校正。

[0105]

图4为本技术实施例提供的另一种天线通道校正方法的流程图,如图4所示,本实施例提供的天线通道校正方法包括:

[0106]

步骤s410,当确定天线通道校正为接收通道校正时,通过辅助校正通道向各待校正通道发送基础参考序列。

[0107]

本实施例提供的天线通道校正方法用于进行天线接收通道的校正。当确定天线通道校正为接收通道校正时,通过辅助校正通道向各待校正通道发送基础参考序列,基础参考序列可以是根据zc(zadoff-chu)序列生成,zcu=e-jπuk(k+1)/m

,x=x

ref

=[diag(zcu)]。

[0108]

步骤s420,根据每一待校正通道的接收信号得到每一待校正通道的频域接收信道响应。

[0109]

每一待校正通道均能接收到辅助校正通道发送的基础参考序列,然后根据每一待校正通道的接收信号得到每一待校正通道的频域接收信道响应。

[0110]

具体地,各通道的接收信号模型仍然可以用通用模型表示为y=x

·

θ+u,对于接收通道校正,y=yn是待估计通道n的接收信号,x为基础参考信号序列x=diag(zcu),为各待校正通道的频域接收信道响应,u=un是待估计通道n的接收噪声。仍然通过最小均方误差方法估计各待校正通道的频域接收信道响应

[0111][0112]

接收通道校正中,每个通道单独处理,单个通道x的是对角阵,所以(x

·rθθ

·

xh+σ2·

i)-1

很容易求得,进而可获取所有通道的信道估计。重复重复n次操作。

[0113]

步骤s430,根据每一待校正通道的频域接收信道响应计算每一待校正通道的接收通道校正系数。

[0114]

最后,可以根据每一待校正通道的频域接收信道响应计算每一待校正通道的接收通道校正系数。具体地,通过如下公式计算每一待校正通道的发射通道校正系数

[0115][0116]

图5为本技术实施例提供的再一种天线通道校正方法的流程图,如图5所示,本实施例提供的天线通道校正方法为结合发射通道校正和接收通道校正的完整天线通道校正方法。

[0117]

首先,判断是tx校正还是rx校正。在确定是tx校正时,首先利用zc序列生成各通道参考校正序列xn,然后由各路待校正通道发送参考校正序列xn,经过功分-耦合器后达到辅助校正通道,接着从辅助校正通道采样获取接收信号y,配置主要组成径的个数和对应的时延进而计算矩阵f,对接收信号模型去基础序列得到y

de

和x

de

,求解hermitian-toeplitz线性方程组(x

de

·

x

deh

+σ2·

i)

·

b=y

de

得到未知矩阵b,计算所有通道的时域信道估计结果最后将时域信道估计结果转换为频域信道估计结果然后就可以计算每一路待校正通道的校正系数wn=[(hn)h·

(hn)]-1

(hn)h,具体为在确定是rx校正时,首先利用zc序列生成基础参考校正序列x,然后由辅助校正通道发送基础参考校正序列x,经过功分-耦合器后到达各路待校正通道,接着从各路待校正通道采样获取接收信号yn,最后对每一路待校正通道,利用最小均方误差估计计算信道估计结果然后就可以计算每一路待校正通道的校正系数wn=[(hn)h·

(hn)]-1

(hn)h,具体为

[0118]

图6为本技术实施例提供的一种天线通道校正装置的结构示意图,如图6所示,本实施例提供的天线通道校正装置包括:

[0119]

信号收发模块61,用于通过多个待校正通道向辅助校正通道发送校正参考序列,并从辅助校正通道获取接收信号。信道估计模块62,用于根据时域校正矩阵对接收信号进行处理,计算得到每一待校正通道的时域发射信道响应,时域校正矩阵根据多个待校正通道中的时域主要组成径和对应的时延得到。时频转换模块63,用于将每一待校正通道的时域发射信道响应转换为每一待校正通道的频域发射信道响应。校正结果计算模块64,用于根据每一待校正通道的频域发射信道响应计算每一待校正通道的发射通道校正系数。

[0120]

本实施例提供的天线通道校正装置用于实现图2所示实施例的天线通道校正方法,其实现原理和技术效果类似,此处不再赘述。

[0121]

进一步地,天线通道校正装置还包括:校正方式确定模块,用于确定天线通道校正为发射通道校正或接收通道校正;所述信号收发模块61,具体用于当确定天线通道校正为发射通道校正时,通过多个待校正通道向辅助校正通道发送校正参考序列

[0122]

进一步地,所述信号收发模块61,还用于通过辅助校正通道向各待校正通道发送基础参考序列,并从所述多个待校正通道获取接收信号;所述信道估计模块62,还用于根据每一待校正通道的接收信号得到每一待校正通道的频域接收信道响应;所述校正结果结算模块64,还用于根据每一待校正通道的频域接收信道响应计算每一待校正通道的接收通道

校正系数。

[0123]

图7为本发明实施例提供的一种电子设备的结构示意图,如图7所示,该电子设备包括处理器71、存储器72,接收器73和发送器74;电子设备中处理器71的数量可以是一个或多个,图7中以一个处理器71为例;电子设备中的处理器71、存储器72、接收器73和发送器74可以通过总线或其他方式连接,图7中以通过总线连接为例。

[0124]

存储器72作为一种计算机可读存储介质,可设置为存储软件程序、计算机可执行程序以及模块,如本技术图2或图4实施例中的天线通道校正方法对应的程序指令/模块(例如天线通道校正装置中的信号收发模块61、信道估计模块62、时频转换模块63、校正结果计算模块64)。处理器71通过运行存储在存储器72中的软件程序、指令以及模块,从而完成电子设备至少一种功能应用以及数据处理,即实现上述的天线通道校正方法。

[0125]

存储器72可主要包括存储程序区和存储数据区,其中,存储程序区可存储操作系统、至少一个功能所需的应用程序;存储数据区可存储根据远程设备的使用所创建的数据等。此外,存储器72可以包括高速随机存取存储器,还可以包括非易失性存储器,例如至少一个磁盘存储器件、闪存器件、或其他非易失性固态存储器件。

[0126]

接收器73为能够接收外部输入信号的器件、模块或组合,发送器74为能够向外部输出信号的器件、模块或组合。

[0127]

本技术实施例还提供一种包含计算机可执行指令的存储介质,计算机可执行指令在由计算机处理器执行时用于执行一种天线通道校正方法,该方法包括:通过多个待校正通道向辅助校正通道发送校正参考序列,并从辅助校正通道获取接收信号;根据时域校正矩阵对接收信号进行处理,计算得到每一待校正通道的时域发射信道响应,时域校正矩阵根据多个待校正通道中的时域主要组成径和对应的时延得到;将每一待校正通道的时域发射信道响应转换为每一待校正通道的频域发射信道响应;根据每一待校正通道的频域发射信道响应计算每一待校正通道的发射通道校正系数。

[0128]

一般来说,本技术的多种实施例可以在硬件或专用电路、软件、逻辑或其任何组合中实现。例如,一些方面可以被实现在硬件中,而其它方面可以被实现在可以被控制器、微处理器或其它计算装置执行的固件或软件中,尽管本技术不限于此。

[0129]

本技术的实施例可以通过计算机装置的数据处理器执行计算机程序指令来实现,例如在处理器实体中,或者通过硬件,或者通过软件和硬件的组合。计算机程序指令可以是汇编指令、指令集架构((instruction set architecture,isa)指令、机器指令、机器相关指令、微代码、固件指令、状态设置数据、或者以一种或多种编程语言的任意组合编写的源代码或目标代码。

[0130]

本技术附图中的任何逻辑流程的框图可以表示程序步骤,或者可以表示相互连接的逻辑电路、模块和功能,或者可以表示程序步骤与逻辑电路、模块和功能的组合。计算机程序可以存储在存储器上。存储器可以具有任何适合于本地技术环境的类型并且可以使用任何适合的数据存储技术实现,例如但不限于只读存储器(read-only memory,rom)、随机访问存储器(random access memory,ram)、光存储器装置和系统(数码多功能光碟(digital video disc,dvd)或光盘((compact disc,cd))等。计算机可读介质可以包括非瞬时性存储介质。数据处理器可以是任何适合于本地技术环境的类型,例如但不限于通用计算机、专用计算机、微处理器、数字信号处理器(digital signal processing,dsp)、专用

集成电路(application specific integrated circuit,saic)、可编程逻辑器件(field-programmable gate array,fgpa)以及基于多核处理器架构的处理器。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1