一种降低芯片Pipeline时间戳总线位宽的方法及应用与流程

本发明是关于电子通信领域,特别是关于一种降低芯片pipeline时间戳总线位宽的方法及应用。

背景技术:

1、报文在交换芯片转发时,会基于入方向端口的mac层产生入方向时间戳(ingresstimestamp),入方向时间戳会存入pipeline总线的报文信息(pi,packetinformation)中,随着报文pipeline处理一步一步传到编辑模块,编辑模块将入方向时间戳填入报文中,用于满足多种协议应用,比如int(in-band telemetry,带内遥测),erspanv3(encapsulatedremoteswitchportanalyzer,封装远程端口镜像),ptp(precisiontimeprotocol,高精度时钟协议)。

2、芯片pipeline处理报文需要分别经历ipe(ingresspipelineengine,入方向流水线处理),bsr(bufferstoreretrieve,缓存存储获取)和epe(egress pipelineengine,出方向流水线处理)三个主要流水线处理。入方向时间戳表示报文进入交换芯片的时间戳,一般是入方向端口的mac层产生capture信号到tsengine(高精度时钟引擎),tsengine立即产生一组时间戳。当需要将入方向时间戳编辑到报文时,需要将入方向时间戳传入到epe的编辑模块,才能将入方向时间戳编辑到报文里面。

3、在现有技术中,当入方向端口的mac层capture到入方向的时间戳,将m位的入方向时间戳编码到报文信息中,报文信息是携带报文处理信息的bus(总线),贯穿交换芯片的ipe、bsr以及epe。随着报文在pipeline处理,m位入方向时间戳随着报文信息被传入到epe的edit模块,edit模块直接从报文信息中获取m位的入方向时间戳,编辑到报文预先定义的位置,比如int协议的metadata部分,erspanv3报文的extendheader部分。此时交换芯片入方向时间戳为64位的值,即m为64。

4、由于报文信息贯穿芯片的ipe、bsr和epe,报文信息的总线宽度制约着芯片设计复杂度和制造成本。64位的入方向时间戳会较大增加ipe、bsr和epe的报文信息总线宽度,也增加了芯片设计复杂度和制造成本。

5、公开于该背景技术部分的信息仅仅旨在增加对本发明的总体背景的理解,而不应当被视为承认或以任何形式暗示该信息构成已为本领域一般技术人员所公知的现有技术。

技术实现思路

1、本发明的目的在于提供一种降低芯片pipeline时间戳总线位宽的方法及应用,其能够降低交换芯片携带的位时间戳的pipeline总线宽度,从而降低了芯片pipeline总线宽度带来的设计复杂度和芯片制造成本。

2、为实现上述目的,本发明的实施例提供了一种降低芯片pipeline时间戳总线位宽的方法。

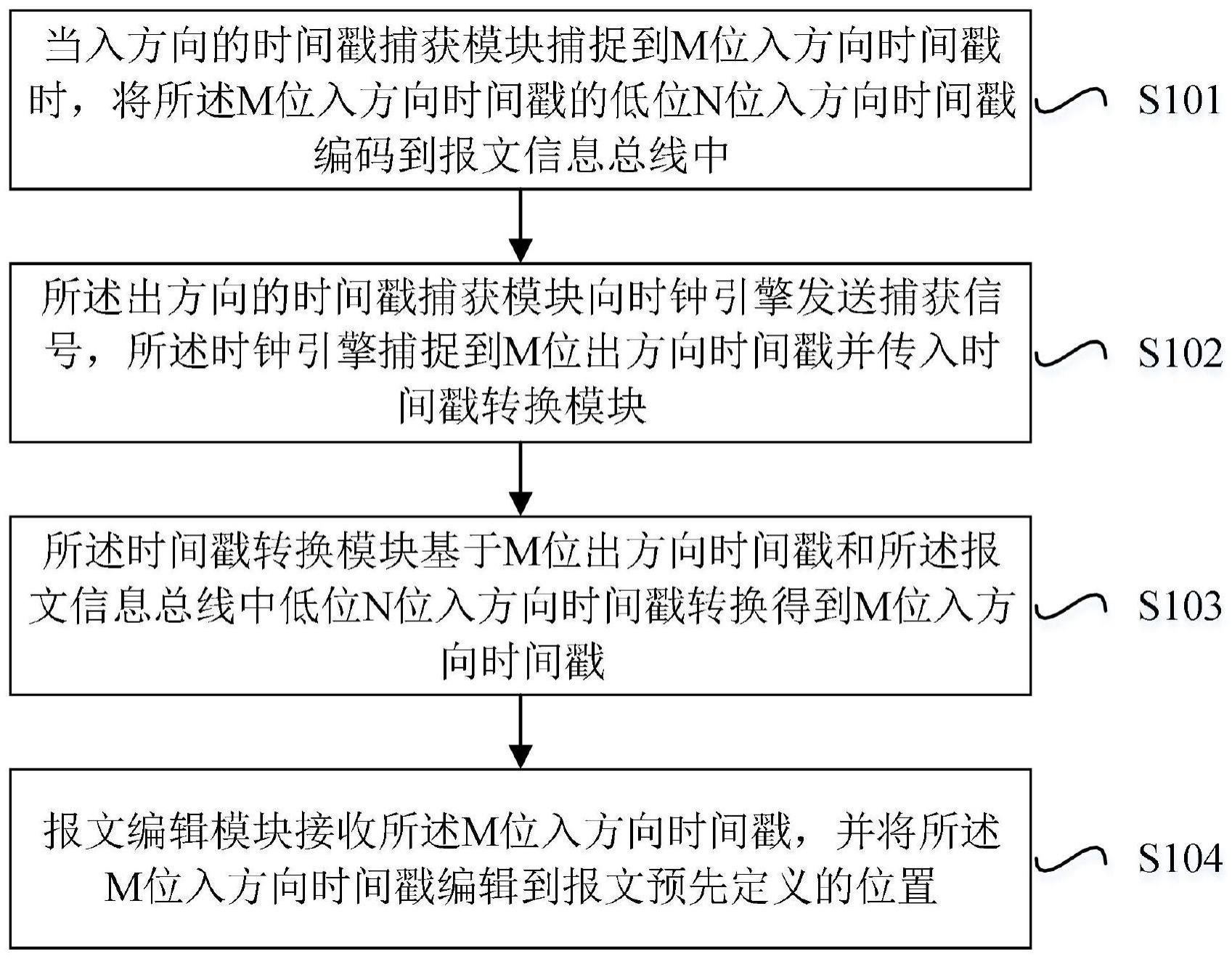

3、在本发明的一个或多个实施方式中,所述方法包括:当入方向的时间戳捕获模块捕捉到m位入方向时间戳时,将所述m位入方向时间戳的低位n位入方向时间戳编码到报文信息总线中,其中n小于m;所述出方向的时间戳捕获模块向时钟引擎发送捕获信号,所述时钟引擎捕捉到m位出方向时间戳并传入时间戳转换模块;所述时间戳转换模块基于m位出方向时间戳和所述报文信息总线中低位n位入方向时间戳转换得到m位入方向时间戳;以及报文编辑模块接收所述m位入方向时间戳,并将所述m位入方向时间戳编辑到报文预先定义的位置。

4、在本发明的一个或多个实施方式中,将所述m位入方向时间戳的低位n位入方向时间戳编码到报文信息总线中,包括:当报文从入方向端口进入芯片时,入方向的时间戳捕获模块通知高精度时钟引擎产生m位入方向时间戳;以及所述入方向的时间戳捕获模块对所述m位入方向时间戳进行截断,获得低位n位入方向时间戳,并把所述低位n位入方向时间戳编码到报文信息中。

5、在本发明的一个或多个实施方式中,所述时间戳转换模块基于m位出方向时间戳和所述报文信息总线中低位n位入方向时间戳转换得到m位入方向时间戳,包括:所述时间戳转换模块获取报文信息中所述低位n位入方向时间戳,结合所述m位出方向时间戳,将所述m位出方向时间戳截取出低位n位出方向时间戳编码,经过转换算法计算得到所述m位入方向时间戳。

6、在本发明的一个或多个实施方式中,所述经过转换算法计算得到所述m位入方向时间戳,包括:比较所述n位出方向时间戳和所述n位入方向时间戳的大小;当所述n位入方向时间戳小于所述n位出方向时间戳时,使用所述n位入方向时间戳替换所述m位出方向时间戳中的低位n位出方向时间戳,得到m位入方向时间戳。

7、在本发明的一个或多个实施方式中,所述经过转换算法计算得到所述m位入方向时间戳,还包括:当所述n位入方向时间戳大于所述n位出方向时间戳时,所述n位入方向时间戳与所述n位出方向时间戳经过借位补偿方式计算出时间差值,转换出期望的m位入方向时间戳。

8、在本发明的一个或多个实施方式中,所述经过借位补偿方式计算出时间差值,包括:对所述n位出方向时间戳借位补偿第n+1位的值1,使得n+1位出方向时间戳比所述n位入方向时间戳大,则n+1位出方向时间戳减去所述n位入方向时间戳得到正值的时间差,即报文转发的驻留时间;以及所述m位出方向时间戳减去所述时间差,获得m位入方向时间戳。

9、在本发明的一个或多个实施方式中,所述方法还包括:m为64,30≤n≤40。

10、在本发明的另一个方面当中,提供了一种降低芯片pipeline时间戳总线位宽的装置,其包括入方向处理模块、出方向处理模块、时间戳转换模块和报文编辑模块。

11、入方向处理模块,用于当入方向的时间戳捕获模块捕捉到m位入方向时间戳时,将所述m位入方向时间戳的低位n位入方向时间戳编码到报文信息总线中,其中n小于m。

12、出方向处理模块,用于所述出方向的时间戳捕获模块向时钟引擎发送捕获信号,所述时钟引擎捕捉到m位出方向时间戳并传入时间戳转换模块。

13、时间戳转换模块,用于所述时间戳转换模块基于m位出方向时间戳和所述报文信息总线中低位n位入方向时间戳转换得到m位入方向时间戳。

14、报文编辑模块,用于报文编辑模块接收所述m位入方向时间戳,并将所述m位入方向时间戳编辑到报文预先定义的位置。

15、在本发明的一个或多个实施方式中,所述入方向处理模块还用于:当报文从入方向端口进入芯片时,入方向的时间戳捕获模块通知高精度时钟引擎产生m位入方向时间戳;以及所述入方向的时间戳捕获模块对所述m位入方向时间戳进行截断,获得低位n位入方向时间戳,并把所述低位n位入方向时间戳编码到报文信息中。

16、在本发明的一个或多个实施方式中,所述出方向处理模块还用于:所述时间戳转换模块获取报文信息中所述低位n位入方向时间戳,结合所述m位出方向时间戳,将所述m位出方向时间戳截取出低位n位出方向时间戳编码,经过转换算法计算得到所述m位入方向时间戳。

17、在本发明的一个或多个实施方式中,所述时间戳转换模块还用于:比较所述n位出方向时间戳和所述n位入方向时间戳的大小;当所述n位入方向时间戳小于所述n位出方向时间戳时,使用所述n位入方向时间戳替换所述m位出方向时间戳中的低位n位出方向时间戳,得到m位入方向时间戳。

18、在本发明的一个或多个实施方式中,所述时间戳转换模块还用于:当所述n位入方向时间戳大于所述n位出方向时间戳时,所述n位入方向时间戳与所述n位出方向时间戳经过借位补偿方式计算出时间差值,转换出期望的m位入方向时间戳。

19、在本发明的一个或多个实施方式中,所述时间戳转换模块还用于:对所述n位出方向时间戳借位补偿第n+1位的值1,使得n+1位出方向时间戳比所述n位入方向时间戳大,则n+1位出方向时间戳减去所述n位入方向时间戳得到正值的时间差,即报文转发的驻留时间;以及所述m位出方向时间戳减去所述时间差,获得m位入方向时间戳。

20、在本发明的一个或多个实施方式中,所述入方向处理模块还用于:m为64,30≤n≤40。

21、在本发明的另一个方面当中,提供了一种电子设备,包括:至少一个处理器;以及存储器,所述存储器存储指令,当所述指令被所述至少一个处理器执行时,使得所述至少一个处理器执行如上所述的降低芯片pipeline时间戳总线位宽的方法。

22、在本发明的另一个方面当中,提供了一种计算机可读存储介质,所述计算机可读存储介质上存储有计算机程序,所述计算机程序被处理器执行时实现如所述的降低芯片pipeline时间戳总线位宽的方法的步骤。

23、与现有技术相比,根据本发明实施方式的降低芯片pipeline时间戳总线位宽的方法及应用,能够解决过大消耗pipeline总线位宽的问题,通过pipeline获取时间戳并结合较短位宽的目标时间戳,经过转换模块的算法运算获得较长位宽的目标时间戳,有效地降低交换芯片携带64位时间戳的pipeline总线宽度;解决时间戳计算时的交换芯片数值翻转的问题,创新使用了借位补偿方式,能够基于二进制数据进行借位减法运算,实现对时间戳转换算法的完善,大大降低了芯片pipeline总线宽度带来的设计复杂度和芯片制造成本。

- 还没有人留言评论。精彩留言会获得点赞!