一种可配置多速率的SDH线路的帧头检测方法及系统与流程

本发明涉及光同步数字传输领域,具体涉及一种可配置多速率的sdh线路的帧头检测方法及系统。

背景技术:

1、同步数字体系(sdh,synchronous digital hierarchy)技术在当前的社会中使用非常广泛,目前常用的有stm-1、stm-4、stm-16和stm-64的速率(统称为stm-n,n=4n),能将不同速率的数据流中提取stm-n帧则是非常重要的工作。

2、在sdh网络系统中使用stm-n的帧格式进行传输,stm-n帧结构中的帧定位字符由3×n个a1字节后紧随3×n个a2字节组成,a1字节为二进制数11110110(十六进制数为0xf6),a2字节为二进制数00101000(十六进制数为0x28)。而a1a2组成的帧定位字符在stm-n结构的开始位置,正确检测stm-n的帧头才能顺利处理stm-n帧中包含的开销字节和有效载荷。

3、在传统的帧头检测方法中,低速的stm-1线路使用串行数据帧头检测的方式进行定帧,高速的stm-n线路中使用将移位后的并行数据与a1a2字符进行比较的检测方式进行定帧,或者将并行数据与移位后的a1a2字符进行比较的检测方式进行定帧。同时在定帧后如果路线出现传输错误,此时帧头检测结果已经失效,应该对此时的定帧状态进行上报并重新检测帧头。

技术实现思路

1、本发明提供的一种可配置多速率的sdh线路的帧头检测方法及系统能够实时提供定帧状态给系统,在满足sdh协议的情况下对stm-n帧进行重新的检测。

2、为了达到上述发明目的,本发明采用的技术方案为:

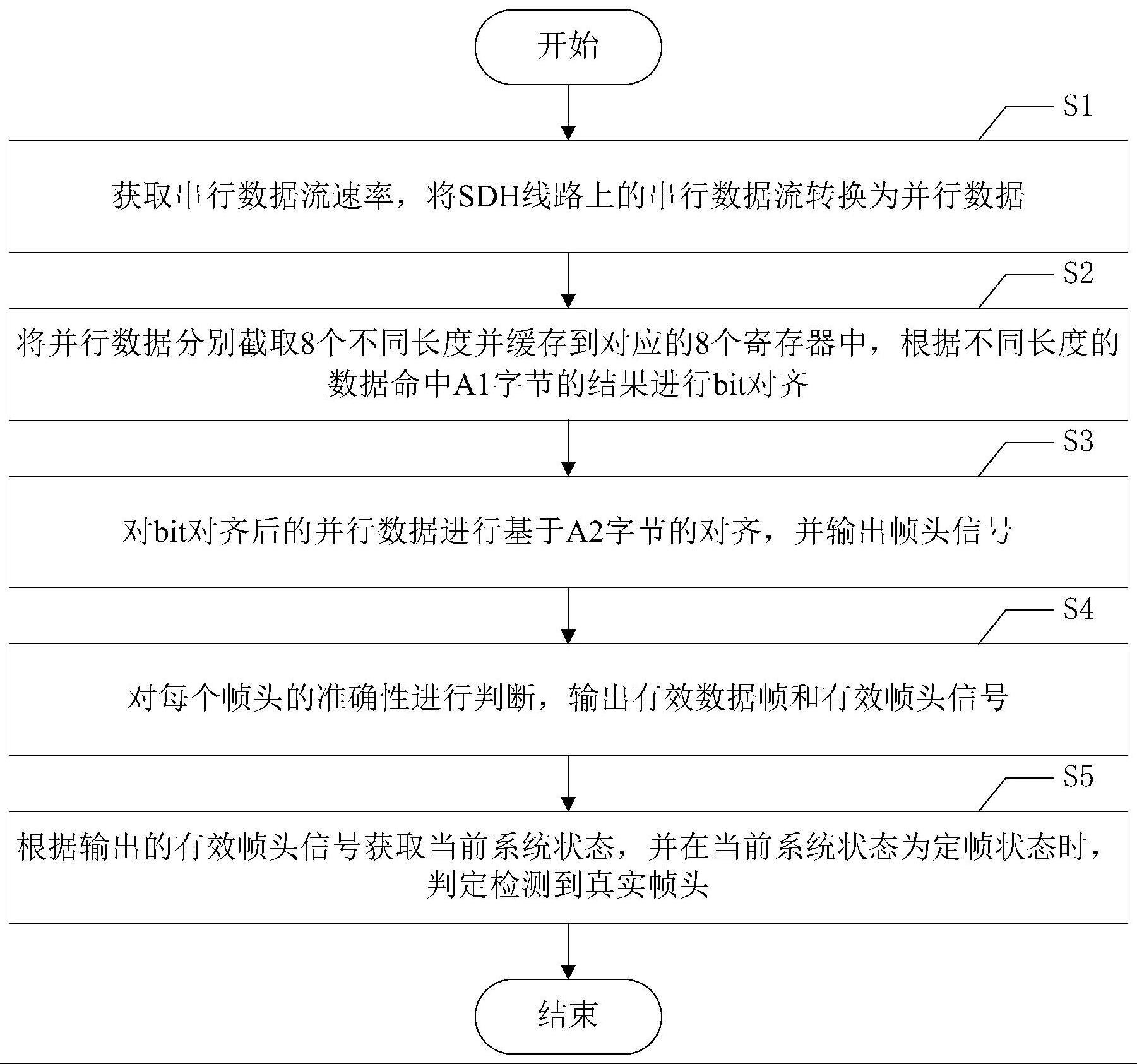

3、提供一种可配置多速率的sdh线路的帧头检测方法,其包括以下步骤:

4、s1、获取串行数据流速率,将sdh线路上的串行数据流转换为并行数据;

5、s2、将并行数据分别截取8个不同长度并缓存到对应的8个寄存器中,根据不同长度的数据命中a1字节的结果进行bit对齐;

6、s3、对bit对齐后的并行数据进行基于a2字节的对齐,并输出帧头信号;

7、s4、对每个帧头的准确性进行判断,输出有效数据帧和有效帧头信号;

8、s5、根据输出的有效帧头信号获取当前系统状态,并在当前系统状态为定帧状态时,判定检测到真实帧头。

9、进一步地,串行数据流速率包括155.52mbps、622.08mbps、2.488gbps和9.953gbps,分别对应stm-1帧结构、stm-4帧结构、stm-16帧结构和stm-64帧结构;stm-n帧结构中的帧定位字符由3×n个a1字节后紧随3×n个a2字节组成,n=1,4,16,64。

10、进一步地,将sdh线路上的串行数据流转换为并行数据流的具体方法为:

11、当串行数据流速率为155.52mbps和622.08mbps时,将并行数据的位宽设置为8bit;当串行数据流速率为2.488gbps时,将并行数据的位宽设置为32bit;当串行数据流速率为9.953gbps时,将并行数据的位宽设置为64bit。

12、进一步地,步骤s2的具体方法包括以下子步骤:

13、s2-1、判断当前并行数据的位宽是否为8bit,若是则将相邻两个并行数据拼接为16bit的并行数据,进入步骤s2-2;否则直接进入步骤s2-2;

14、s2-2、将当前的并行数据分别截取为15bit、14bit、13bit、12bit、11bit、10bit、9bit和8bit的长度,并对应缓存到reg1、reg2、reg3、reg4、reg5、reg6、reg7和reg8中;其中reg表示寄存器;

15、s2-3、将8个寄存器中的数据进行右对齐,并从最右开始,将第m列数据作为数据组,即得到8组8bit的数据组qn,n=8-m,m=1,2,3,4,5,6,7,8;

16、s2-4、将8组8bit的数据组qn分别与a1字节进行匹配,将匹配命中的数据组qn的n值作为偏移量n;

17、s2-5、根据偏移量n对当前并行数据进行n比特的左移;

18、s2-6、判断位移后的并行数据是否为连续的a1字节,若是则将当前位移后的并行数据作为bit对齐后的并行数据,完成bit对齐;否则将当前位移后的并行数据作为截取对象,返回步骤s2-2。

19、进一步地,步骤s3的具体方法包括以下子步骤:

20、s3-1、判断并行数据的初始位宽是否为8bit,若是则直接输出帧头信号并进入步骤s4;否则在bit对齐后的并行数据中查找a2字节,并进入步骤s3-2;

21、s3-2、判断第一个a2字节之前的数据是否存在非a1字节数据,若是则判定帧头有误,将当前bit对齐后的并行数据作为截取对象并返回步骤s2;否则根据当前的对齐情况获取对应的偏移量,即第二偏移量,并进入步骤s3-3;

22、s3-3、根据第二偏移量对当前bit对齐后的并行数据进行左移,并输出帧头信号指示每一帧的帧头位置。

23、进一步地,若对齐情况中包含m个a1字节,则将对应的偏移量设置为8×m个比特。

24、进一步地,步骤s4的具体方法为:

25、按字节对3×n个a1字节和3×n个a2字节进行持续的匹配,若匹配成功,则输出有效数据帧和有效帧头信号;否则将当前根据第二偏移量进行左移后的并行数据作为截取对象,返回步骤s2。

26、进一步地,步骤s5的具体方法为:

27、将未正确定帧之前的系统状态初始化为帧失步状态;

28、在帧失步状态中,若在250us内连续判断到正确的帧头,则将当前系统状态修改为定帧状态;

29、在定帧状态中,若在625us内连续判断到错误的帧头,则将当前系统状态修改为帧失步状态,判定当前传输数据为无效数据,将当前根据第二偏移量进行左移后的并行数据作为截取对象,返回步骤s2;

30、若帧失步状态持续时间大于3ms,则将当前系统状态修改为帧丢失状态;

31、在帧丢失状态中,若在1.25ms内连续判断到正确的帧头,则将帧丢失状态修改为定帧状态;

32、当当前系统状态为定帧状态时,判定当前的帧头为正确帧头,当前传输的数据均为有效数据,完成sdh线路的帧头检测。

33、提供一种可配置多速率的sdh线路的帧头检测系统,其包括cdr时钟恢复模块、bit对齐模块、配置管理模块、帧头检测模块、帧头监视模块和定帧状态判决模块;

34、cdr时钟恢复模块,用于将sdh线路上的串行数据流转换为并行数据;

35、bit对齐模块,用于将cdr时钟恢复模块输出的并行数据分别截取8个不同长度并缓存到对应的8个寄存器中,根据不同长度的数据命中a1字节的结果进行bit对齐;

36、配置管理模块,用于根据串行数据流速率对cdr时钟恢复模块和bit对齐模块进行配置;

37、帧头检测模块,用于对bit对齐模块输出的bit对齐后的并行数据进行基于a2字节的对齐,并输出帧头信号;

38、帧头监视模块,用于对帧头检测模块输出的每个帧头的准确性进行判断,输出有效数据帧和有效帧头信号;

39、定帧状态判决模块,用于根据帧头监视模块输出的有效帧头信号获取当前系统状态,并在当前系统状态为定帧状态时,判定检测到真实帧头。

40、本发明的有益效果为:本发明能够灵活配置用于检测多种sdh速率的帧头,并且对帧头检测的准确率高,且持续提供定帧和帧丢失状态的指示。

- 还没有人留言评论。精彩留言会获得点赞!