改善IIC通讯电路EMC性能的电路的制作方法

改善iic通讯电路emc性能的电路

技术领域

1.本实用新型涉及iic总线技术。

背景技术:

2.iic(inter-integrated circuit)的英文简称为iic bus,中文简称为集成电路总线,它是一种低成本串行通信总线,使用多主从架构,最初由飞利浦公司开发。iic总线有两根通信线,一根是串行数据线sda,另一根是串行时钟线scl。多个符合iic总线标准的器件都可以通过同一条iic总线进行通信,而不需要额外的地址译码器。每个连接到总线上的器件都有一个唯一的地址作为识别的标志,都可以发送或接收数据。iic总线通信速率受主机控制,最高传输速度可达5mbit/s。

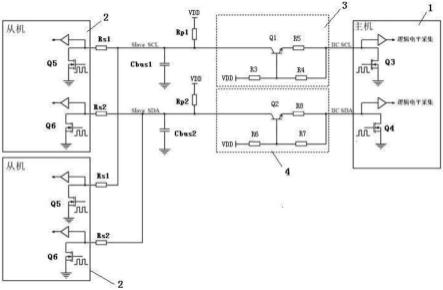

3.一般具有iic总线的器件其sda、scl引脚都为漏极开路结构。图1示出了现有的iic总线的电路原理图。如图1所示,主机、从机通过驱动芯片内部nmos(n-metal-oxide-semiconductor,n型金属-氧化物-半导体)管q3、q4、q5、q6等来实现数据的传输(应答)。在实际使用过程中,sda和scl信号线必须加上拉电阻rp,同时为了消除通讯线中耦合到的电压尖峰,会在通讯线sda、scl上串联电阻rs。总线空闲时sda、scl均保持高平。

4.通常,iic总线通讯电路中只有上拉电阻r

p

、串联电阻rs和总线电容cbus这几个器件,其工作过程为:nmos管q3、q4关断,v

dd

通过上拉电阻r

p

给总线电容cbus充电,如图2所示,上拉电阻rp和总线电容cbus这两者决定了波形的上升时间;nmos管q3、q4导通,总线电容cbus通过串联电阻rs放电,如图3所示,当总线电容cbus固定时,rs决定了通讯波形下降沿的时间。按照iic总线规范,同时也为了保证通讯的可靠性,通常上升时间tr和下降时间tf不能太长,低逻辑电平为0.3v

dd

,高逻辑电平为0.7v

dd

。

5.上升时间:

6.为了能够得到更好的emc(电磁兼容)性能,人们总是希望尽可能地延长上升时间和下降时间,上升时间比较容易更改,只需要增大总线电容cbus或者增大上拉电阻rp即可。

7.下降时间:

8.增加下降时间存在一个矛盾点,增大串联电阻rs的同时,根据电阻分压公式:

[0009][0010]

从机芯片接收到的低逻辑电平v

slavescl

也会跟着提高,当增大到一定程度(大于0.3v

dd

),通讯将不能正常进行。按照传统的硬件电路,总线电容放电电流尖峰带来的emi(electromagnetic interference,电磁干扰)问题很难规避。

技术实现要素:

[0011]

本实用新型所要解决的技术问题在于提供一种能够改善iic通讯电路的emc性能的电路。

[0012]

本实用新型实施例的改善iic通讯电路emc性能的电路,iic通讯电路包括主机、从

机、scl线和sda线,scl线通过上拉电阻rp1与系统电源vdd连接,并通过第一总线电容cbus1接地,sda线通过第二上拉电阻rp2与系统电源vdd连接,并通过第二总线电容cbus2接地,其特点在于,所述改善iic通讯电路emc性能的电路包括第一放电电路和第二放电电路;第一放电电路包括npn三极管q1、发射极电阻r5、分压电阻r3和分压电阻r4;npn三极管q1的集电极与scl总线连接,npn三极管q1的发射极与发射极电阻r5的一端连接;分压电阻r3的一端与系统电源vdd连接,分压电阻r3的另一端与分压电阻r4的一端的共接点连接于npn三极管q1的基极,分压电阻r4的另一端与发射极电阻r5的另一端的共接点连接于主机的scl引脚;第二放电电路包括npn三极管q2、发射极电阻r8、分压电阻r6和分压电阻r7;npn三极管q2的集电极与sda总线连接,npn三极管q2的发射极与发射极电阻r8的一端连接;分压电阻r6的一端与系统电源vdd连接,分压电阻r6的另一端与分压电阻r7的一端的共接点连接于npn三极管q2的基极,分压电阻r7的另一端与发射极电阻r8的另一端的共接点连接于主机的sda引脚。

[0013]

本实用新型至少具有以下优点:

[0014]

本实用新型实施例将现有的总线串联电阻替换成由阻容器件和三极管组成的放电电路,在获得更长的波形下降时间的同时,能使从机接收到的低逻辑电平的电压也更低,从而能达到更好的emi效果。

附图说明

[0015]

为了更清楚地说明本实用新型实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简要介绍,显而易见地,下面描述中的附图仅仅是本实用新型的一些实施例,对于本领域的普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。

[0016]

图1示出了现有的iic总线的电路原理示意图。

[0017]

图2示出了现有的iic总线释放时总线电容的充电路径示意图。

[0018]

图3示出了现有的iic总线发送数据时总线电容的放电路径示意图。

[0019]

图4示出了根据本实用新型第一实施例的改善iic通讯电路emc性能的电路的电路原理图。

[0020]

图5示出了根据本实用新型第二实施例的改善iic通讯电路emc性能的电路的电路原理图。

具体实施方式

[0021]

下面结合附图对本实用新型做出进一步说明。

[0022]

图4示出了根据本实用新型第一实施例的改善iic通讯电路emc性能的电路的电路原理图。请参考图4,iic通讯电路包括主机1、从机2、scl线、sda线,根据本实用新型第一实施例的改善iic通讯电路emc性能的电路第一放电电路3和第二放电电路4。

[0023]

scl线通过上拉电阻rp1与系统电源vdd连接,并通过第一总线电容cbus1接地,sda线通过第二上拉电阻rp2与系统电源vdd连接,并通过第二总线电容cbus2接地。从机2的scl引脚与scl线之间串联了串联电阻rs1,从机2的sda引脚与sda线之间串联了串联电阻rs2。

[0024]

第一放电电路3包括npn三极管q1、基极电容c2、发射极电阻r5、分压电阻r3和分压

电阻r4。npn三极管q1的集电极与scl总线连接,npn三极管q1的发射极与发射极电阻r5的一端连接。分压电阻r3的一端与系统电源vdd连接,分压电阻r3的另一端、基极电容c2的一端和分压电阻r4的一端的共接点连接于npn三极管q1的基极,分压电阻r4的另一端、基极电容c2的另一端和发射极电阻r5的另一端的共接点连接于主机1的scl引脚。基极电容c2与电阻r4并联连接。

[0025]

第二放电电路4包括npn三极管q2、基极电容c4、发射极电阻r8、分压电阻r6和分压电阻r7。npn三极管q2的集电极与sda总线连接,npn三极管q2的发射极与发射极电阻r8的一端连接。分压电阻r6的一端与系统电源vdd连接,分压电阻r6的另一端、基极电容c4的一端和分压电阻r7的一端的共接点连接于npn三极管q2的基极,分压电阻r7的另一端、基极电容c4的另一端和发射极电阻r8的另一端的共接点连接于主机1的sda引脚。基极电容c4与电阻r7并联连接。

[0026]

第一放电电路3和第二放电电路4的结构及工作原理均类似,以下仅以sda线为例,说明其在连接了第二放电电路之后的工作原理与工作过程。sda线的三个工作状态如下:

[0027]

状态1:总线释放过程,总线上所有的nmos管(包括nmos管q3、q4、q5、q6等)都处于关断状态,此时系统电源vdd通过上拉电阻rp2给总线电容cbus2充电,此时第二放电电路4中的npn三极管q2不工作;

[0028]

状态2:主机1向总线发送数据,与主机1的sda引脚相连的nmos管q4的导通瞬间,npn三极管q2工作在放大区,系统电源vdd通过分压电阻r6给基极电容c4充电,上拉电阻rp2为集电极电阻,r8为发射极电阻,随着基极电压上升,基极电流增加,npn三极管q2逐渐饱和,这期间三极管起到了类似于可变电阻器的作用,总线电容cbus2放电期间,第二放电电路的等效电阻由大到小,限制了总线电容cbus2的放电电流峰值。

[0029]

状态3:从机2向总线发送应答信号,此时从机2的与sda引脚相连的nmos管q6导通,主机1的nmos管q4关断,总线电平slave_sda被拉低,npn三极管q2的集电极正偏,npn三极管q2的基极电压为0.6v,主机1的与sda引脚相连的逻辑电平采集部分依然可以通过分压电阻r7读取到总线的电平状态,以此判断从机2是否应答,通讯能正常进行。

[0030]

图5示出了根据本实用新型第二实施例的改善iic通讯电路emc性能的电路。该第二实施例与第一实施例的主要区别在于,在第一放电电路3中未设置基极电容c2,在第二放电电路4中未设置基极电容c4。由于npn三极管q1、q2存在基极寄生电容,因此可以省略掉基极电容c2、c4,也能达到相近的效果。

[0031]

本实用新型实施例将现有的总线串联电阻替换成由阻容器件和三极管组成的放电电路,在获得更长的波形下降时间的同时,能使从机接收到的低逻辑电平的电压也更低,从而能达到更好的emi效果。相比于现有技术直接增大串联电阻阻值的方式,本实用新型实施例避免了低逻辑电平与高串联电阻值之间的矛盾。

[0032]

显然,本领域的技术人员可以对本实用新型进行各种改动和变型而不脱离本实用新型的精神和范围。这样,倘若本实用新型的这些修改和变型属于本实用新型权利要求及其等同技术的范围之内,则本实用新型也意图包含这些改动和变型在内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1