一种主板及交换机的制作方法

1.本实用新型涉及网络通信设备领域,特别是涉及一种主板及交换机。

背景技术:

2.路由交换机一种用于电(光)信号转发的网络设备,它可以为接入交换机的任意两个网络节点提供独享的电信号通路,交换机的作用为将一些机器连接起来组成一个局域网。随着云业务和大数据的应用深入,网络数据大流量传输成为人们越来越深入关注的焦点,交换机是网络数据传输中的核心设备。

3.目前传统交换机所提供的数据流量接口有限,限制了一定的应用场景,本实用新型提供了一种数据传输系统及内置该数据传输系统的交换机,其可提供6个对外万兆光口接口,同时通过phy芯片和网络变压器转换,对外提供3组,每组16个rj45千兆网口接口,极大的丰富了本实用新型提供的数据中心交换机应用场景。

4.另外,目前传统交换机多采用国外进口芯片,在特殊应用领域缺乏安全性,本实用新型提供的交换机的硬件结构布局采用国产化芯片中央处理器cpu,国产化内存,国产化phy芯片,实现了交换机核心器件的国内自主开发研制,设计实现100%的整机国产化率,实现了特殊应用场景的自主可控要求。

技术实现要素:

5.本实用新型的目的在于提供一种主板及交换机,旨在满足本领域现阶段云业务和大数据的应用深入应用的背景下,对交换机性能要求的提高。

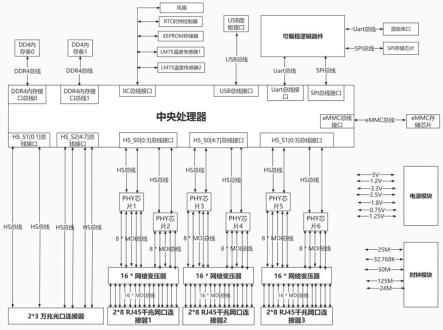

6.为了实现上述目的,本实用新型提供了一种主板,所述主板包括中央处理器、可编程逻辑器件、电源模块、时钟模块、phy芯片1、phy芯片2、phy芯片3、phy芯片4、phy芯片5和phy芯片6,所述中央处理器包括ddr4内存总线接口0、ddr4内存总线接口1、iic总线接口、usb总线接口、uart总线接口、spi总线接口、emmc总线接口、hs_s1[0:3]总线接口、hs_s0[4:7]总线接口、hs_s0[0:3]总线接口、hs_s2[4:7]总线接口和hs_s1[0:1]总线接口,所述中央处理器通过uart总线接口和spi总线接口与所述可编程逻辑器件连接。

[0007]

进一步的,所述中央处理器通过hs_s0[0:3]总线接口与phy芯片1和phy芯片2连接,所述phy芯片1和所述phy芯片2分别通过8*mdi总线与16*网络变压器连接,所述16*网络变压器通过16*mdi总线与2*8 rj45千兆网口连接器1连接。

[0008]

进一步的,所述中央处理器通过hs_s0[4:7]总线接口与phy芯片3和phy芯片4连接,所述phy芯片3和所述phy芯片4分别通过8*mdi总线与16*网络变压器连接,所述16*网络变压器通过16*mdi总线与2*8 rj45千兆网口连接器2连接。

[0009]

进一步的,所述中央处理器通过hs_s1[0:3]总线接口与phy芯片5和phy芯片6连接,所述phy芯片5和所述phy芯片6分别通过8*mdi总线与16*网络变压器连接,所述16*网络变压器通过16*mdi总线与2*8 rj45千兆网口连接器3连接。

[0010]

进一步的,所述中央处理器通过ddr4内存总线接口0与dd4内存条0连接,所述中央

处理器通过ddr4内存总线接口1与dd4内存条1连接。

[0011]

进一步的,所述中央处理器通过iic总线接口与风扇、rtc时钟控制器、eeprom存储器、lm75温度传感器1和lm75温度传感器2连接。

[0012]

进一步的,所述中央处理器通过usb总线接口与usb面板接口连接,所述中央处理器通过emmc总线接口与emmc存储芯片连接。

[0013]

进一步的,所述可编程逻辑器件通过uart总线与面板串口连接,所述可编程逻辑器件通过spi总线与spi存储芯片连接。

[0014]

进一步的,所述中央处理器通过hs_s2[4:7]总线接口和hs_s1[0:1]总线接口与2*3万兆光口连接器连接。

[0015]

进一步的,提供一种交换机,包括至少上述任一项所述的主板。

[0016]

相较于现有技术,本实用新型具有以下优点:提供了大量且丰富的接口,极大的丰富了本实用新型提供的数据中心交换机应用场景;实现了交换机核心器件的国内自主开发研制,设计实现100%的整机国产化率,实现了特殊应用场景的自主可控要求。

附图说明

[0017]

为了更清楚地说明本技术实施例的技术方案,下面将对本技术实施例中所需要使用的附图作简单地介绍,应当理解,以下附图仅示出了本技术的某些实施例,因此不应被看作是对范围的限定,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他相关的附图。

[0018]

图1本实用新型的网络数据处理系统的结构示意图。

具体实施方式

[0019]

以下通过特定的具体实例说明本实用新型的实施方式,本领域技术人员可由本说明书所揭露的内容轻易地了解本实用新型的其他优点与功效。本实用新型还可以通过另外不同的具体实施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点与应用,在没有背离本实用新型的精神下进行各种修饰或改变。

[0020]

下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行描述。

[0021]

应注意到:相似的标号和字母在下面的附图中表示类似项,因此,一旦某一项在一个附图中被定义,则在随后的附图中不需要对其进行进一步定义和解释。同时,在本技术的描述中,术语“第一”、“第二”等仅用于区分描述,而不能理解为指示或暗示相对重要性。

[0022]

请参阅图1。需要说明的是,本实施例中所提供的图示仅以示意方式说明本实用新型的基本构想,遂图式中仅显示与本实用新型中有关的组件而非按照实际实施时的组件数目、形状及尺寸绘制,其实际实施时各组件的型态、数量及比例可为一种随意的改变,且其组件布局型态也可能更为复杂。

[0023]

本实用新型所采用的中央处理器使用国产飞腾cpuft2000/4,phy芯片使用国产盛科的ctc21108,内存使用紫光国芯的scc04gx03a1f1c-26v,可编程逻辑器件使用紫光同创的pgc1kg_6cfbg256,网络变压器使用深圳市联泰兴的hst-88029dr,spi存储芯片使用北京兆易创新科技的gd25q128esigr,eeprom使用上海复旦微电子fm24c128d-so-t-g-ax,电源模块主要使用无锡紫光微电子的sm53319、矽力杰半导体sq24302、杰华特微电子的

jwh5276,时钟模块主要使用宁波奥拉的aura5410、au5411a-qmr、au5410a-qmr,网口连接器使用乐清市华信电子有限公司的8805-62g8817223,光口连接器使用庆虹电子有限公司的760445002。

[0024]

中央处理器作为整个系统的核心,实现系统管理,接口配置,协议报文处理等功能。中央处理器内置2个ddr4sdram控制器,其中ddr4内存控制器0外接1片ddr4内存条0,ddr4内存控制器1外接1片ddr4内存条1。

[0025]

中央处理器支持支持4组高速总线接口hs_s0、hs_s1、hs_s2、hs_s3,其中hs_s1[0:1]总线和hs_s2[4:7]总线连接到前面板扩展2*3万兆光口。hs_s0[0:3]总线接口通过4组hs总线连接到phy芯片1和phy芯片2,扩展16组mdi总线,通过网络变压器连接到前面板2*8rj45千兆网卡连接器1上。hs_s0[4:7]总线接口通过4组hs总线连接到phy芯片3和phy芯片4,扩展16组mdi总线,通过网络变压器连接到前面板2*8rj45千兆网卡连接器2上。hs_s1[0:3]总线接口通过4组hs总线连接到phy芯片5和phy芯片6,扩展16组mdi总线,通过网络变压器连接到前面板2*8rj45千兆网卡连接器3上。

[0026]

中央处理器可扩展1组iic总线接口,iic总线接口连接rtc时钟芯片记录当前时间,连接eeprom存储设备生产制造信息,连接2pcs温度传感器实现风扇转速调控,其中温度传感器1放到设备入风口,温度传感器2放到设备出风口。

[0027]

中央处理器的uart总线连接到可编程逻辑器件上,通过可编程逻辑器件进行电压切换,可编程逻辑器件引出uart总线连接到面板串口。

[0028]

中央处理器的spi总线连接到可编程逻辑器件上,通过可编程逻辑器件进行电压切换,可编程逻辑器件引出spi总线连接spi存储芯片,存储系统启动程序。

[0029]

中央处理器的emmc总线连接emmc存储芯片存储操作系统。

[0030]

中央处理器的usb总线连接到面板usb连接器扩展1组usb接口。

[0031]

系统使用dcdc电源模块生成5v、1.2v、3.3v、2.5v、1.8v、0.75v、1.25v等各芯片所需的电压,使用时钟模块生成25mhz、125mhz、50mhz.24mhz、32.768khz各芯片所需的时钟。

[0032]

本实用新型提供了一种主板,所述主板包括中央处理器、可编程逻辑器件、电源模块、时钟模块、phy芯片1、phy芯片2、phy芯片3、phy芯片4、phy芯片5和phy芯片6,所述中央处理器包括ddr4内存总线接口0、ddr4内存总线接口1、iic总线接口、usb总线接口、uart总线接口、spi总线接口、emmc总线接口、hs_s1[0:3]总线接口、hs_s0[4:7]总线接口、hs_s0[0:3]总线接口、hs_s2[4:7]总线接口和hs_s1[0:1]总线接口,所述中央处理器通过uart总线接口和spi总线接口与所述可编程逻辑器件连接。

[0033]

进一步的,所述中央处理器通过hs_s0[0:3]总线接口与phy芯片1和phy芯片2连接,所述phy芯片1和所述phy芯片2分别通过8*mdi总线与16*网络变压器连接,所述16*网络变压器通过16*mdi总线与2*8 rj45千兆网口连接器1连接。

[0034]

进一步的,所述中央处理器通过hs_s0[4:7]总线接口与phy芯片3和phy芯片4连接,所述phy芯片3和所述phy芯片4分别通过8*mdi总线与16*网络变压器连接,所述16*网络变压器通过16*mdi总线与2*8 rj45千兆网口连接器2连接。

[0035]

进一步的,所述中央处理器通过hs_s1[0:3]总线接口与phy芯片5和phy芯片6连接,所述phy芯片5和所述phy芯片6分别通过8*mdi总线与16*网络变压器连接,所述16*网络变压器通过16*mdi总线与2*8 rj45千兆网口连接器3连接。

[0036]

进一步的,所述中央处理器通过ddr4内存总线接口0与dd4内存条0连接,所述中央处理器通过ddr4内存总线接口1与dd4内存条1连接。

[0037]

进一步的,所述中央处理器通过iic总线接口与风扇、rtc时钟控制器、eeprom存储器、lm75温度传感器1和lm75温度传感器2连接。

[0038]

进一步的,所述中央处理器通过usb总线接口与usb面板接口连接,所述中央处理器通过emmc总线接口与emmc存储芯片连接。

[0039]

进一步的,所述可编程逻辑器件通过uart总线与面板串口连接,所述可编程逻辑器件通过spi总线与spi存储芯片连接。

[0040]

进一步的,所述中央处理器通过hs_s2[4:7]总线接口和hs_s1[0:1]总线接口与2*3万兆光口连接器连接。

[0041]

提供一种交换机,所述交换机至少包括上述的主板。交换机其他的硬件结构不做具体限定。本实用新型提供的交换机具有一般交换机所具备的外壳、天线等相关必要硬件结构。

[0042]

以上所描述的实施例仅仅是本实用新型一部分实施例,而不是全部的实施例。通常在此处及附图中描述和示出的本实用新型实施例的组件可以以各种不同的配置来布置和设计。因此,以下对在附图中提供的本实用新型的实施例的详细描述并非旨在限制要求保护的本实用新型的范围,而是仅仅表示本实用新型的选定实施例。基于本实用新型的实施例,本领域技术人员在没有做出创造性劳动的前提下所获得的所有其他变化或替换,都属于本实用新型保护的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1