一种红外热成像系统的制作方法

1.本技术涉及成像系统领域,特别是涉及一种红外热成像系统。

背景技术:

2.在自然界中,一切物体都会辐射红外线,这种红外线辐射是基于任何物体在常规环境下都会产生自身分子和原子无规则的运动,并不停的辐射出热红外能量。因此红外热成像技术是利用红外传感其采集被测目标的红外热辐射能量,通过波长转换技术将热辐射能量转换为可视化图像,图像中不同颜色代表被测物体的不同温度,从而实现观测与测温。热成像应用于安防、防疫测温、国家禁捕、工业测温等各个方面。

3.目前,普遍应用于热成像探测器的都是采用单fpga模式,此模式集成控制、通信与图像处理。例如,专利cn206712951u公开了一种基于图像复原的主动红外夜视辅助驾驶系统,公开了采用对红外线采集到的图像进行基于fpga+dsp实时图像复原。利用配置芯片接收实时采集图像,再传送fpga模块进行图像的预处理,fpga模块再传送至dsp进行图像复原处理,复原处理后的图像再通过fpga传送至图像显示模块的显示屏上。

4.热成像探测器工作环境较为复杂,不同环境,图像效果各有差异,单fpga模式受限于资源限制问题,集成图像处理算法有限,对于后续新算法实现较为困难,系统可持续性与扩展性较差,不利于后期图像的优化。当需要添加新算法和算法升级时,由于单fpga处理器内部有限的逻辑资源和存储资源,导致图像效果优化空间小,可扩展性差,并且不具有高分率探测器兼容性,不具有通用性,无法满足后续图像效果的优化及高分辨率探测器的兼容。日益增多的算法处理与优化需求对图像处理系统提出了较高的要求,并且对于高分辨率探测器(1280*1024),往往需要更换芯片与硬件。

5.针对相关技术中存在单fpga模式的红外线热成像系统不能完成复杂算法的升级与新算法的添加,导致图像效果优化空间小,可扩展性差,不能兼容高分辨率探测器的问题,目前还没有提出有效的解决方案。

技术实现要素:

6.在本实施例中提供了一种红外热成像系统,以解决相关技术中单fpga模式的红外线热成像系统不能完成复杂算法的升级与新算法的添加,导致图像效果优化空间小,可扩展性差,不能兼容高分辨率探测器的问题。

7.第一个方面,在本实施例中提供了一种红外热成像系统,所述红外热成像系统包括图像采集单元、控制单元和图像处理单元,所述图像采集单元分别与所述控制单元和所述图像处理单元连接;所述图像处理单元与所述控制单元连接;

8.所述图像处理单元,包括:至少两个fpga芯片,所述fpga芯片之间通过其内部通信接口连接。

9.在其中的一些实施例中,所述图像处理单元包括第一fpga芯片和第二fpga芯片,所述第一fpga芯片和第二fpga芯片通过其内部通信接口连接,所述fpga芯片包括ddr模块;

10.所述红外热成像系统还包括dsp模块,所述dsp模块与所述第一fpga芯片通信连接。

11.在其中的一些实施例中,所述红外热成像系统还包括显示模块,所述dsp模块与所述显示模块通信连接。

12.在其中的一些实施例中,所述第二fpga芯片与所述图像采集单元连接。

13.在其中的一些实施例中,所述红外热成像系统还包括快门模块、存储器、控制器模块和温度传感器,所述快门模块、所述存储器、所述控制器模块和所述温度传感器分别与所述控制单元连接。

14.在其中的一些实施例中,所述控制单元通过spi接口与所述存储器连接,所述控制单元通过iic接口或spi接口与所述控制器模块连接,所述控制单元通过iic接口与所述温度传感器连接,所述控制单元通过uart接口与所述dsp模块连接。

15.在其中的一些实施例中,所述控制单元通过iic接口与所述图像采集单元连接。

16.在其中的一些实施例中,所述控制单元通过spi接口与所述fpga芯片通信连接。

17.在其中的一些实施例中,所述控制器模块为tec控制模块。

18.在其中的一些实施例中,所述图像处理单元还包括通信接口模块,所述fpga芯片通过所述通信接口模块与所述显示模块连接。

19.与相关技术相比,在本实施例中提供的一种红外热成像系统,通过双fpga模式,扩大了一倍资源,解决了热成像后续扩展图像处理算法,优化图像的需求,同时兼容高分辨率探测器。

20.本技术的一个或多个实施例的细节在以下附图和描述中提出,以使本技术的其他特征、目的和优点更加简明易懂。

附图说明

21.此处所说明的附图用来提供对本技术的进一步理解,构成本技术的一部分,本技术的示意性实施例及其说明用于解释本技术,并不构成对本技术的不当限定。在附图中:

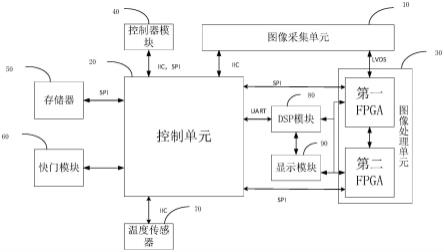

22.图1是本实施例的一种红外热成像系统的结构框图。

23.图2是本实施例的另一种红外热成像系统的结构框图。

24.图3是本优选实施例的一种红外热成像系统的结构框图。

25.图4是本优选实施例的图像处理单元处理数据的流程图。

具体实施方式

26.为更清楚地理解本技术的目的、技术方案和优点,下面结合附图和实施例,对本技术进行了描述和说明。

27.除另作定义外,本技术所涉及的技术术语或者科学术语应具有本技术所属技术领域具备一般技能的人所理解的一般含义。在本技术中的“一”、“一个”、“一种”、“该”、“这些”等类似的词并不表示数量上的限制,它们可以是单数或者复数。在本技术中所涉及的术语“包括”、“包含”、“具有”及其任何变体,其目的是涵盖不排他的包含;例如,包含一系列步骤或模块(单元)的过程、方法和系统、产品或设备并未限定于列出的步骤或模块(单元),而可包括未列出的步骤或模块(单元),或者可包括这些过程、方法、产品或设备固有的其他步骤

或模块(单元)。在本技术中所涉及的“连接”、“相连”、“耦接”等类似的词语并不限定于物理的或机械连接,而可以包括电气连接,无论是直接连接还是间接连接。在本技术中所涉及的“多个”是指两个或两个以上。“和/或”描述关联对象的关联关系,表示可以存在三种关系,例如,“a和/或b”可以表示:单独存在a,同时存在a和b,单独存在b这三种情况。通常情况下,字符“/”表示前后关联的对象是一种“或”的关系。在本技术中所涉及的术语“第一”、“第二”、“第三”等,只是对相似对象进行区分,并不代表针对对象的特定排序。

28.在本实施例中提供了一种红外热成像系统,图1是本实施例的红外热成像系统的结构框图,如图1所示,该系统包括:图像采集单元10、控制单元20和图像处理单元30,图像采集单元10分别与控制单元20、图像处理单元30连接;图像处理单元30与控制单元20连接。

29.图像处理单元30,包括:至少两个fpga芯片,两个fpga芯片之间通过其内部通信接口连接。

30.具体的,红外图像处理系统的核心是其硬件电路,传统的红外成像及处理电路大多只有成像以及简单的处理及采集功能,大多依托dsp芯片作为核心器件,控制图像采集,存储和运算处理,其特点是依靠处理进行串行化的处理,但在一些包含复杂算法和实时高流量的数字图像应用中,dsp芯片资源无法满足要求。还有一些其他设计,采用了dsp加fpga的处理器架构,dsp作为控制和核心运算器件,fpga作为协处理器件,但fpga的数字运算能力并未得到充分体现,实现同样功能硬件成本也相应更高。fpga具备强大的并行处理能力,内含上百个mac单元,达到系统级集成度的单片fpga芯片已足以提供足够的数字处理能力,处理器业界认为,运算强度在低于5gmacs时,使用传统dsp芯片较容易实现,反之则fpga具有更多优势。

31.具体的,在本实施例中图像处理单元采用fpga芯片的数量可根据图像处理单元中相关算法的需求设置来实现fpga芯片数量的增减,也就是说可以根据图像处理单元中相关算法的需求对fpga芯片进行串形扩展来搭建一个流水线架构。

32.具体的,在基于fpga芯片的基础上搭建一个流水线架构,在流水线架构下每一级fpga芯片都接收前一级送来的数据进行处理,然后将结果保存在ddr芯片内。在下一个时钟周期时,后一级处理fpga芯片从前一级的ddr芯片中取出缓存的数据进行处理。这样,在每一个时钟周期,流水线架构中的每一个fpga芯片从接收任务信号直到完成执行计算任务,而不会像纯并行结构那样,执行完处理任务的fpga芯片闲置直到完成全部处理后接收到新的数据才会继续工作。在fpga芯片流水线架构中,一个大任务被分解成复杂性大致相同的小任务,各部分任务在流水线上同时执行,整个任务的速度取决于执行时间最长的部分任务执行时间。因为,fpga芯片具有处理速度高的特点,fpga芯片流水线架构是以不同事务的并行处理为特征,而并行阵列结构是以相同事务的并行处理为特征。在采用并行流水线架构来设计图像处理单元,满足大量数据处理的实时性要求,以实现红外热成像系统中对于图像处理系统高精度、高速化和高度集成化的需求。

33.在本实施例中还提供了一种红外热成像系统,图2是本实施例的红外热成像系统的结构框图,如图2所示,该系统包括:图像采集单元10、控制单元20和图像处理单元30,图像采集单元10分别与控制单元20、图像处理单元30连接;图像处理单元30与控制单元20连接;图像处理单元30,包括:至少两个fpga芯片,所述fpga芯片之间通过其内部通信接口连接。

34.具体的,在本实施例中图像采集单元10为热成像探测器,物体发出的红外辐射通过光学器件聚集到探测器上,探测器把辐射转换成电信号,电信号通过图像处理单元30将被测目标表面的热信息瞬间可视化,即热像图。

35.在其中的一些实施例中,图像处理单元30包括第一fpga芯片301和第二fpga芯片302,第一fpga芯片301和第二fpga芯片302通过其内部通信接口连接,fpga芯片包括ddr模块(图中未画出);红外热成像系统还包括dsp模块80,dsp模块80与第一fpga芯片301通信连接。

36.具体的,第一fpga芯片301从热成像探测器采集第一数据,并对第一数据进行校正降噪,实现数据raw域处理,第一fpga芯片301通过内部协议将第一数据转为第二数据传输到第二fpga芯片302,第二fpga芯片302完成数据yuv域的处理,并输出视频流。

37.具体的,第一fpga芯片301从热成像探测器采集第一数据,对第一数据依次经过非均性校正、坏点坏列校正、锅盖校正得到第三数据,将第三数据依次经过3d降噪、竖条纹降噪、2d降噪得到第二数据,实现数据raw域处理。

38.具体的,第一数据为14bit数据,第二数据为8bit数据。

39.具体的,从探测器流出的数据为14bit,经过探测器内部协议将模拟信号数据转换成数字信号数据,数字信号数据流入接口时序,接口时序将数字信号数据再一次回流进探测器内,从而完成数字信号数据的振幅校正。经校正后的数字信号数据再一次通过lvds接口流入第一fpga芯片301中,第一fpga芯片301内对该数字信号数据进行raw域相关算法处理。具体的过程如下,从接口时序流出的数据流进非均匀校正模块,经非均匀校正模块校正的数字信号数据流进给坏点坏列校正模块,经过坏点坏列模块校正的数据再一次流进锅盖校正模块,经锅盖校正模块校正的数字信号数据流进3d降噪模块,经3d降噪模块降噪的数字信号数据再一次流入竖条纹降噪模块,经竖条纹降噪模块降噪完的数字信号数据再次流入2d降噪模块进行再次降噪,经过一系列的数据校正,从而完成图像raw域的处理。

40.具体的,第一fpga芯片301将第二数据传输到第二fpga芯片302,第二fpga芯片302包括drc模块,第二fpga芯片302接收到的第二数据先经过drc模块进行处理,进行亮度、对比度、锐度、细节增强、边缘增强等相关算法的实现,处理完的数据后经过伪彩处理、osd叠加处理,最后第二fpga芯片输出视频流。

41.具体的,从探测器流出的14bit数据经过第一fpga芯片301的内部协议通过无损硬件压缩系统进行压缩,将从探测器流出的14bit数据压缩成8bit数据。从而使经过第一fpga芯片301压缩后的8bit数据符合fpga芯片对yuv422处理的格式,8bit数据流入第二fpga芯片302中进行yuv域处理以及图像输出。具体过程如下,8bit数据经过drc模块,该drc模块对数据进行亮度、对比度、锐度、细节增强、边缘增强等相关算法的处理。经drc模块处理完的数据再一次流进伪彩模块,经过伪彩模块处理的数据流进osd叠加模块,经过osd叠加模块处理完成的视频流数据通过通信模块在上位机图像显示。

42.具体的,ddr模块主要用来存储图像以及校正数据。

43.在其中的一些实施例中,红外热成像系统还包括显示模块90,dsp模块80与显示模块90通信连接。

44.在其中的一些实施例中,红外热成像系统还包括快门模块60、存储器50、控制器模块40和温度传感器70,快门模块60、存储器50、控制器模块40和温度传感器70分别与控制单

元20连接。

45.具体的,控制单元20在热成像探测器开机时,将从存储器50读取的非均匀性校正数据、坏点坏列数据、锅盖校正数据写入第一fpga芯片301,且在每次快门就进行一次非均匀性校正。

46.具体的,存储器50为flash存储器主要用来存储一些非均匀校正参数以及其他需要掉电存储的数据。

47.在其中的一些实施例中,控制单元20通过spi接口与存储器连接,控制单元20通过iic接口或spi接口与控制器模块40连接,控制单元20通过iic接口与温度传感器70连接,控制单元20通过uart接口与dsp模块80连接。

48.具体的,控制单元20通过通用异步收发器与数字信号处理器dsp模块80进行信息交互。

49.具体的,所述控制单元20通过iic读取温度传感器70的温度值,通过spi通信,结合专用驱动芯片对所述热成像探测器进行温度调节控制。

50.在其中的一些实施例中,控制单元20通过iic接口与图像采集单元10连接。

51.具体的,控制单元20通过iic通信协议与热成像探测器进行交互,对热成像探测器进行相关配置的设置及关键参数的读取。

52.在其中的一些实施例中,控制单元20通过spi接口与fpga芯片通信连接。

53.具体的,控制单元20通过spi通信,分别与第一fpga芯片301、第二fpga芯片302进行交互,设置相关配置,实时读取相关参数。

54.在其中的一些实施例中,控制器模块40为tec控制模块。

55.具体的,控制单元20通过spi通信,结合专用驱动芯片对热成像探测器进行tec温度调节控制,保持热成像探测器温度稳定,图像效果保持稳定。

56.在其中的一些实施例中,图像处理单元30还包括通信接口模块,fpga芯片通过通信接口模块与显示模块连接。

57.通过双fpga模式,利用第一fpga芯片301实现探测器的数据采集及图像raw域处理功能,利用第二fpga芯片302实现图像输出及yuv域的处理,扩大了一倍资源,解决了热成像后续扩展图像处理算法,优化图像的需求,同时兼容高分辨率探测器,满足大量数据处理的实时性要求,实现了红外热成像系统中对于图像处理系统高精度、高速化和高度集成化的需求。

58.下面通过优选实施例对本实施例进行描述和说明。

59.图3是本优选实施例的红外热成像系统的结构框图,如图3所示,红外热成像系统主要有单片机4,第一fpga芯片1和第二fpga芯片2。进一步红外热成像系统包含存储器9,tec控制模块8、温感模块7、快门模块11、图像显示器5。选用的fpga芯片自带ddr模块,该存储器9可以是flash芯片。

60.单片机4主要实现整体控制,通过spi与存储器9进行交互,保存关键配置。通过iic与热成像探测器3进行交互,探测器3内含集成a/d转换模块,对探测器3的相关配置进行设置及关键参数的读取,通过uart通信与dsp模块进行交互。通过iic读取温感模块7,实时观察。通过spi通信,结合专用驱动芯片对探测器3进行tec温度调节控制,保持探测器3温度稳定,图像效果保持稳定。红外热成像系统通过spi通信,对两片fpga进行交互,设置相关配

置,实时读取相关参数。

61.上述ad转换模块将多路模拟信号输出转换为数字电平信号,送达第一fpga芯片1。

62.如图4所示,第一fpga芯片1主要实现探测器3数据采集及图像raw域处理功能。从探测器3采集数据并对探测器3进行ddac校正,此时采集的数据为14bit。将采集的数据进行非均性校正,将校正完的14bit数据发送给坏点坏列校正模块。对于坏点坏列校正完的数据发送给锅盖校正模块。以此类推,校正完的数据依次发送给3d降噪,竖条纹降噪、2d降噪。每次探测器开机,单片机将会把存储器9读取的非均匀性校正数据、坏点坏列数据、锅盖校正数据写入第一fpga芯片1的arm里,且每次快门就进行一次非均匀性校正,以便达到图像最佳效果。

63.第二fpga芯片2主要实现图像输出及yuv域的处理。同时可以输出raw和yuv数据。此时第一fpga芯片1通过内部协议将14bit数据转为8bit数据到第二fpga芯片2。第二fpga芯片2的算法都将在8bit数据进行处理。首先是drc模块,主要功能为亮度、对比度、锐度、细节增强、边缘增强等相关算法的实现。在处理完的数据上进行伪彩处理、osd叠加,最后输出视频流。对于视频流数据可以通过通信模块进行上位机图像显示,也可以外接dsp模块处理其他相关功能,扩展性强。

64.需要说明的是,在上述流程中或者附图的流程图中示出的步骤可以在诸如一组计算机可执行指令的计算机系统中执行,并且,虽然在流程图中示出了逻辑顺序,但是在某些情况下,可以以不同于此处的顺序执行所示出或描述的步骤。

65.需要说明的是,在本实施例中的具体示例可以参考上述实施例及可选实施方式中所描述的示例,在本实施例中不再赘述。

66.应该明白的是,这里描述的具体实施例只是用来解释这个应用,而不是用来对它进行限定。根据本技术提供的实施例,本领域普通技术人员在不进行创造性劳动的情况下得到的所有其它实施例,均属本技术保护范围。

67.显然,附图只是本技术的一些例子或实施例,对本领域的普通技术人员来说,也可以根据这些附图将本技术适用于其他类似情况,但无需付出创造性劳动。另外,可以理解的是,尽管在此开发过程中所做的工作可能是复杂和漫长的,但是,对于本领域的普通技术人员来说,根据本技术披露的技术内容进行的某些设计、制造或生产等更改仅是常规的技术手段,不应被视为本技术公开的内容不足。

[0068]“实施例”一词在本技术中指的是结合实施例描述的具体特征、结构或特性可以包括在本技术的至少一个实施例中。该短语出现在说明书中的各个位置并不一定意味着相同的实施例,也不意味着与其它实施例相互排斥而具有独立性或可供选择。本领域的普通技术人员能够清楚或隐含地理解的是,本技术中描述的实施例在没有冲突的情况下,可以与其它实施例结合。

[0069]

以上所述实施例仅表达了本技术的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对专利保护范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本技术构思的前提下,还可以做出若干变形和改进,这些都属于本技术的保护范围。因此,本技术的保护范围应以所附权利要求为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1