一种多电源供电结构及像素驱动电路的制作方法

1.本发明涉及图像传感器技术领域,具体涉及一种多电源供电结构及像素驱动电路。

背景技术:

2.高分辨率是图像传感器的一个重要发展方向,而高分辨率也意味着像素阵列的面积在不断增大,由于像素的电源线和地线在像素阵列中走线过长,由此发生短路的概率也不断增加,最终导致读出的有效像素有损失,影响成像质量。

3.在像素结构中,传输晶体管受tx信号的控制,将光电二极管pd处的电荷传输到浮动扩散区fd处,tx的电位只是由芯片内部的电荷泵来供电,这样就导致电荷泵产生较大的负载电流,为了保证电荷泵输出的稳定性就需要增加电荷泵的面积,这对超大规模像素阵列的图像传感器而言,电荷泵的面积较大是不期望发生的。

4.鉴于此,需要提供一种能够保证图像传感器高分辨率,但电荷泵面积不随之增加的像素驱动电路。

技术实现要素:

5.本实用新型所要解决的技术问题是像素驱动电路只是由电荷泵来供电,导致大像素图像传感器的电荷泵面积不断增大。

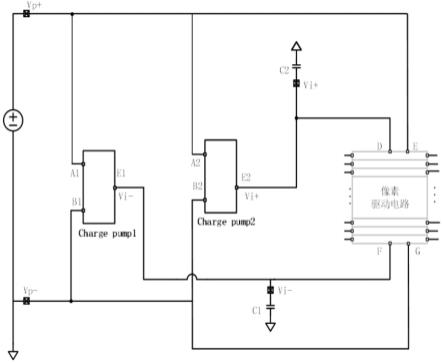

6.为解决上述问题,第一方面,本实用新型提供一种多电源供电结构,包括外部电源vp+、外部电源vp-、外部电容c1、外部电容c2、电荷泵1、电荷泵2和像素驱动电路,其中,所述外部电源vp+分别与电荷泵1的输入端a1、电荷泵2的输入端a2、像素驱动电路的输入端e连接,所述外部电源vp-分别与电荷泵1的输入端b1、电荷泵2的输入端b2、像素驱动电路的输入端g连接,所述电荷泵1的输出端e1与所述像素驱动电路的输入端f连接,所述电荷泵2的输出端e2与所述像素驱动电路的输入端d连接;所述电荷泵1的输出电压为vi-,所述电荷泵2的输出电压为vi+;所述电荷泵1的输出端e1与所述外部电容c1的一端连接,c1的另一端接地;所述电荷泵2的输出端e2与所述外部电容c2的一端连接,c2 的另一端接地。

7.进一步地,所述像素驱动电路,包括电平转换单元、逻辑电路、输出级电路,其中,所述电平转换单元接入控制信号,所述电平转换单元与所述逻辑电路、所述输出级电路依次连接。

8.进一步地,所述输出级电路包括p沟道型mos管mp1和mp2,n沟道型mos管mn1 和mn2;所述pmos管mp1的源极接外部电源vp+,漏极接所述mp2的漏极,所述mp2 的源极接vi+;所述nmos管mn1的源极接vp-,漏极接mn2的漏极,所述mn2的源极接vi-;所述mp1、mp2、mn1、mn2的栅极分别接所述逻辑电路;所述mp1的漏极、所述mp2的漏极、所述mn1的漏极、所述mn2的漏极的公共端接输出信号线tx。

9.进一步地,所述电平转换单元包括第一正升压电平转换器、第二正升压电平转换器、第三正升压电平转换器,第一负升压电平转换器、第二负升压电平转换器;所述逻辑电

路包括第一与非门nand1、第二与非门nand2,与门and,或非门nor;

10.所述第一升压电平转换器的同相输出端out接所述第二与非门nand2的输入端p6,其反相输出端xout接所述第一与非门nand1的输入端p4;所述第二正升压电平转换器的同相输出端out分别接第一与非门nand1的输入端p2、第二与非门nand2的输入端p5;所述第一负升压电平转换器的同相输出端out分别接与门and的输入端n2、或非门nor 的输入端n4;所述第二负升压电平转换器的同向输出端out接或非门nor的输入端n5;所述第三正升压电平转换器的反相输出端xout接第一与非门nand1的输入端p3;

11.所述第一与非门nand1的输出端经节点sp2与所述mp2的栅极连接;所述第二与非门 nand2的输出端经节点sp1与所述mp1的栅极连接;所述与门and的输出端经节点sn1 与所述mn1的栅极连接;所述或非门nor的输出端经sn2与mn2的栅极连接;

12.所述第一升压电平转换器的输入端接信号线tx_p_select_logic,所述第二正升压电平转换器和所述第一负升压电平转换器的输入端同时接信号线tx_logic,所述第二负升压电平转换器和所述第三正升压电平转换器的输入端同时接信号线tx_n_select_logic。

13.与传统的像素驱动电路的供电结构相比,本实用新型提供的多电源供电结构,能够降低对电荷泵供电的需求,压缩电荷泵所占面积,进而降低芯片成本。

14.为让本技术的上述和其他目的、特征和优点能更明显易懂,下文特举较佳实施例,并配合所附图式,作详细说明如下。

附图说明

15.此处所说明的附图用来提供对本实用新型实施例的进一步理解,构成本技术的一部分,并不构成对本实用新型实施例的限定。在附图中:

16.图1是本实用新型的多电源供电结构的示意图;

17.图2是本实用新型的像素驱动电路的结构示意图;

18.图3是本实用新型的像素驱动电路的输入与输出的逻辑关系示意图。

具体实施方式

19.为使本实用新型的目的、技术方案和优点更加清楚,下面将结合附图对本实用新型的技术方案进行清楚、完整地描述,显然,所描述的实施例是本实用新型的一部分实施例,而不是全部的实施例,仅用于解释本实用新型,而不用于限定本实用新型所保护的技术方案。基于本实用新型中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本实用新型保护的范围。

20.本实用新型是为了解决像素驱动电路只是由电荷泵来供电,导致大像素图像传感器的电荷泵面积不断增大。通过采用多电源为像素驱动电路供电的方式,能够降低对电荷泵供电的需求,减小电荷泵所占面积。

21.下面结合实施例和附图对本实用新型结构及其工作方法做详细说明。

22.如图1所示,本实用新型提供的多电源供电结构,包括外部电源vp+、外部电源vp-、外部电容c1、外部电容c2、电荷泵1、电荷泵2和像素驱动电路,其中,所述外部电源vp+ 分别与电荷泵1的输入端a1、电荷泵2的输入端a2、像素驱动电路的输入端e连接,所述外部电源

vp-分别与电荷泵1的输入端b1、电荷泵2的输入端b2、像素驱动电路的输入端g 连接,所述电荷泵1的输出端e1与所述像素驱动电路的输入端f连接,所述电荷泵2的输出端e2与所述像素驱动电路的输入端d连接;所述电荷泵1的输出电压为vi-,所述电荷泵 2的输出电压为vi+;所述电荷泵1的输出端e1与所述外部电容c1的一端连接,c1的另一端接地;所述电荷泵2的输出端e2与所述外部电容c2的一端连接,c2的另一端接地。

23.作为一种可能的实施方式,如图2所示,所述像素驱动电路的结构,包括电平转换单元、逻辑电路、输出级电路,其中,所述电平转换单元包括第一正升压电平转换器、第二正升压电平转换器、第三正升压电平转换器、第一负升压电平转换器、第二负升压电平转换器;所述逻辑电路包括第一与非门nand1、第二与非门nand2,与门and,或非门nor,所述输出级电路包括p沟道型mos管mp1和mp2,n沟道型mos管mn1和mn2;

24.所述第一正升压电平转换器的同相输出端out接所述第二与非门nand2的输入端p6,其反相输出端xout接所述与第一与非门nand1的输入端p4;所述第二正升压电平转换器的同相输出端out分别接第一与非门nand1的输入端p2、第二与非门nand2的输入端 p5;所述第一负升压电平转换器的同相输出端out分别接与门and的输入端n2、或非门 nor的输入端n4;所述第二负升压电平转换器的同向输出端out接或非门nor的输入端n5;所述第三正升压电平转换器的反相输出端xout接第一与非门nand1的输入端p3;

25.所述第一与非门nand1的输出端经节点sp2与所述mp2的栅极连接;所述与第二非门 nand2的输出端经节点sp1与所述mp1的栅极连接;所述与门and的输出端经节点sn1 与所述mn1的栅极连接;所述或非门nor的输出端经sn2与mn2的栅极连接;

26.所述pmos管mp1的源极接外部电源vp+,漏极接所述mp2的漏极,所述mp2的源极接vi+;所述nmos管mn1的源极接vp-,漏极接mn2的漏极,所述mn2的源极接vi-;所述mp1的漏极、所述mp2的漏极、所述mn1的漏极、所述mn2的漏极的公共端接输出信号线tx;

27.所述第一正升压电平转换器的输入端接信号线tx_p_select_logic,所述第二正升压电平转换器和所述第一负升压电平转换器的输入端同时接信号线tx_logic,所述第二负升压电平转换器和所述第三正升压电平转换器的输入端同时接信号线tx_n_select_logic。

28.所述像素驱动电路用于向像素提供驱动脉冲信号,当向该驱动电路提供电源vp+、vp-、 v_logic(v_logic<vp+)时,该电路的工作分以下几种情况:

29.1、当tx_logic输入为vp-,tx_p_select_logic为vp-,tx_n_select_logic为vp-时,

30.第一正升压电平转换器的同相输出为vp-,反相输出为vi+,节点p6为vp-,节点p4为 vi+;

31.第二正升压电平转换器的同相输出为vp-,节点p2为vp-,节点p5为vp-;

32.第一负升压电平转换器的同相输出为vi-,节点n2为vi-,节点n4为vi-;

33.第二负升压电平转换器的同相输出为vi-,节点n3为vi-,节点n5为vi-;

34.第三正升压电平转换器的反向输出为vi+,节点p3为vi+;

35.第一与非门nand1的输出为vi+,mp2管截止;

36.第二与非门nand2的输出为vi+,mp1管截止;

37.与门and的输出为vi-,mn1管截止;

38.或非门nor的输出为v_logic,mn2管导通;

39.最终tx输出为vi-。

40.2、当tx_logic输入为v_logic,tx_p_select_logic为v_logic,tx_n_select_logic为vp

‑ꢀ

时,

41.第一升压电平转换器的同相输出为vi+,反相输出为vp-,节点p6为vi+,节点p4为 vp-;

42.第二正升压电平转换器的同相输出为vi+,节点p2为vi+,节点p5为vi+;

43.第一负升压电平转换器的同相输出为v_logic,节点n2为v_logic,节点n4为v_logic;

44.第二负升压电平转换器的同相输出为vi-,节点n3为vi-,节点n5为vi-;

45.第三正升压电平转换器的反向输出为vi+,节点p3为vi+;

46.第一与非门nand1的输出为vi+,mp2管截止;

47.第二与非门nand2的输出为vp-,mp1管导通;

48.与门and的输出为vi-,mn1管截止;

49.或非门nor的输出为vi-,mn2管截止;

50.最终tx输出为vp+。

51.3、当tx_logic输入为v_logic,tx_p_select_logic为vp-,tx_n_select_logic为vp-时,

52.第一升压电平转换器的同相输出为vp-,反相输出为vi+,节点p6为vp-,节点p4为 vi+;

53.第二正升压电平转换器的同相输出为vi+,节点p2为vi+,节点p5为vi+;

54.第一负升压电平转换器的同相输出为v_logic,节点n2为v_logic,节点n4为v_logic;

55.第二负升压电平转换器的同相输出为vi-,节点n3为vi-,节点n5为vi-;

56.第三正升压电平转换器的反向输出为vi+,节点p3为vi+;

57.与非门nand1的输出为vp-,mp2管导通;

58.与非门nand2的输出为vi+,mp1管截止;

59.与门and的输出为vi-,mn1管截止;

60.或非门nor的输出为vi-,mn2管截止;

61.最终tx输出为vi+。

62.4、当tx_logic输入为v_logic,tx_p_select_logic为vp-,tx_n_select_logic为v_logic 时,

63.第一正升压电平转换器的同相输出为vp-,反相输出为vi+,节点p6为vp-,节点p4为 vi+;

64.第二正升压电平转换器的同相输出为vi+,节点p2为vi+,节点p5为vi+;

65.第一负升压电平转换器的同相输出为v_logic,节点n2为v_logic,节点n4为v_logic;

66.第二负升压电平转换器的同相输出为v_logic,节点n3为v_logic,节点n5为v_logic;

67.第三正升压电平转换器的反向输出为vi-,节点p3为vi-;

68.第一与非门nand1的输出为vi+,mp2管截止;

69.第二与非门-nand2的输出为vi+,mp1管截止;

70.与门and的输出为v_logic,mn1管导通;

71.或非门nor的输出为vi-,mn2管截止;

72.最终tx输出为vp-。

73.上述像素驱动电路的输入与输出的逻辑关系如图3所示,像素结构中当传输晶体管的tx 信号动作时,该像素驱动电路所使用的电源顺序依次为vi-,vp+,vi+,vp-,vi-。只需要保持mp1、mp2、mn1、mn2四个mos管中的其中一个为导通状态,就能够保证tx的输出设定到指定的电压值。

74.本实用新型通过对像素驱动电路进行改进,实现了多电源供电,该像素驱动电路能够用于图像传感器的传输晶体管的tx信号的控制。在保证tx输出到指定电压的同时,也使得电荷泵的面积得到压缩,节约了芯片成本。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1