组合成像阵列和条及像素噪声消除系统的制作方法

组合成像阵列和条及像素噪声消除系统

1.x射线成像阵列可用于响应于入射x射线而生成二维图像或视频。成像条可围绕轴摇摄以生成全景图像。

2.噪声可能累积在成像阵列的像素中。虽然各种技术诸如相关双采样可减少或除去由于从像素到图像的链中的其他部件引起的噪声,但像素本身的噪声可能仍然存在。

附图说明

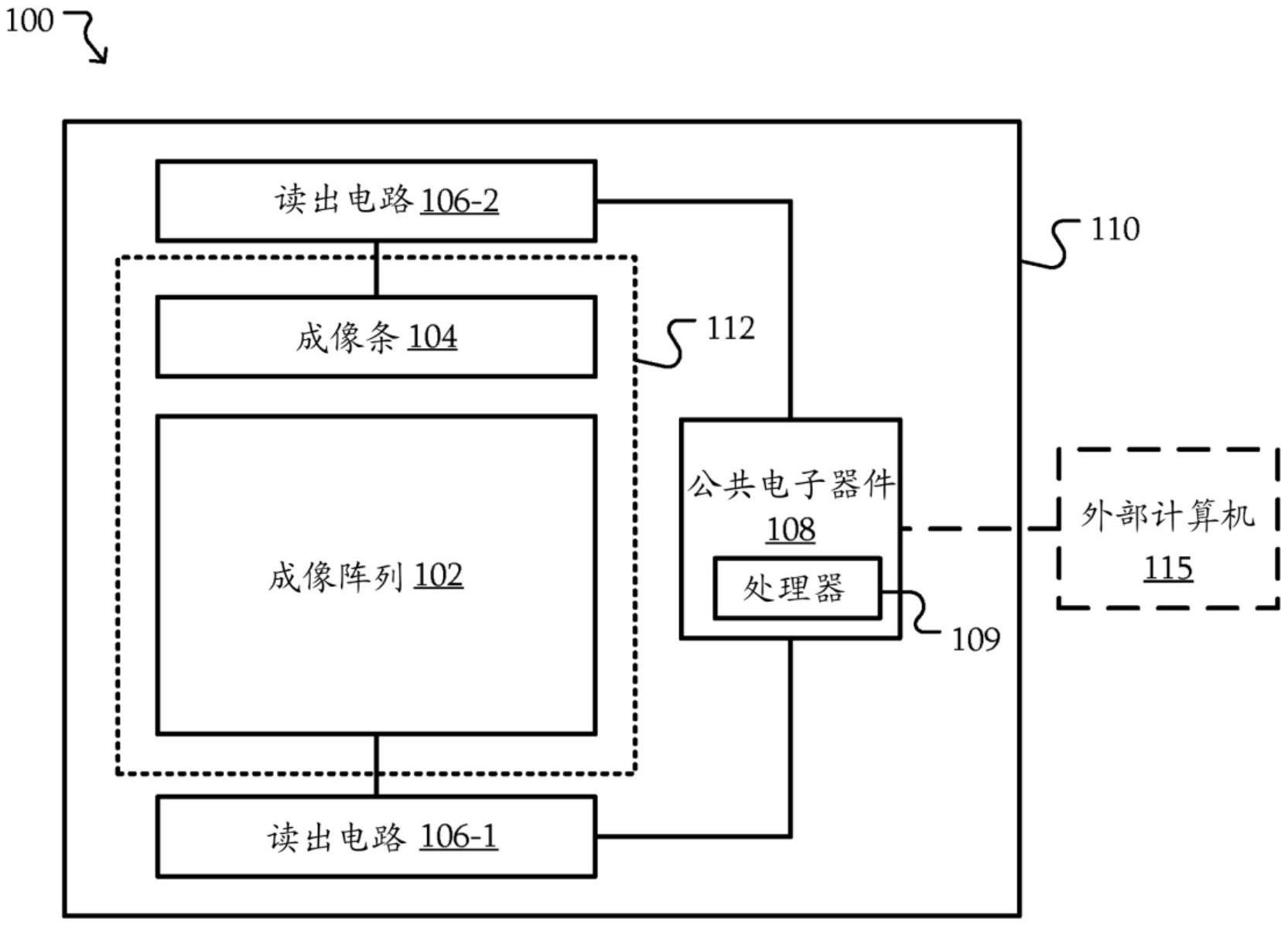

3.图1是根据一些实施方案的包括成像阵列和成像条的成像系统的框图。

4.图2是根据一些实施方案的成像系统的操作的流程图。

5.图3是根据一些实施方案的包括基板的成像系统的框图。

6.图4是根据一些实施方案的具有单独行驱动器的成像系统的框图。

7.图5是根据一些实施方案的成像系统的框图,其中成像条是成像阵列的子集。

8.图6是根据一些实施方案的具有拆分的数据线的成像系统的框图。

9.图7a-图7b是根据一些实施方案的具有可选择性耦接的拆分的数据线的成像系统的框图。

10.图8a-图8b是根据一些实施方案的具有多条数据线的成像系统的框图。

11.图9a是根据一些实施方案的成像系统中的像素和相关联的电子器件的框图。

12.图9b是根据一些实施方案的成像系统中的成像阵列和相关联的电子器件的框图。

13.图10是双采样操作的时序图。

14.图11a是根据一些实施方案的时序图。

15.图11b是根据一些实施方案的成像系统的操作的流程图。

16.图12a是根据一些实施方案的时序图。

17.图12b是根据一些实施方案的成像系统的操作的流程图。

18.图13a是根据一些实施方案的时序图。

19.图13b是根据一些实施方案的成像系统的操作的流程图。

20.图13c是根据一些其他实施方案的时序图。

21.图13d是根据一些其他实施方案的时序图。

22.图14是根据一些实施方案的操作成像系统的技术的流程图。

23.图15是根据一些实施方案的2d x射线成像系统的框图。

具体实施方式

24.一些实施方案与包括成像阵列和成像条的成像系统相关。所述系统可在不同模式下操作,以使用成像阵列获取二维(2d)图像并且使用成像条获取全景图像。

25.用在牙科面板中的成像系统可执行全景成像操作,其中当检测器围绕患者头部旋转时成像条被照射。该成像条可集成为大幅面平板检测器的一部分。通过快速扫描检测器的未使用的行(此操作称为“刷洗”)并且仅打开面板的特定行以进行图像读出来生成图像。此方法受到两个问题的困扰。首先,帧速率受刷洗未使用像素所需时间的限制。其次,在特

定应用诸如医学成像中,成像可能受剂量率限制,并且因此由于更低的可用信号,背景电子噪声具有对图像质量更大的影响。

26.通常,阵列的大小可约为16x 16厘米(cm),其中像素大小大约为100微米(μm)。像素矩阵由一组栅极驱动器寻址,并且由一组正交的读出电荷放大器读出。全尺寸图像可通过顺序开启每行tft并且同时读出阵列的每条数据线上的像素电荷来获取。对于全景模式,行驱动器被控制以快速扫描矩阵的第一部分直到成像条的第一行。行驱动器被控制以在可能是约60-100行的成像条的行的持续时间内减慢到正常读出速率,并且然后快速扫描其余栅极线以刷洗成像器的其余部分。电荷读出通常使用每个像素的栅极接通脉冲由前一行像素的栅极截止脉冲补偿的时序来执行。其他读出方法是可能的,但此途径可增大栅极接通时间以减少滞后并且提供相对平坦的暗图像。由于数据线的相对长的长度,电荷放大器被设定为高功率以便最小化来自数据线电容的噪声。

27.如以下将进一步详细描述的,实施方案包括成像阵列和成像条的不同配置。在一些实施方案中,单独成像阵列和单独成像条可设置在同一外壳中并且共享公共电子器件。在其他实施方案中,成像阵列和成像条可设置在同一基板上。在其他实施方案中,成像条可以是成像阵列的子集,其中在成像阵列内具有各种连接配置。

28.图1是根据一些实施方案的包括成像阵列和成像条的成像系统的框图。成像系统100包括成像阵列102和成像条104。成像阵列102和成像条104设置在同一外壳110中。

29.成像阵列102可以是二维(2d)像素阵列。例如,成像阵列102可包括1600x 1600像素阵列。虽然已经使用在行和列中具有相同数目的像素的成像阵列102作为示例,但是在其他实施方案中,行和列的数目可有所不同。虽然已经使用特定数量的像素作为示例,但是在其他实施方案中,像素数量可有所不同。以像素为单位的较短尺寸与较长尺寸的纵横比大于0.3、0.5、0.75等或者等于1。

30.成像条(或线性成像阵列或线性阵列)104是具有相对低纵横比的像素阵列,其可以是或可以不是2d阵列。例如,成像条104可包括1像素

×

1600像素的阵列。在其他实施方案中,成像条104可包括大约80像素

×

1600像素的阵列。在其他实施方案中,较短尺寸与较长尺寸的纵横比小于约0.05、0.1或0.3。

31.成像阵列102和成像条104可基于相同、相似或不同的技术。例如,成像阵列102可包括基于非晶硅(a-si)的阵列,而成像条可基于更高成本和/或更高分辨率的互补金属氧化物半导体(cmos)、铟镓锌氧化物(igzo)或光子计数技术,诸如碲化镉(cdte)、碲锌镉(cdznte或czt)、硒光电检测器等。在一些实施方案中,成像阵列102和成像条104中的一者或两者可基于igzo。

32.在一些实施方案中,成像阵列102和成像条104中的一者或两者可与一个或多个闪烁体相关联。一个或多个闪烁体可包含多种材料,其被配置来将x射线光子转换成可由对应成像阵列102或成像条104检测的光子。例如,闪烁体可包含碘化铯(csi)、钨酸镉(cdwo4)、聚乙烯甲苯(pvt)等。闪烁体的其他示例包括硫氧化钆(gd2o2s;gos;gadox)、掺有铽的硫氧化钆(gd2o2s:tb)等。在一些实施方案中,成像阵列102和成像条中的一者或两者可不包括闪烁体,但可包括包含cdte、cdznte或czt、硒等的直接转换材料。

33.成像阵列102和成像条104的像素可相同、相似或不同。像素的大小、布局、间距、内部部件、内部电连接等中的一者或多者可相同或不同。例如,成像阵列102可包括50微米(μ

m)像素以获得更好的单次拍摄准确性,而成像条104可具有100μm像素以获得更好的信噪比和/或更快的速度。在另一示例中,成像阵列102和成像条104中的一者可具有1t像素而另一者具有4t像素。虽然已经使用像素之间的差异的特定示例作为示例,但是在其他实施方案中,像素可具有其他差异。

34.成像系统100包括耦接到成像阵列102的读出电路106-1。读出电路106-1可包括用于成像阵列102的列的一个或多个放大器(例如,电荷放大器)。在一些实施方案中,读出电路106-1可包括用于成像阵列102的每个列的电荷放大器。如以下将进一步详细描述的,列的每个像素可耦接到数据线,所述数据线耦接到读出电路106-1的电荷放大器中的一个的输入端。

35.成像系统100包括耦接到成像条104的读出电路106-2。读出电路106-2可包括用于成像条104的列的一个或多个电荷放大器。在一些实施方案中,读出电路106-2可包括用于成像阵列102的每个列的电荷放大器。如以下将进一步详细描述的,列的每个像素可耦接到数据线,所述数据线耦接到读出电路106-2的电荷放大器中的一个的输入端。

36.读出电路106-1可不同于读出电路106-2。例如,将成像阵列102的像素耦接到读出电路106-1的数据线可能比将成像条104的像素耦接到读出电路106-2的数据线更长(例如,由于较大数量的像素行)。因此,由于相关联的数据线的更低电容,读出电路106-2可具有不同配置、可不同地操作等。尽管数据线的长度已被用作读出电路106-2可有所不同的原因的示例,但是读出电路106-2可能出于其他理由而不同。

37.成像系统100包括耦接到第一读出电路106-1和第二读出电路106-2的公共电子器件108。公共电子器件108被配置来响应于第一读出电路106-1和第二读出电路106-2中的至少一者而生成图像数据。在一些操作中,公共电子器件108基于来自读出电路106-1的数据生成图像数据。在其他操作中,公共电子器件108被配置来基于来自读出电路106-2的数据生成图像数据。在其他操作中,公共电子器件108被配置来基于来自读出电路106-1的数据和来自读出电路106-2的数据生成图像数据。

38.公共电子器件108可包括在成像阵列102与成像条104之间以及读出电路106-1和106-2之间共享的多种不同电路。例如,公共电子器件108可包括电源,所述电源被配置来生成用于成像阵列102和成像条104以及读出电路106-1和106-2的电力。公共电子器件108可包括处理器109,其被配置来控制本文所述的各种操作。这种处理器109可以是通用处理器、数字信号处理器(dsp)、专用集成电路、微控制器、可编程逻辑装置、分立电路、此类装置的组合等。处理器109可包括内部部分,诸如寄存器、高速缓冲存储器、处理核心等,并且还可包括外部接口,诸如地址和数据总线接口、中断接口等。尽管在公共电子器件108中仅示出了一个处理器109,但是可存在多个处理器109。此外,其他接口装置诸如逻辑芯片组、集线器、存储器控制器、通信接口等可以是系统公共电子器件108的一部分,以将处理器109连接到内部和外部部件诸如成像阵列102和成像条104、读出电路106-1和106-2以及外部计算机115。

39.外部计算机115是可耦接(例如,经由有线、光学或无线连接)到成像系统100以从公共电子器件108接收图像数据的装置的示例。公共电子器件108可被配置来接收来自外部计算机115的命令,并且响应于所述命令,与外部计算机115交换数据,等等。外部计算机115可采用多种形式,诸如台式计算机、服务器、工作站、平板计算机、移动装置、用户接口终端

等。

40.在一些实施方案中,所述成像阵列102和所述成像条104是分开的。成像阵列102和成像条104可设置在各自附接到外壳110的单独基板上。成像阵列102和成像条104可设置成使得入射辐射可进入公共窗口或开口112并且由成像阵列102或成像条104检测到。

41.在一些实施方案中,成像条104可具有导致比成像阵列102噪声更低、帧速率更高、分辨率更高等的配置。因此,成像阵列102和成像条104可供不同应用使用。由于成像阵列102和成像条104设置在同一外壳110中,用户可针对不同应用使用单个成像系统100,或者用户可在各种成像系统中使用单个外壳110中的检测器。

42.在一些实施方案中,成像阵列102和成像条104可不同时操作。结果,公共电子器件108一次可专门用于成像阵列102和成像条104中的一者的操作。对于成像阵列102和成像条104中的每一者,公共电子器件108的操作可有所不同。例如,公共电子器件108可以比与成像阵列102相关联的行驱动器更快的速率来驱动成像条104的行驱动器。

43.图2是根据一些实施方案的成像系统的操作的流程图。参考图1和图2,并且使用成像系统100作为示例,在一些实施方案中,在200中使用读出电路106-1从成像阵列102读取第一数据。例如,与成像阵列102相关联的行驱动器可被顺序地激活以使用读出电路106-1逐行地从成像阵列102读出数据。公共电子器件108可被配置来控制行驱动器和读出电路106-1以读出期望数据。

44.在202中,使用读出电路106-2从成像条104读取第二数据。例如,与成像条104相关联的行驱动器可被顺序地激活以使用读出电路106-2逐行地从成像条104读出数据。公共电子器件108还可被配置来控制行驱动器和读出电路106-2以读出期望数据。

45.在204和206中,来自成像阵列102和成像条104的数据在公共电子器件108中分别被处理以生成不同的图像数据集。在204和206中的公共电子器件108中的处理可相同、相似或不同。例如,与处理来自成像阵列102的数据相比,可以生成导致噪声降低的图像数据的方式处理来自成像条104的数据。在其他示例中,来自成像阵列102的数据可用于生成视频流,而来自成像条104的数据可用于生成全景图像。204和206中的处理可同时执行、并行执行、顺序执行等。

46.虽然已经使用特定操作次序作为图2中的示例,但是在一些实施方案中,次序可有所不同。例如,可在202之前执行204。在另一个示例中,可在206之后执行200和204。

47.图3是根据一些实施方案的包括基板的成像系统的框图。成像系统300可类似于图1的成像系统100并且包括相同或相似的部件。为了清楚起见,省略了一些部件,但其可能存在。如上所述,在一些实施方案中,成像阵列102和成像条104可以是分开的并且形成在不同的基板上。在一些实施方案中,成像系统300包括基板114。基板114可以是由诸如玻璃、塑料或聚合物、陶瓷、有机或无机半导体等形成的单一基板。成像阵列102和成像条104可形成在基板114中或基板上。例如,成像阵列102和成像条104可以是附接到基板114的单独的集成电路管芯。在其他实施方案中,成像阵列102和成像条104可形成在同一集成电路管芯的不同部分中,诸如在半导体基板的不同部分中。

48.在一些实施方案中,成像阵列102和成像条104仍然可以是单独电子装置,即使成像阵列102和成像条104在同一半导体基板上彼此紧邻。也就是说,除通过基板的寄生连接和/或通过读出电路106-1和106-2以及公共电子器件108的连接之外,成像阵列102和成像

条104可彼此不具有电连接。

49.在一些实施方案中,读出电路106-1和106-2可形成在不同于基板114的基板上。然而,在其他实施方案中,读出电路106-1和106-2中的一者或两者可形成在基板114上。

50.图4是根据一些实施方案的具有单独行驱动器的成像系统的框图。成像系统400可类似于上文所述的成像系统100和300。然而,成像阵列102耦接到行驱动器416b,而成像条104耦接到行驱动器416a。在一些实施方案中,行驱动器416a和416b是分开的电路,而在其他实施方案中,行驱动器416a和416b是与对应成像条104或成像阵列102或两者相同的集成电路的一部分。行驱动器416a和416b可耦接到公共电子器件108并由其控制。

51.行驱动器416a被配置来被顺序激活以逐行读出成像条104。行驱动器416b被配置来被顺序激活以逐行读出成像阵列102。与在控制行驱动器416b时相比,公共电子器件108可被配置来在控制行驱动器416a时改变信号、时序等。

52.图5是根据一些实施方案的成像系统的框图,其中成像条是成像阵列的子集。成像系统500可类似于上文所述的成像系统100、300和400。然而,成像条104是成像阵列102的子集。在一些实施方案中,成像条104可设置在成像阵列102的边缘上。例如,成像阵列102可具有1600像素

×

1600像素的大小。成像条可包括阵列的大小为1600像素

×

80像素的顶部80行像素。虽然已经使用成像条104的特定大小作为示例,但是在维持上述纵横比的同时,所述大小可有所不同。

53.在一些实施方案中,成像阵列102可耦接到行驱动器516。可共享耦接到成像阵列102的成像条104部分的行驱动器516。当成像条104用于生成图像时,可使用相关联的行选择线516a。当成像阵列102用于生成图像时,可使用所有的行选择线516a和516b。

54.在一些实施方案中,成像条104的像素可与成像阵列102的其余部分的像素一样并且与之相同地形成。例如,成像条104的像素可具有相同的大小、形状、间距等。通常,间距是指像素的长度或宽度以及像素之间的间隔。结果,当使用成像阵列102生成图像时,由于成像条104与成像阵列102的其余部分之间的不连续性,可能不出现伪影。

55.在一些实施方案中,当读取图像阵列102时,行驱动器516被配置来逐渐激活跨成像阵列102的行选择线516a和516b。

56.图6是根据一些实施方案的具有拆分的数据线的成像系统的框图。成像系统600可类似于如上所述的成像系统500等。成像系统600包括拆分的数据线618。数据线618被拆分成两组,数据线618a和数据线618b。数据线618a耦接到成像阵列102的成像条104部分并且耦接到读出电路106-2。数据线618b耦接到成像阵列102的其余部分并且耦接到读出电路106-1。

57.数据线618a与618b之间的拆分位置可在多个位置中。在一些实施方案中,拆分是列长度的大约30%,其中数据线618a耦接到列中30%的像素而数据线618b耦接到列中70%的像素。虽然使用30%作为示例,但是在其他实施方案中,位置可有所不同,诸如在1%、5%、10%、20%等处拆分。在其他实施方案中,拆分可在距边缘的特定数量的像素诸如大约80个像素或更少处,但是仍小于成像阵列102的列中的像素数量的30%。在一些实施方案中,可定位拆分使得只有成像条104的像素耦接到数据线618a,而成像条104之外的像素耦接到数据线618b。在其他实施方案中,成像条104之外的一些像素耦接到数据线618a,但是耦接到数据线618a的列的像素总数可能小于约30%。

58.拆分在小于约30%处向成像条104提供了益处。在一些实施方案中,由于数据线618a比数据线618b短,噪声可能更小。在一些实施方案中,更低噪声可能导致伪影出现在使用成像阵列102生成的图像中;然而,如下文将进一步详细描述的,当整个成像阵列102用于生成图像时,附加噪声或等效物可能被添加到由成像条104生成的数据。在一些实施方案中,下游处理可有所不同。例如,与成像阵列102的其余部分相比,可执行不同的暗级匹配操作。

59.在一些实施方案中,噪声降低的量和/或信噪比的增大可以是约10%、20%、40%、50%或更多。例如,更短数据线618a导致更低数据线电容和电阻,这可降低电子读出噪声。在特定示例中,电荷放大器可具有约200个电子(e-)的最小噪声,所述电子噪声随着数据线电容的增大而线性增大。噪声斜率由施加到电荷放大器的功率以及相关联的样本和保持电路的带宽设定控制。此外,数据线的电阻产生与数据线电容相乘的热噪声或约翰逊噪声。此约翰逊噪声随着长度而增大,但是对于更短数据线诸如耦接到成像条104的数据线618a来说可忽略不计。所得噪声可能接近于电荷放大器的最小噪声组合像素的ktc噪声。此噪声(估计为400e-)可能比未拆分数据线的相同大小阵列的噪声(大约700e-)低约40%。术语ktc噪声是指由温度(t)和电容(c)乘以玻尔兹曼常数(k)生成的噪声,诸如热噪声乘以数据线电容和玻尔兹曼常数。玻尔兹曼常数(k)是将粒子的平均相对动能与粒子的热力学温度联系起来的比例因子。

60.更短长度还可增大读出速度。例如,在成像条104的像素的读取操作期间可读取更少的行。不需要刷洗成像阵列102的其余部分以读取成像条104的像素。使用成像条104的80行像素作为示例,控制逻辑103可继续每80门控时钟将令牌(即,沿着行驱动器616传播以激活行的信号)传递到行驱动器616中以激活行选择信号616a。这些令牌可通过其余行驱动器616并且使用行选择信号616b刷洗成像阵列102的其余部分而不干扰成像条104的读出。这可增大成像条104的读出速度。例如,假设刷洗像素的速率为每行约1微秒(μs),则刷洗1600行成像阵列102的在80行成像条104之外的成像阵列(约1520行)所需的时间约为1.52毫秒(ms)。假设读出成像条104的每一行约16μs,则80行成像条104需要1.28ms来读出。总时间约为2.8ms,从而得到357fps的最大帧速率。在专用成像条104的情况下,读出时间仅为1.28ms,从而得到约780fps的帧速率。在预定帧数诸如19帧的读出(24ms)中,可刷洗阵列中的其余像素。

61.在一些实施方案中,读出电路106-1和106-2可以是相同的和/或以相同方式操作,而在其他实施方案中,读出电路106-1和106-2可有所不同和/或以不同方式操作。例如,读出电路106-1和106-2可以是一样的。在其他实施方案中,读出电路106-1和106-2是一样的但不同地操作,诸如具有不同的增益、电流、电容等。在其他实施方案中,读出电路106-1和106-2可有所不同,其中读出电路106-2被优化以用于更短数据线618a。

62.参考图2和图6,在一些实施方案中,在200中,从成像阵列102读取第一数据包括通过数据线618b从成像阵列102读取第一数据。在202中,从成像条104读取第二数据包括使用不同于数据线618b的数据线618a从成像条104读取第二数据。

63.图7a-图7b是根据一些实施方案的具有可选择性耦接的拆分的数据线的成像系统的框图。参考图7a,成像系统700a可类似于上文描述的成像系统600。然而,系统700a包括耦接到成像条104的数据线718a、耦接到成像阵列102的其余部分的数据线718b。数据线718a

和718b是分开的但可由开关722选择性地耦接。每个开关722可选择性地将数据线718a中的一条耦接到对应数据线718b。

64.在一些实施方案中,开关722可包括耦接数据线718a和718b的一个或多个晶体管。开关722可由控制逻辑103控制,使得当成像条104被读取时,开关722断开。结果,来自数据线718a的更低电容被单独提供给读出电路106-2。然而,当读取成像阵列102时,数据线718a和718b可耦接在一起以用作单数据线。可通过读出电路106-1,经由耦接数据线718a和718b读取来自成像阵列102的数据。

65.参考图7b,成像系统700b可类似于成像系统700a。然而,与成像阵列102相关联的数据线可包括数据线718a、718c和718d。在一些实施方案中,数据线718c与718d之间的拆分可在沿着成像阵列102的距离的50%处。例如,像素行的50%可在数据线718c与718d之间的拆分的一侧并且像素行的50%可在拆分的另一侧。

66.响应于控制逻辑103,数据线718a和718c可由开关722选择性地耦接。在一些实施方案中,可通过使用开关722将数据线718a和718c解耦并且通过数据线718a使用读出电路106-2来读取而读取成像条104。当读取成像阵列102时,数据线718a和718c可由开关722耦接并且通过数据线718a和718c的组合使用读出电路106-2来读取。可使用读出电路106-1通过数据线718d读取成像阵列102的其余部分。数据线718a和718c的耦接可发生在小于像素行的50%处,或者数据线718a可覆盖小于整个成像阵列102的30%。

67.因此,在各种实施方案中,整个成像阵列102的数据线的一部分可从与成像条104相关联的数据线718a解耦。所述部分可以是成像条104之外的其余部分的子集,或者是如在成像系统700a和700b中的整个其余部分。

68.参考图2、图7a和图7b,在一些实施方案中,在200中,从成像阵列102读取第一数据包括在从成像阵列102读取第一数据时将第一数据线718a或718c电耦接到第二数据线718b。在202中,从成像条104读取第二数据包括在从成像条104读取第二数据时将第一数据线718a或718c从第二数据线718b电解耦。

69.图8a-图8b是根据一些实施方案的具有多条数据线的成像系统的框图。成像系统800a可类似于上文所述的成像系统500和600。然而,成像系统800a包括数据线818a和818e。数据线818a耦接到成像条104的像素。数据线818e耦接到包括成像条104的像素的整个成像阵列102的像素。因此,至少两条数据线818a和818e耦接到成像条104的每个像素。因此,当读取成像条104时使用数据线818a,而当读取成像阵列102时使用数据线818e。

70.参考图8b,在一些实施方案中,成像系统800b可类似于成像系统800a。在一些实施方案中,用于成像阵列102的数据线可包括在沿着成像阵列102的中途拆分的拆分数据线818d和818f。读出电路106-2可包括用于数据线818a和818f的单独输入。读出电路106-1可耦接到数据线818d。因此,当读取成像条104时使用数据线818a,而当读取成像阵列102时使用数据线818d和818f。

71.如上所述,在各种实施方案中,存在于从成像条104读取的数据中的噪声量可能小于存在于从成像阵列102的其余部分读取的数据中的噪声量。例如,用于从成像条104读取数据的数据线可比用于从成像阵列102读取数据的数据线短。这些数据线可具有更小的电容并贡献更少的噪声。在一些应用中,可能期望降低噪声。例如,当读取成像条104时出现的降低噪声可允许对所得图像中的相同信噪比使用较低的剂量、对于相同的剂量使用较高的

信号、在这两者的各个因素之间进行不同的权衡等。

72.如果来自成像条104的数据与来自成像阵列102的数据组合,即使每一者的像素具有相同的特性,也可能由于不同的噪声水平而出现伪影。为了对此进行补偿,读出电路106-2可以增大从成像条104读取的噪声量的方式操作。例如,内置测试电容器、外部电容器或其他电容器可选择性地耦接到读出电路106-2的输入端,可降低一个或多个放大器的功率,和/或可增大读出电路106-2的部件诸如放大器和/或样本和保持电路的带宽。这些操作可增加电子噪声并且可被调节以匹配成像条104与成像阵列102的其余部分之间的总体噪声。例如,典型的20μs线路时间可能使用40千赫(khz)低通滤波器以用于噪声降低。对于在具有数十皮法(pf)数量级的电容的数据线上的大多数图像读出,在读出电路106-1被设定为高功率低噪声条件的情况下,电子噪声约为600-800

e-。为了使成像条104达到此水平的噪声,可使用低功率正常噪声操作模式,将具有与内置在读出电路106-2中的数据线的电容相似的电容的测试电容器耦接到数据线,和/或将带宽增大到105khz。此操作在成像条104条中给出大约600-800e-的类似的总体噪声。尽管上面已经描述了添加噪声、模拟噪声、均衡噪声等技术的特定示例,但是在其他实施方案中,可执行其他操作以减少或除去图像中由于成像条104的更低噪声而导致的伪影。

73.在一些实施方案中,上述成像系统400、600、700a、700b、800a、800b等可在可动态管理功率的模式下操作。例如,在操作中,控制逻辑103可被配置来控制读出电路106-1或106-2的放大器在较高功率模式下操作,以减少读取整个成像阵列102时的噪声。然而,当读取成像条104时,读出电路106-2的放大器可在更低功率模式下操作。虽然更低功率的操作模式可能增大相对噪声量和/或降低信噪比(snr),但功耗更低。此外,读出电路106-1的放大器可被关断、进入具有显著更低功耗的睡眠模式等。当可读取整个成像阵列102时,可将读出电路106-1和106-2置于较高功率模式以减少噪声的影响。在这些操作模式之间动态切换可降低成像系统500、600、700a、700b、800a、800b等的功耗、降低温度和/或改善可靠性。

74.在一些实施方案中,可降低图像中像素ktc噪声的影响。结果,可使用更低剂量来实现期望分辨率,可增大帧速率,等等。

75.图9a是根据一些实施方案的成像系统中的像素和相关联的电子器件的框图。图9b是根据一些实施方案的成像系统中的成像阵列和相关联的电子器件的框图。参考图9a和图9b,成像系统900包括设置在行和列中的像素902。

76.像素902包括光电检测器904(例如,光电二极管)和晶体管906(即,开关)。晶体管906被配置来响应于行选择信号(rss)选择性地将光电检测器904耦接到数据线908。多个像素902可耦接到列中的单条数据线908。

77.数据线908耦接到放大器910。在一些实施方案中,放大器910是包括重置晶体管(或重置开关)910a和电荷存储装置910b诸如电容器的积分放大器。重置晶体管910a被配置来响应于重置信号“重置”而重置放大器910。放大器910的输出端可响应于采样信号“采样”,通过选择晶体管911选择性地耦接到模数转换器(adc)912。数字化信号可由现场可编程门阵列(fpga)914处理、存储在存储器916中和/或由处理器918或其他下游系统进一步处理。

78.控制逻辑903可耦接到上述各种部件。例如,控制逻辑903可耦接到行驱动器901。控制逻辑可被配置来控制行驱动器901以生成用于像素902的行的行选择信号rss。控制逻

辑903可被配置来配置和控制adc 912、fpga 914、处理器918等的操作。控制逻辑903可包括通用处理器、数字信号处理器(dsp)、专用集成电路、微控制器、可编程逻辑装置、分立电路、此类装置的组合等。控制逻辑903可包括内部部分,诸如寄存器、高速缓冲存储器、处理核心等,并且还可包括外部接口,诸如地址和数据总线接口、中断接口等。另外,诸如逻辑芯片组、集线器、存储器控制器、通信接口等的其他接口装置可以是成像系统900的一部分,以将控制逻辑903连接到内部和外部部件。

79.虽然控制逻辑903被示为与fpga 914、处理器918等分开,但是控制逻辑903可与此类部件集成。例如,本文所述的操作的控制和/或执行可跨fpga 914、处理器918、此类部件的组合等分布。

80.图10是双采样操作的时序图。参考图9a、图9b和图10,系统900可根据图10的时序图来操作。例如,晶体管910a可响应于重置信号“重置”上的脉冲而被启用以重置放大器910。在此操作期间,晶体管(或开关)906随着行选择信号rss被禁用而被禁用。在行选择信号rss被禁用的同时,采样信号“采样”被激活以对放大器910的输出端处的重置值进行采样作为r1。在获取值r1之后,采样信号“采样”被去激活。在去激活采样信号“采样”之后,行选择信号rss被启用,从而启用晶体管906。结果,来自光电检测器904的电荷在放大器910中累积。采样信号“采样”被启用以在放大器910的输出端处对值s1进行采样。

81.等式1和2示出了采样值r1和s1的分量。v

重置

是采样的重置电压,其包括由放大器910贡献的噪声。v

信号,像素

是来自像素902的期望信号。v

ktc

(n-1)是像素902的先前读数遗留下来的像素ktc噪声。v

数据线

噪声是由于数据线908引起的噪声。

82.r1=v

重置

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(1)

83.s1=v

重置

+v

信号,像素-v

ktc

(n-1)+v

数据线噪声

ꢀꢀꢀꢀꢀꢀꢀꢀ

(2)

84.等式3是r1与s1之间的差值,v

p1

(n)。结果包括期望信号v

信号,像素

以及像素ktc噪声v

ktc

(n-1)和数据线噪声v

数据线

。

[0085]vp1

(n)=s

1-r1=v

信号,像素-v

ktc

(n-1)+v

数据线噪声

ꢀꢀꢀꢀ

(3)

[0086]

等式3的运算可以多种方式执行,诸如通过模拟相关双采样(acds)、数字相关双采样(dcds)或将减去信号r1和s1的其他过程。

[0087]

固定模式噪声源可能是由像素到像素或放大器到放大器的变化引起的。固定模式噪声可能不因帧而异。然而,像素ktc噪声由像素半导体开关中的电阻生成并存储在光电检测器904的电容上。像素ktc噪声可能因帧而异。可通过制造控制降低固定模式噪声。像素ktc噪声的降低可通过减小光电检测器904的大小来减小光电检测器904的电容来实现;然而,减小光电检测器904的大小可能会减小其他因素诸如灵敏度、效率等。

[0088]

等式3中的结果仍然具有像素ktc噪声。像素ktc噪声可通过改变像素设计诸如添加附加晶体管来降低。然而,使用一些半导体技术形成的像素,诸如在非晶硅(a-si)中,晶体管的大小可能是禁止的。例如,对于给定像素大小,单个晶体管可能占据像素的很大百分比。添加更多晶体管将显著减少可供光电检测器904使用的像素面积,从而降低系统900的效率。

[0089]

如以下将进一步详细描述的,系统900可不同地操作,从而降低像素ktc噪声。在一些实施方案中,可执行测量,其中可获取像素ktc噪声并将其用于从信号测量中减少或除去像素ktc噪声。尽管像素ktc噪声在帧与帧之间变化,但是在获取信号样本并且通过禁用行

选择信号rss禁用晶体管906之后,像素噪声ktc噪声从放大器910呈现到放大器910的输入端(并且随后输出)。在操作中的此点处,可获取样本以捕获ktc噪声。此样本可被存储并且然后用于减少或除去下一帧中来自像素902的信号的像素ktc噪声。

[0090]

然后可使用所述测量来去除或减少最终值中的像素ktc噪声。因此,来自先前帧的测量被用于减少或消除当前帧中的像素ktc噪声。尽管本文所述的实施方案可适用于使用a-si工艺或其中晶体管的大小与像素大小相比可能相对较大的其他工艺的系统,但是在其他实施方案中,系统可使用其他工艺诸如互补金属氧化物半导体(cmos)工艺形成。

[0091]

图11a是根据一些实施方案的时序图。图11b是根据一些实施方案的成像系统的操作的流程图。参考图9a、图9b、图11a和图11b,在1100中,在开关处于断开状态时,使用读出电路来获取通过开关耦接到数据线908的像素902的第一值。这里,晶体管906是开关的示例,并且读出电路包括放大器910和至少一些下游部件。此第一值即样本r/s在第n-1帧中获取,同时晶体管906被禁用。在对帧n执行后续操作之前,可发生后续处理。

[0092]

在1102中重置读出电路。在这个示例中,重置放大器910。然而,在其他实施方案中,可重置附加部件。重置放大器910可包括通过激活重置信号“重置”来使电荷存储装置910b放电。

[0093]

在1104中,在重置读出电路之后获取像素902的第二值。在这个示例中,在重置放大器910之后获取值r1。

[0094]

在1106,接通开关。这里,行选择信号rss被激活,从而接通晶体管906。结果,来自像素902的电荷可被转移到放大器910。

[0095]

在1108中,在接通开关之后获取像素902的第三值。在这个示例中,在接通晶体管906之后获取值s1。

[0096]

在1110中,将第一值、第二值和第三值组合成像素902的组合值。在这个示例中,将三个值r1、s1和r/s组合成像素920的组合值。如下文将更详细描述的,可以各种方式组合三个值r1、s1和r/s以减少或除去像素ktc噪声。根据将第一值、第二值和第三值组合在一起以减少或除去ktc噪声的特定组合技术,组合在一起的各种值可包括其他值。

[0097]

在一些实施方案中,在1101中,存储基于第一值的存储值。例如,可将基于值r/s的值存储在fpga 914、存储器916、处理器920或另一个下游系统中。存储值基于来自前一帧n-1的值。存储值可与来自当前帧n的值r1和s1组合。因此,1110中的组合可包括通过基于第一值的存储值来组合第一值。在一些实施方案中,可对于每个像素902存储整个帧的r/s值或衍生值。整个帧的值r1和s1,无论是单独还是组合的,都可与存储的r/s值组合。

[0098]

本文所述的操作涉及在读出过程期间获取附加样本。因为此附加样本耗费附加时间,因此增大了读出时间。然而,可降低噪声,从而潜在地增大信噪比,从而允许更低剂量等。因此,在一些实施方案中,读出时间的增大可换取噪声的减少、更低剂量等。

[0099]

在一些实施方案中,当数据线908电容更小时,降噪益处具有更大影响。当组合所述值时,来自数据线908电容的噪声增大了2的平方根。在一些实施方案中,可在捕获来自像素902的信号期间实施合并(binning)。例如,在2x2合并模式中,组合四个像素902以作为单个像素操作。相对于读出单个像素902,数据线908噪声可能加倍,同时像素ktc噪声原本将是四倍。然而,可减少或除去像素ktc噪声。因此,本文所述的操作在执行合并时可能具有更大的影响。

[0100]

图12a是根据一些实施方案的时序图。图12b是根据一些实施方案的成像系统的操作的流程图。参考图9a、图9b、图12a和图12b,所述操作可类似于包括操作1100、1101(任选地)、1102、1104、1106和1108的图11a和图11b的操作,其类似于以上关于图11b描述的那些操作。在1200中,在获取像素902的第一值之前,重置读出电路。例如,可用重置信号“重置”上的脉冲重置放大器910。此操作可以是与在1102中稍后执行的重置相同或相似的操作。

[0101]

在1202中,当开关处于接通状态时获取像素902的第四值。例如,在重置放大器910之后,在开关906处于接通状态时获取值r2。

[0102]

所述操作继续类似于图11b的操作,其中r3是值r/s。在1204中,将值s1、r1、r2和r3组合在一起以生成像素902的组合值。等式4-6示出了类似于上述等式1-3的采样值r1、s1和v

p1

(n)的分量。v

重置1

是在重置放大器910之后采样的重置电压。

[0103]

r1=v

重置1

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(4)

[0104]

s1=v

重置1

+v

信号,像素-v

ktc

(n-1)+v

数据线噪声1

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(5)

[0105]vp1

(n)=s

1-r1=v

信号,像素-v

ktc

(n-1)+v

数据线噪声1

ꢀꢀꢀꢀꢀꢀꢀ

(6)

[0106]

等式7是采样值r2。值r2在放大器910被重置之后并且开关906处于接通状态时被采样。等式8是采样值r3。值r3在开关906转换到断开状态之后被采样。等式9是r2与r3之间的差值。等式10是v

像素

(n),即v

p1

(n)和v

p2

(n-1)的总和。虽然添加了不同的数据线噪声v

数据线噪声1

和v

数据线噪声2

,但是所得组合实际上是二的平方根乘以通用数据线噪声电平。

[0107]

r2=v

重置2

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(7)

[0108]

r3=v

重置2

+v

ktc

(n-1)+v

数据线噪声2

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(8)

[0109]vp2

(n-1)=r

3-r2=v

ktc

(n-1)+v

数据线噪声2

ꢀꢀꢀꢀꢀꢀꢀꢀ

(9)

[0110][0111]

在前一帧n-1上采样的值r2和r3具有来自所述前一帧的像素ktc噪声。为了解释来自前一帧n-1的r2和r3的值,将解释帧n中的操作。重置放大器910并且在重置之后进行采样。这生成值r1。像素902通过接通开关906而接通,并且对信号进行另一个采样,从而生成值s1。然后如前所述减去两个样本r1和s1。

[0112]

在执行对信号进行采样以生成值s1之后,晶体管906不断开,而是保持在接通状态。由重置信号“重置”上的脉冲重置放大器910并且获取样本,即值r2。此样本包括放大器910的重置值。当开关906响应于去激活行选择信号rss而断开时,像素ktc噪声被转移并被放大器910积分。具体地,当断开晶体管906时,一些电荷保留在像素902中并且相等且相反的量被放大器910积分。此积分量与下次读取像素902时将出现的像素ktc噪声相反。

[0113]

再次对放大器910的输出进行采样,从而获取值r3,其包括重置值、像素ktc噪声和数据线908噪声。像素ktc噪声是下一次在下一帧中读取像素902时将出现的像素ktc噪声。因此,当在帧n-1中执行此操作时,值r2和r3或这些值的组合可用于下一帧n。

[0114]

在一些实施方案中,可通过使用相关双采样技术来执行等式6和9的操作。例如,无论是模拟还是数字,相关双采样技术可用于生成r2与r3之间的差值,如等式9所示。类似地,在不同的时间,相关双采样技术可用于生成r1与s1之间的差值,如等式6所示。因此,不同的值可组合成两个不同的相关值。这些相关值可如等式10进行组合。因此,在一些实施方案中,可使用现有硬件通过控制诸如重置信号“重置”和行选择信号rss的各种信号来生成值v

p1

(n)和v

p2

(n-1)。不是执行两次相关双采样操作以最终产生两帧图像数据,而是可执行两

次相关双采样操作以最终产生一帧图像数据。

[0115]

参考图9a、图9b和图12a-图12c,图12b的1204可用1208和后续处理替换。在操作1200至1108之后,在1208中,可将第一值和第四值组合成第一相关值。如上所述,值r2和r3可通过相关双采样技术组合。在1210,可将第二值和第三值组合成第二相关值。如上所述,r1和s1可通过相关双采样技术组合。在1212中,将第一相关值和第二相关值组合成像素902的组合值。所述组合可由多种装置诸如fpga 914、处理器918、控制逻辑903、外部计算机913等执行。

[0116]

图13a是根据一些实施方案的时序图。图13b是根据一些实施方案的成像系统的操作的流程图。参考图9a、图9b、图13a和图13b,在一些实施方案中,生成值r1和s1的信号可与上述那些信号类似。然而,基于先前帧的第三值s2与那些值组合。

[0117]

在1302至1308中,所述操作与图11b的1102至1108相同或相似以生成值r1和s1。这些操作是针对前一帧n-1的。在1300中,与1100类似,在不重置对应读出电路的情况下获取用于后续帧的像素902的第一值。例如,当获取到第一值时,开关处于断开状态。因此,在1306之后,行选择信号rss被禁用,断开晶体管906。然后获取值s2作为第一值以用于后续帧n。在帧n的稍后时间,重复操作1302至1308,从而生成用于帧n的值r1和s1。执行类似于操作1110的操作1310,以组合第一值、第二值和第三值。可执行操作1300,从而生成用于帧n的值s2以供在帧n+1中使用。

[0118]

在特定示例中,对于先前帧n-1,等式11和12给出r1(n-1)和s1(n-1)的分量。

[0119]

r1(n-1)=v

重置1

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(11)

[0120]s1(n-1)

=v

重置1

+v

信号,像素-v

ktc

(n-2)+v

数据线噪声1

ꢀꢀꢀꢀꢀ

(12)

[0121]

然而,在获取用于前一帧n-1的值s1之后获取值s2。所述值s2是在断开晶体管906之后并且在没有重置放大器910的情况下获取的。因此,所得值s2包括由等式13表示并在等式14中简化的先前积分值s1加上像素ktc噪声两者。

[0122]

s2(n-1)=v

重置1

+v

信号,像素-v

ktc

(n-2)+v

ktc

(n-1)+v

数据线噪声2

[0123]

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(13)

[0124]

s2(n-1)=s1(n-1)+v

ktc

(n-1)+v

数据线噪声2

ꢀꢀꢀꢀꢀꢀꢀꢀ

(14)从s2减去s1得到前一帧n-1的像素ktc噪声,如等式15所示。

[0125]bp,ktc

(n-1)=s

2-s1=v

ktc

(n-1)+v

数据线噪声2

ꢀꢀꢀꢀꢀꢀꢀꢀ

(15)对于当前帧n,获取值r1和s1并将其组合,如等式16-18所示。得自等式15的像素ktc噪声是先前生成的。它可被添加到v

p1

(n)以去除来自前一帧n-1的像素ktc噪声。

[0126]

r1(n)=v

重置1

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(16)

[0127]

s1(n)=v

重置1

+v

信号,像素-v

ktc

(n-1)+v

数据线噪声1

ꢀꢀꢀꢀ

(17)

[0128]vp1

(n)=s

1-r1=v

信号,像素-v

ktc

(n-1)+v

数据线噪声1

ꢀꢀꢀꢀꢀꢀꢀ

(18)

[0129][0130]

由于只获取了三个值,因此一帧数据的处理速度可有所提高超过上述获取了四个值的数据的处理速度。结果,可增大帧速率。然而,可使用不同于现有相关双采样硬件的硬件。也就是说,虽然可使用相关双采样技术组合s1和r1以生成表示差值的单个值,但值s2可使用不同电子器件以生成所述值。此外,采样电路可被配置来分别对值r1、s1和s2进行采样并且将它们组合在fpga914、处理器918、外部计算机913或其他下游系统中。

[0131]

图13c是根据一些实施方案的时序图。参考图9a、图9b、图13b和图13c,在一些实施方案中,可使用数字相关双采样技术。响应于信号中的asic移位(asin),要采样的信号可移位到采样电容器或其他样本存储装置。所述操作可类似于图13a的操作。在一些实施方案中,采样电容器可以是一组采样电容器,其中电容器的使用在采样操作之间轮换。采样信号“采用”可如上所述被激活以对值r1、s1和s2进行采样。然而,采样电容器组可包括偶数个采样电容器。可激活第四采样信号1350或附加采样信号以确保相关联的像素902看到相同的采样电容器。虽然使用一个采样信号1350作为示例,但可根据需要存在更多采样信号。采样值可能无关紧要。因此,asin可能不被激活。因此,在一些实施方案中,移入信号以进行采样的次数可小于激活采样信号“采样”的次数。

[0132]

图13d是根据一些实施方案的时序图。参考图9a、图9b、图13b和图13d,在一些实施方案中,可使用模拟相关双采样来执行操作。响应于钳位信号“钳位”,重置值r1可存储在采样电容器上。所述采样电容器可耦接到模拟减法装置诸如差分放大器,其执行与模拟相关双采样相关联的模拟减法。

[0133]

在一些实施方案中,两个测量被数字化为中间值。如上所述,在等式12和13中,s1和s2均包括重置值r1。不是直接减去s1和s2,而是在数字化样本之前通过模拟相关双采样操作从s1和s2中减去r1。因此,可数字化地执行的后续操作可由等式20-22表示,其中s'1是在差分放大器中从s1减去r1之后的数字化值,并且s'2类似地是从s2减去r1之后的数字化值。可如上所述使用等式22中的所得v

p,ktc

。

[0134]s′1(n-1)=s

1-r1ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(20)

[0135]s′2(n-1)=s

2-r1ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(21)

[0136]vp,ktc

(n-1)=s

′

2-s

′1=v

ktc

(n-1)

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(22)

[0137]

因此,在各种实施方案中,1300、1304、1308的获取操作和1310的组合操作可在硬件和数字信号处理的多种组合中执行。

[0138]

图14是根据一些实施方案的操作成像系统的技术的流程图。在1400中,选择操作模式。在第一操作模式中,可执行类似于如上所述的图11b、图12b、图12c、图13b等中描述的操作的操作。结果,可获取更低噪声的数据。然而,一些应用可能需要更高的帧速率。因此,由于更低噪声操作中的附加样本而导致的附加延迟可能是不期望的。因此,可选择第二操作模式,其中在1402中,执行相关双采样操作。在此模式下,不执行获取第一值。因此,系统的操作可从更低噪声模式切换到较高帧速率模式。

[0139]

在特定示例中,当成像系统用于荧光检查或可能需要更高帧速率的其他应用时,可选择第二模式。一旦识别出感兴趣区域,就可选择第一模式以生成具有更低噪声、更低剂量等的图像。在另一个示例中,在执行合并的情况下,诸如2x2、3x3、4x4或更大合并,像素ktc噪声可能优于数据线相关噪声。成像系统可在第一模式下操作以减少像素ktc噪声。

[0140]

在一些实施方案中,数据帧可能不可用和/或可能被丢弃。例如,帧n-1的第一帧数据可用于生成第一值和其他值。所述帧数据不能用于生成图像或视频信号帧。相反,所述数据可用于初始化上述处理,使得每个后续帧可具有来自先前帧的可用值以执行上述更低噪声处理。

[0141]

在一些实施方案中,上述用于减少或除去像素ktc噪声的操作可应用于上述成像条104。具体地,成像条104可具有将成像条104耦接到读出电路106-2的相对更短数据线。公

共电子器件108和读出电路106-2可如上所述进行配置以减少ktc噪声。

[0142]

在一些实施方案中,可根据是否读取成像条104来切换关于图14描述的操作模式。例如,如果成像条104是成像阵列102的一部分,并且正在读取整个成像阵列102,则可不执行上述用于减少像素ktc噪声的操作。因为每条数据线存在两次测量,所以来自数据线的背景噪声也被测量两次。对于具有更长数据线的成像阵列102,此数据线噪声可比像素ktc噪声占优势。

[0143]

图15是根据一些实施方案的2d x射线成像系统的框图。2d x射线成像系统1500包括x射线源1502和检测器1510。检测器1510可包括如上所述的成像系统100、200、400、500、600、700a、700b、800a、800b、900等。x射线源1502相对于检测器1510而设置,使得可生成穿过标本1522并且由检测器1510检测的x射线1520。在一些实施方案中,检测器1510是医学成像系统的一部分。在其他实施方案中,2d x射线成像系统1500可包括便携式车辆扫描系统作为货物扫描系统的部分。

[0144]

一些实施方案包括一种系统,其包括:外壳110;成像阵列102,所述成像阵列设置在所述外壳110内;成像条104,所述成像条设置在所述外壳110内;第一读出电路106-1,所述第一读出电路耦接到所述成像阵列102;第二读出电路106-2,所述第二读出电路耦接到所述成像条104;和公共电子器件108,所述公共电子器件耦接到所述第一读出电路106-1和所述第二读出电路106-2并且被配置来响应于所述第一读出电路106-1和所述第二读出电路106-2中的至少一者而生成图像数据。

[0145]

在一些实施方案中,所述成像阵列102和所述成像条104是分开的。

[0146]

在一些实施方案中,所述成像阵列102和所述成像条104是分开的并且形成在同一基板114上。

[0147]

在一些实施方案中,所述成像阵列102的像素的大小、布局、分辨率和内部部件中的至少一者不同于所述成像条104的像素的大小、布局、分辨率和内部部件中的对应至少一者。

[0148]

在一些实施方案中,所述成像条104是所述成像阵列102的子集。

[0149]

在一些实施方案中,所述成像条104小于所述成像阵列102的30%。

[0150]

在一些实施方案中,所述系统还包括:数据线618、718、818,所述数据线耦接到所述成像阵列102和所述成像条104。

[0151]

在一些实施方案中,所述系统还包括:多个开关722,所述多个开关将所述数据线718分成耦接到所述成像条104的多条第一数据线718b和耦接到所述成像阵列102的在所述成像条104之外的其余部分的多条第二数据线718b。

[0152]

在一些实施方案中,所述系统还包括:多条第一数据线618a,所述多条第一数据线耦接到包括所述成像条104的所述成像阵列102的所述子集;多条第二数据线618b,所述多条第二数据线与所述第一数据线618a分开并且耦接到所述成像条104之外的所述成像阵列102。

[0153]

在一些实施方案中,所述系统还包括:x射线源,所述x射线源被配置来生成x射线束;检测器,所述检测器被设置为接收所述x射线束并且包括所述外壳110、所述成像阵列102、所述成像条104、所述第一读出电路106-1、所述第二读出电路106-2和所述公共电子器件108。

[0154]

一些实施方案包括一种方法,其包括:使用至少第一读出电路106-1从设置在外壳110内的成像阵列102读取第一数据;使用至少第二读出电路106-2从设置在所述外壳110内的成像条104读取第二数据;在公共电子器件108中处理所述第一数据以生成第一图像数据;并且在所述公共电子器件108中处理所述第二数据以生成第二图像数据。

[0155]

在一些实施方案中,所述成像阵列102和所述成像条104是分开的。

[0156]

在一些实施方案中,所述成像阵列102和所述成像条104形成在同一基板114上。

[0157]

在一些实施方案中,所述成像阵列102的像素的像素大小不同于所述成像条104的像素的像素大小。

[0158]

在一些实施方案中,所述成像条104是所述成像阵列102的子集。

[0159]

在一些实施方案中,所述成像条104小于所述成像阵列102的30%。

[0160]

在一些实施方案中,使用至少所述第一读出电路106-1从设置在外壳110内的所述成像阵列102读取所述第一数据包括通过第一数据线618、718、818从所述成像阵列102读取所述第一数据;并且使用至少所述第二读出电路106-2从设置在所述外壳110内的所述成像条104读取所述第二数据包括使用不同于所述第一数据线618、718、818的第二数据线618、718、818从所述成像条104读取所述第二数据。

[0161]

在一些实施方案中,使用至少所述第一读出电路106-1从设置在外壳110内的所述成像阵列102读取所述第一数据包括通过第一数据线618、718、818从所述成像阵列102读取所述第一数据;并且使用至少所述第二读出电路106-2从设置在所述外壳110内的所述成像条104读取所述第二数据包括使用第二数据线618、718、818从所述成像条104读取所述第二数据;并且还包括当从所述成像阵列102读取所述第一数据时将所述第一数据线618、718、818电耦接到所述第二数据线618、718、818。

[0162]

一些实施方案包括一种系统,其包括:用于从设置在外壳内的成像阵列读取第一数据的装置;用于从设置在所述外壳内的成像条读取第二数据的装置;用于在公共电子器件108中处理所述第一数据以生成第一图像数据的装置;以及用于在所述公共电子器件108中处理所述第二数据以生成第二图像数据的装置。

[0163]

所述用于从设置在外壳内的成像阵列读取第一数据的装置的示例包括读出电路106-1和相关联的数据线。

[0164]

所述用于从设置在所述外壳内的成像条读取第二数据的装置的示例包括读出电路106-2和相关联的数据线。

[0165]

所述用于在公共电子器件中处理所述第一数据以生成第一图像数据的装置的示例包括所述公共电子器件108。

[0166]

所述用于在所述公共电子器件中处理所述第二数据以生成第二图像数据的装置的示例包括所述公共电子器件108。

[0167]

在一些实施方案中,所述成像条104是所述成像阵列102的子集。

[0168]

一些实施方案包括一种系统,其包括:多个像素902;多条数据线908,所述多条数据线耦接到所述像素902;多个开关906,所述多个开关将所述像素902耦接到所述数据线908;多个读出电路910-918,所述多个读出电路耦接到所述数据线908;控制逻辑903,所述控制逻辑耦接到所述读出电路910-918,所述控制逻辑903被配置来,针对所述像素902中的一个像素:当对应开关906处于断开状态时获取所述像素902的第一值;重置对应于所述像

素的对应读出电路910-918;在重置所述读出电路之后获取所述像素902的第二值;接通所述对应开关906;在接通所述对应开关906之后获取所述像素902的第三值;并且将所述第一值、所述第二值和所述第三值组合成所述像素902的组合值。

[0169]

在一些实施方案中,所述控制逻辑903还被配置来,针对所述像素902中的一个像素:存储基于所述第一值的所述像素902的存储值;并且将所述第二值、所述第三值和所述存储值组合成所述像素902的所述组合值。

[0170]

在一些实施方案中,所述控制逻辑903还被配置来,针对所述像素902中的一个像素:在获取所述像素的所述第一值之前:重置所述对应读出电路;在所述对应开关906处于接通状态时获取所述像素902的第四值;并且将所述第一值、所述第二值、所述第三值和所述第四值组合成所述像素902的所述组合值。

[0171]

在一些实施方案中,所述控制逻辑903还被配置来,针对所述像素902中的一个像素:将所述第三值减去所述第二值与第一值减去所述第四值相加,以将所述第一值、所述第二值、所述第三值和所述第四值组合成所述像素902的所述组合值。

[0172]

在一些实施方案中,所述控制逻辑903还被配置来,针对像素902中的一个像素:将所述第一值和所述第四值组合成第一相关值;将所述第二值和所述第三值组合成第二相关值;和将所述第一相关值和所述第二相关值组合成所述像素902的所述组合值。

[0173]

在一些实施方案中,所述控制逻辑903还被配置来,针对所述像素902中的一个像素:在不重置所述对应读出电路的情况下获取用于后续帧的所述像素902的第一值。

[0174]

在一些实施方案中,所述控制逻辑903还被配置来,针对所述像素902中的一个像素:从所述第三值减去所述第一值和所述第二值,以将所述第一值、所述第二值和所述第三值组合成所述像素902的所述组合值。

[0175]

在一些实施方案中,所述控制逻辑903还被配置来,针对所述像素902中的一个像素:在以下模式之间切换906:第一操作模式,在所述第一操作模式中,所述第一值、所述第二值和所述第三值被组合成所述像素的所述组合值;以及第二操作模式,在所述第二操作模式中,所述第二值和所述第三值被组合成所述像素902的所述组合值,并且在所述对应开关906处于所述断开状态时不执行获取所述像素902的所述第一值。

[0176]

在一些实施方案中,所述系统还包括:x射线源,所述x射线源被配置来生成x射线束;检测器,所述检测器包括所述像素902并且被设置为接收所述x射线束。

[0177]

一些实施方案包括一种方法,其包括:当开关906处于断开状态时,使用读出电路910-918获取通过所述开关906耦接到数据线的像素902的第一值;重置所述读出电路;在重置所述读出电路之后获取所述像素902的第二值;接通所述开关906;在接通所述开关906之后获取所述像素902的第三值;并且将所述第一值、所述第二值和所述第三值组合成所述像素902的组合值。

[0178]

在一些实施方案中,所述方法还包括:存储基于所述第一值的所述像素902的存储值;并且其中将所述第一值、所述第二值和所述第三值组合成所述像素902的所述组合值包括:将所述第二值、所述第三值和所述存储值组合成所述像素902的所述组合值。

[0179]

在一些实施方案中,所述方法还包括:在获取所述像素的所述第一值之前:重置所述读出电路;并且在所述开关906处于接通状态时获取所述像素902的第四值;并且其中将所述第一值、所述第二值和所述第三值组合成所述像素902的所述组合值包括:将所述第一

值、所述第二值、所述第三值和所述第四值组合成所述像素902的所述组合值。

[0180]

在一些实施方案中,将所述第一值、所述第二值、所述第三值和所述第四值组合成所述像素902的所述组合值包括:将所述第三值减去所述第二值与所述第一值减去所述第四值相加。

[0181]

在一些实施方案中,所述方法还包括:将所述第一值和所述第四值组合成第一相关值;将所述第二值和所述第三值组合成第二相关值;并且将所述第一相关值和所述第二相关值组合成所述像素902的所述组合值。

[0182]

在一些实施方案中,所述方法还包括:在不重置所述对应读出电路的情况下获取用于后续帧的所述像素902的第一值。

[0183]

在一些实施方案中,将所述第一值、所述第二值和所述第三值组合成所述像素902的所述组合值包括:从所述第三值中减去所述第一值和所述第二值。

[0184]

在一些实施方案中,所述方法还包括:在以下模式之间切换:第一操作模式,在所述第一操作模式中,所述第一值、所述第二值和所述第三值被组合成所述像素的所述组合值;以及第二操作模式,在所述第二操作模式中,所述第二值和所述第三值被组合成所述像素902的所述组合值,并且在所述对应开关906处于所述断开状态时不执行获取所述像素902的所述第一值。

[0185]

在一些实施方案中,所述方法还包括:使用x射线源生成x射线束;并且使用被设置为接收所述x射线束的包括所述像素902的检测器来生成图像。

[0186]

一些实施方案包括一种系统,其包括:用于当开关处于断开状态时使用读出电路获取通过所述开关耦接到数据线的像素的第一值的装置;用于重置所述读出电路的装置;用于在重置所述读出电路之后获取所述像素的第二值的装置;用于接通所述开关的装置;用于在接通所述开关之后获取所述像素的第三值的装置;以及用于将所述第一值、所述第二值和所述第三值组合成所述像素的组合值的装置。

[0187]

所述用于当开关处于断开状态时使用读出电路获取通过所述开关耦接到数据线的像素的第一值的装置的示例包括开关906、行驱动器901、数据线908和读出电路910-918。

[0188]

所述用于重置所述读出电路的装置的示例包括开关910a和控制逻辑903。

[0189]

所述用于在重置所述读出电路之后获取所述像素的第二值的装置的示例包括所述开关906、所述行驱动器901、所述数据线908和所述读出电路910-918

[0190]

所述用于接通所述开关的装置的示例包括所述控制逻辑903。

[0191]

所述用于在接通所述开关之后获取所述像素的第三值的装置的示例包括所述开关906、所述行驱动器901、所述数据线908和所述读出电路910-918。

[0192]

所述用于将所述第一值、所述第二值和所述第三值组合成所述像素的组合值的装置的示例包括所述开关906、所述行驱动器901、所述数据线908、所述读出电路910-918和外部计算机913。

[0193]

在一些实施方案中,所述系统还包括:用于在不重置所述对应读出电路的情况下获取用于后续帧的所述像素的第一值的装置。所述用于在不重置所述对应读出电路的情况下获取用于后续帧的所述像素的第一值的装置的示例包括所述开关906、所述行驱动器901、所述数据线908和所述读出电路910-918。

[0194]

尽管上面已经描述了用于执行特定功能的装置的特定示例,但是在其他实施方案

中,可通过本文所述的其他装置来执行特定功能。

[0195]

虽然已经根据特定实施方案描述了结构、装置、方法和系统,但本领域普通技术人员将容易地认识到,对特定实施方案的许多变化是可能的,并且因此,任何变化应被视为在本文所公开的精神和范围内。因此,在不脱离所附权利要求的精神和范围的情况下,本领域普通技术人员可做出许多修改。

[0196]

随附此书面公开的权利要求据此明确并入本书面公开中,其中每项权利要求自身可作为单独的实施方案。本公开包括单独权利要求及其从属权利要求的所有排列。此外,能够从随附的单独权利要求和从属权利要求衍生的附加实施方案也明确并入本书面说明书中。这些附加实施方案是通过用短语“以权利要求[x]开始并且以紧接在所述权利要求之前的权利要求结束的权利要求中的任一个”来替换给定从属权利要求的从属关系来确定的,其中括号内的术语“[x]”被用最近引用的独立权利要求的编号来替换。例如,对于以独立权利要求1开始的第一权利要求集,权利要求4可从属于权利要求1和权利要求3中的任一项,其中这些单独的从属关系产生两个不同的实施方案;权利要求5可从属于权利要求1、权利要求3或权利要求4中的任一项,其中这些单独的从属关系产生三个不同的实施方案;权利要求6可从属于权利要求1、权利要求3、权利要求4或权利要求5中的任一项,其中这些单独的从属关系产生四个不同的实施方案;以此类推。

[0197]

关于特征或要素的术语“第一”的权利要求的叙述并不一定意味着存在第二或附加的这种特征或要素。要求排他性属性或特性的本发明的实施方案限定如下。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1