一种FPGA模组和音频转换设备的制作方法

一种fpga模组和音频转换设备

技术领域

1.本发明涉及时钟同步领域,尤其涉及一种fpga模组和包括该fpga模组的音频转换设备。

背景技术:

2.精确时间同步协议(precision time protocol,ptp),是一种用于在计算机网络中同步时钟的协议,在局域网中实现了亚微秒范围内的时钟精度,使其适用于测量和控制系统。

3.在同一局域网中,从节点通过网络与同一局域网内的主节点保持同步,现有技术中主、从节点内一般通过专用的时钟芯片生成本地时钟信号,设备间运行ptp协议发送sync、delay_req、delay_resq指令来完成从节点的时间校准,达到时钟同步的目的。然而,采用专用时钟芯片极易受限于芯片厂家的供应,而且硬件成本相对较高。另外,主从节点由于时钟频率不同步会导致两者之间的时间差offset发生变化,现有技术在根据ptp协议实现同步校准时,未考虑到ptp报文在设备内部的延时以及因网络环境变化等原因使得网络延时发生抖动,进而影响所获取到的时间差,从而进一步影响时钟频差的获取,导致所实现的时钟同步精准度不够高。

技术实现要素:

4.有鉴于此,因为现有的时钟同步精准度不够高的问题,本发明提供一种fpga模组和包括该fpga模组的音频转换设备,通过fpga内部模块生成硬件时间戳,并获取网络端对端处的时间戳,减少内部延时、网络延时对时间差计算的影响,提高时钟同步精准度。

5.为了解决上述问题,本发明提供一种fpga模组,基于ptp协议实现时钟同步,包括:网络模块、时钟模块和主控模块,所述网络模块根据网络协议接收和发送ptp报文,所述主控模块对所述时钟模块进行同步校准,所述时钟模块包括:时钟校准单元,用于生成并行数据,从所述主控模块接收时钟频差,并根据所述时钟频差调整所生成的并行数据;串行化单元,用于将所述并行数据进行并串转换得到基础时钟信号;计数单元,用于根据所述基础时钟信号生成时间戳;所述网络模块根据所述ptp报文中的消息类型获取报文经离其时的时间戳,所述主控模块根据所述网络模块获取到的时间戳计算时间差和网络延时,再根据预设规则获取所述时钟频差。

6.其中,所述ptp报文包括sync报文、delay_req报文和delay_resq报文,将所述fpga模组应用在主节点和从节点,所述主节点和从节点交互一组ptp报文的时间为一个同步周期,一个同步周期对应一个时间差、网络延时和同步时间点,所述同步时间点为所述同步周期内的一个时间点。

7.进一步,为了减少设备内部延时对网络延时和时间差计算的干扰,对于任意同步

周期,获取对应的时间差和网络延时包括:所述主节点发送sync报文,所述主节点的网络模块获取所述sync报文经离其时的第一时间戳,并将所获取的第一时间戳封装在sync报文中;所述从节点接收所述sync报文,所述从节点的网络模块获取所述sync报文经离其时的第二时间戳;所述从节点的主控模块从所述网络模块接收所述sync报文和第二时间戳,并从所述sync报文中解析所述第一时间戳;所述从节点发送所述delay_req报文,所述从节点的网络模块获取所述delay_req报文经离其时的第三时间戳,并发送给所述从节点的主控模块;所述主节点接收delay_req报文,所述主节点的网络模块获取所述delay_req报文经离其时的第四时间戳;所述主节点发送所述delay_resq报文,所述主节点的网络模块将所述第四时间戳封装在所述delay_resq报文中;所述从节点接收所述delay_resq报文,所述从节点的网络模块接收所述delay_resq报文并发送给所述主控模块,所述主控模块从所述delay_resq报文中解析所述第四时间戳;所述从节点的主控模块根据所述第一时间戳、第二时间戳、第三时间戳和第四时间戳计算所述主节点和从节点之间的时间差和网络延时。

8.更进一步,为了减少网络延时抖动对一同步周期内时间差获取的影响,为使第一时间戳更加逼近于第三时间戳,所述从节点的主控模块对所述主节点发送所述sync报文时间进行预测,控制所述从节点根据预测时间发送所述delay_req报文。

9.其中,所述预设规则为:设定校准周期,所述主控模块在每个校准周期内获取一次时钟频差。

10.作为一种实施方式,为了进一步降低网络延时抖动对时间差的干扰,对于每个校准周期,所述主控模块获取所述时钟频差,包括:在校准周期内设定若干个统计周期,所述统计周期内包括了若干个同步周期;在每个统计周期内将网络延时最小的同步周期所对应的时间差作为所述统计周期内的优选时间差;将各统计周期的优选时间差及其对应的同步时间点进行线性拟合得到所述校准周期内的时钟频差。

11.作为另一种实施方式,对于每个校准周期,所述主控模块获取所述时钟频差,包括:所述校准周期包含若干同步周期;选取任意两个同步周期,根据所选同步周期对应的时间差和同步时间点计算时钟频差。

12.为了便于操作,对于任意同步周期,其对应的同步时间点为其第一时间戳。

13.另外,本发明还公开了一种音频转换设备,所述音频转换设备上述fpga模组。

14.其中,所述音频转换设备还包括模数转换模块和数模转换模块,所述模数转换模块接入模拟音频信号,将模拟音频信号转换为数字音频信号;所述数模转换模块将数字音频信号转换成模拟音频信号,输出模拟音频信号;所述fpga模组还包括编解码模块,所述编

解码模块实现数字音频信号和ip音频流之间的转换,所述ip音频流指能够在网络中传输的数字音频信号;所述fpga模组中的网络模块根据网络协议发送和接收所述ip音频流。

15.与现有技术相比,本发明具有以下优势:本发明的fpga模组利用并行数据经过并串转换产生时钟信号,进而基于ptp协议在获取主、从节点的时间差时尽量减少设备内部时延干扰以及因网络不稳定所带来的干扰,使得所获取的时间差更加接近真实的时间差,从而基于获取到的时间差得到主、从节点之间的时钟频差,实现精准时钟同步;本发明的音频转换设备,采用上述fpga模组实现同一网络中各设备间的同步,保证ip音频流传输的可靠性和稳定性。

附图说明

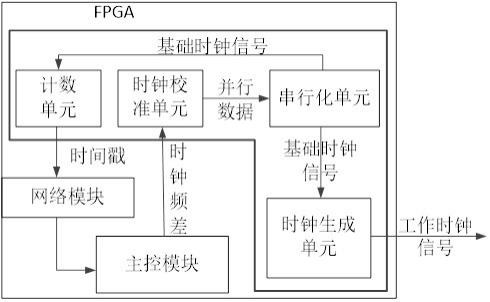

16.图1是本发明中音频转换设备的模块示意图;图2是图1中fpga模组的模块示意图;图3是同一网络中主从节点之间通过ptp协议实现时钟同步的连接示意图;图4是同一网络中主从节点之间通过ptp协议实现时钟同步的流程示意图;图5是对称网络中主从节点之间时间差随时间的变化示意图;图6是非对称网络中主从节点之间时间差随时间的变化示意图。

具体实施方式

17.下面结合实施例对本发明作更进一步的说明。

18.图1中本发明的音频转换设备100包括fpga模组、模数转换模块、数模转换模块,fpga模组包括:网络模块、编解码模块、时钟模块和主控模块;模数转换模块,连接模拟音频输入接口(图未示),接入模拟音频信号,将模拟音频信号转换为数字音频信号;数模转换模块,连接模拟音频输出接口(图未示),将数字音频信号转换为模拟音频信号,输出模拟音频信号;网络模块,连接网络接口(图未示),根据网络协议接收和发送网络数据,以及从时钟模块获取时间戳;编解码模块,实现数字音频信号和ip音频流之间的转换;时钟模块,用于生成时间戳以及数字音频信号在设备内部传输所需的时钟信号,为了便于描述,本发明中将该时钟信号称为工作时钟信号;主控模块,控制fpga模组中各模块工作以及对时钟模块进行同步校准。

19.上述网络协议可以是以太网协议,上述ip音频流指的是能够在网络中传输的数字音频信号,例如满足aes67、ndi或srt等协议的数据流,即音频转换设备100的主要功能为实现 ip音频流和模拟音频信号的相互转换。上述工作时钟信号与设备采用传输协议有关,例如常见的数字音频传输标准i2s(inter-ic sound, integrated interchip sound),其采用的工作时钟信号包括bclk,sclk,mclk和wclk,这些工作时钟信号的频率均是音频采样率的整数倍。

20.在通信网络中应用上述音频转换设备,必然也需要满足网络时钟同步以保证数据传输的可靠性和稳定性。下文将重点介绍上述fpga模组中的时钟模块。

21.作为一种实施方式,本发明中采用精准时钟同步协议(ptp)来实现同一网络中上述音频转换设备之间的时钟同步。如图2所示,本发明中时钟模块包括时钟校准单元、串行化单元、时钟生成单元和计数单元;时钟校准单元生成并行数据,接收时钟频差,并根据时

钟频差调整其输出的并行数据;串行化单元接收并行数据,将并行数据进行并串转换得到基础时钟信号;时钟生成单元根据基础时钟信号生成工作时钟信号;计数单元根据基础时钟信号生成时间戳。

22.时钟校准单元在生成并行数据时,可参考工作时钟的频率,以i2s为例,因其采用的工作时钟信号均为音频采样率的整数倍,故而将基础时钟信号的频率设定为音频采样率的n倍(n为2的幂),则可通过计数分频方式(50%的占空比)得到工作时钟信号,这样产生的工作时钟频率更加稳定,有利于提高音频的总谐波失真和信噪比。

23.上述时钟频差指待同步的主、从节点的时钟频率之间的差值,如同时间戳,可以通过计数比来反映。为了便于统计,可设时钟频差的单位为ppb(part per billion)。作为一种实施方式,本发明中串行化单元可采用serdes(multi-gigabit serializer/deserializer,序列化器/反序列化器)来实现,serdes模块产生的串行数据频率普遍在5ghz以上,则时钟调节时的精度至少能达到0.2ns。

24.假设基础时钟信号为100hz,串行化单元频率为5ghz,则时钟校准单元周期性输出并行数据0x3fffffe000000即可得到上述基础时钟信号,即通过高、低位来调整基础时钟信号的频率。若从节点与主节点之间的频差为+100ppb,则从节点的实际时钟频率为100mhz+100ppb*100mhz=100.00001mhz,则主、从节点的时钟周期差为103*(1/100-1/00.00001) ns,即经过n=0.2/[103*(1/100-1/00.00001)]位后,即大约20万次后,主节点比从节点慢0.2ns,故而调整从节点的并行数据,每 20万个周期增加一个高位,即可实现主、从节点的基础时钟同频。

[0025]

结合图1和图2,网络模块根据网络协议在网络中发送和接收ptp报文,根据ptp消息类型获取ptp报文经离其时的时间戳,将获取到的时间戳发送给主控模块;主控模块根据接收到的时间戳计算时钟频差,并将时钟频差发送给时钟模块中的时钟校准单元。

[0026]

ptp报文包括报头(header)、主体(body)和附加(suffix),报头中的某些字段标记了消息的类型,以ptpv2为例,报头中 messageid 字段标识了消息类型,下文实施例中所涉及到的sync报文、delay_req报文以及delay_resq报文均对应不同的消息类型标识。

[0027]

作为一种实施例,如图3所示,位于同一局域网内的主节点200和从节点300均包括图2所示的时钟模块,主节点200与从节点300的模块结构可以与图1中的音频转换设备100的模块结构相同,也可包括其他功能模块,图3仅示出了与实现时钟同步相关的模块。根据ptp协议规定,通过网络互连的多个设备可通过announce报文来选择时间精准度高的设备作为主节点,本实施例仅重点介绍主节点确定后的时钟同步过程。结合图4所示,主、从节点通过网络模块周期性地发送和接收ptp报文组,在每个同步周期内,包括以下步骤:主节点200发送sync报文,当sync报文经离主节点200的网络模块时,主节点200的网络模块从其计数单元获取第一时间戳t1,并将所获取的第一时间戳t1封装在sync报文中;从节点300接收sync报文,当sync报文到达从节点300的网络模块时,从节点300的网络模块从其计数单元获取第二时间戳t2,并将sync报文和第二时间戳t2发送给从节点300的主控模块;从节点300的主控模块接收sync报文并进行解析获取其中的第一时间戳t1以及第二时间戳t2;

从节点300发送delay_req报文,当delay_req报文经离从节点300的网络模块时,从节点300网络模块从其计数单元获取第三时间戳t3,并将第三时间戳t3发送给从节点的主控模块;主节点200接收 delay_req报文,当delay_req报文到达主节点200的网络模块时,主节点200的网络模块从其计数单元获取第四时间戳t4,并将第四时间戳t4封装在delay_resq报文中,主节点200发送delay_resq报文;从节点300接收delay_resq报文,从节点300的主控模块对delay_resq报文进行解析获取其中的第四时间戳t4。至此,从节点300的主控模块已知第一时间戳t1、第二时间戳t2、第三时间戳t3和第四时间戳t4。

[0028]

上述实施例中仅介绍了在请求应答机制下采用单步模式来实现时钟同步方式的步骤,对于双步模式,本发明中的fpga模组同样适用。

[0029]

对于每个同步周期,从节点300的主控模块根据第一时间戳t1、第二时间戳t2、第三时间戳t3和第四时间戳t4便可获取到该网络中主、从节点之间的单向网络延时为delay_1、delay_2和同步时间点t1、t3对应的时间差offset_1、offset_2,计算公式如下:t1 + delay_1 + offset_1=t2;t3+ delay_2

ꢀ–ꢀ

offset_2=t4。

[0030]

结合上述公式,对于对称网络,即网络延时delay稳定(delay_1= delay_2)的情况下,结合图5所示,其中主、从节点时钟随时间t的变化率分别为主、从节点的时钟频率,从节点300的时钟频率高于主节点200的时钟频率,则时间差offset会越来越大,并线性增大;同理,若从节点300的时钟频率低于主节点200的时钟频率,则时间差offset会越来越小,并线性减小;若从节点300的时钟频率与主节点200的时钟频率一致,则任意时刻的offset保持不变(图未示),即从节点300和主节点200相对同步。本实施例通过时钟频差对从节点300进行时钟频率校准,使得主节点200与从节点300之间的时钟频率趋于一致。现有技术中,在每个同步周期,进一步假设各同步时间点的时间差稳定,即offset_1=offset_2,此时,便可得到:delay_1= delay_2 =[ (t2

ꢀ–ꢀ

t1)+ (t4

ꢀ–ꢀ

t3)]/2;offset_1= offset_2= [(t2

ꢀ–

t1)

ꢀ–ꢀ

(t4

ꢀ–ꢀ

t3)]/2。

[0031]

显然通过这种方式获得的时间差是不够精准的,基于上述分析,为了更准确地通过时间差offset来获取时钟频差从而提高时钟校准精度,应尽可能使主节点200发送sync报文和从节点300发送delay_req报文的时间保持一致,本实施例做了进一步改进,对于每个同步周期,从节点300在发送delay_req报文之前,从节点300的主控模块先对主节点发送sync报文时间进行预测(ptp报文组发送周期以及报文发送间隔是固定的),再根据预测时间发送delay_req报文。

[0032]

下文将具体介绍本实施例如何根据时间差offset获取时钟频差。

[0033]

结合上文和图5,以从节点300的时钟频率高于主节点200的时钟频率为例,每个同步周期均对应一个同步时间点,如图中t1、t2、t3、t4

…

,tn,各同步周期(亦即各同步时间点)所对应的时间差offset分别为offset1、offset2、offset3、offset4…

,offsetn,为了便于操作,t1、t2、t3、t4

…

,tn可以是每个同步周期的第一时间戳t1,显然,图5中时钟频差是固定的,不会随着时间的推移而发生变化。在任意校准周期(包含若干个同步周期),从节点

300的主控模块获取任意两个同步周期所对应的时钟频差,即根据所选同步周期对应的时间差和同步时间点计算时钟频差,再发送给其时钟校准单元,时钟校准单元根据时钟频差改变输出的并行数据,相应的串行化单元所产生的基础时钟信号则发生变化,从而实现主、从节点之间的频率同步。

[0034]

例如,假设校准周期为图5中为两个同步周期间隔,则其至少包含了两个同步周期,设某一校准周期内包含了同步周期一(对应同步时间点t1)和同步周期二(对应同步时间点t2),则该校准周期的时钟频差为(offset2–ꢀ

offset1)/(t2

ꢀ–

t1)。

[0035]

网络在收发包时,难免会遇到因为交换机拥塞、网络不对称性等原因使得网络延时delay发生抖动,导致实际获取的时间差offset如图6所示,因此为了进一步提高时钟校准的精度,本实施例对时钟频差的获取方式做了进一步改进,具体为:在每个校准周期内设定若干个统计周期,任意统计周期内包括了若干个同步周期,获取该统计周期内网络延时delay最小的同步周期所对应的时间差offset作为该统计周期内的优选时间差;将校准周期内,根据各统计周期获取到的优选时间差及其对应的同步时间点进行线性拟合得到该校准周期内的时钟频差。

[0036]

例如,每个同步周期均对应一个同步时间点,如图6中t1、t2、t3,t4

…

,tn,各同步周期(亦即各同步时间点)所对应的时间差offset分别为offset1、offset2、offset3、offset4…

,offsetn,结合上文,每个同步周期都有相应的网络延时delay和时间差offset,假设一个校准周期内包含两个统计周期,每个统计周期内包含两个同步周期,设时间段(0,t4)为一个校准周期,则其中包含两个统计周期,分别为时间段(0,t2)和时间段(t2,t4),设在第一个统计周期内同步时间点t2对应的网络时延delay2最小,则在该统计周期内的优选时间差为offset2;在第二统计周期内若同步时间点t3对应的网络时延delay3最小,则在该统计周期内的优选时间差为offset3,则优选时间差为offset3,显然经过线性拟合方式获得该校准周期内的时钟频差为(offset3–ꢀ

offset2)/(t3

ꢀ–

t2)。

[0037]

通过设置统计周期获取最小网络时延对应节点的时间差作为优选时间差,可以极大的减少网络异常所带来的offset抖动,提高时钟同步校准的精度。

[0038]

以上详细描述了本发明的优选实施方式,但是,本发明并不限于上述实施方式中的具体细节,在本发明的技术构思范围内,可以对本发明的技术方案进行多种等同变换,这些等同变换均属于本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1