一种基于FPGA实现的高效网络流表设计方法与流程

本发明涉及网络数据处理,具体涉及一种基于fpga实现的高效网络流表设计方法。

背景技术:

1、在网络数据处理当中,流表占据着极为重要的位置,广泛应用于网络交换系统、终端处理系统以及网络运维系统。流表当中存储了所有流的处置方法,对于当前流,必须及时地查找其对应的处置方法,这就需要对流表进行快速地访问,关键在于根据当前流的特征,获取其在流表中的存储内容。对于同一流的认定在于相同的流特征,之后基于此流特征,计算该流在流表当中的位置索引,通过索引获取当前流的处置方法,按照处置方法进行后续的相关处理。

2、网络五元组(源ip地址、目的ip地址、传输层协议类型、源端口、目的端口)是比较公认的流特征,可以唯一的标识一个流。但是五元组的数据位宽过大,仅在ipv4协议下就有104位,无法直接作为索引使用,需要对其进行一定的压缩变换。哈希(hash)流表作为一种广泛地使用的流表,依赖于哈希散列的操作简单、计算复杂度小、处理延时低等优点,在索引快速计算方面有着优越的性能。但哈希流表天然存在着哈希冲突的问题,即不同的五元组通过哈希变换,可能得到相同的索引。为了提供可靠的流表服务,发生的哈希冲突需要较高的资源能耗和成本代价去处理。

3、因此,如何减小哈希冲突的概率,以及如何处理出现的哈希冲突,是哈希方式的流表在设计当中必须要解决的问题。

技术实现思路

1、本发明的目的在于提供一种基于fpga实现的高效网络流表设计方法,该方法基于高效哈希表与cam表相结合,以及以大容量哈希表结合小容量cam表的方式,构造以哈希表为主存储器、cam表为辅存储器的联合存储结构体,来减小和处理哈希冲突。

2、为解决上述问题,本发明所采用的技术方案如下:

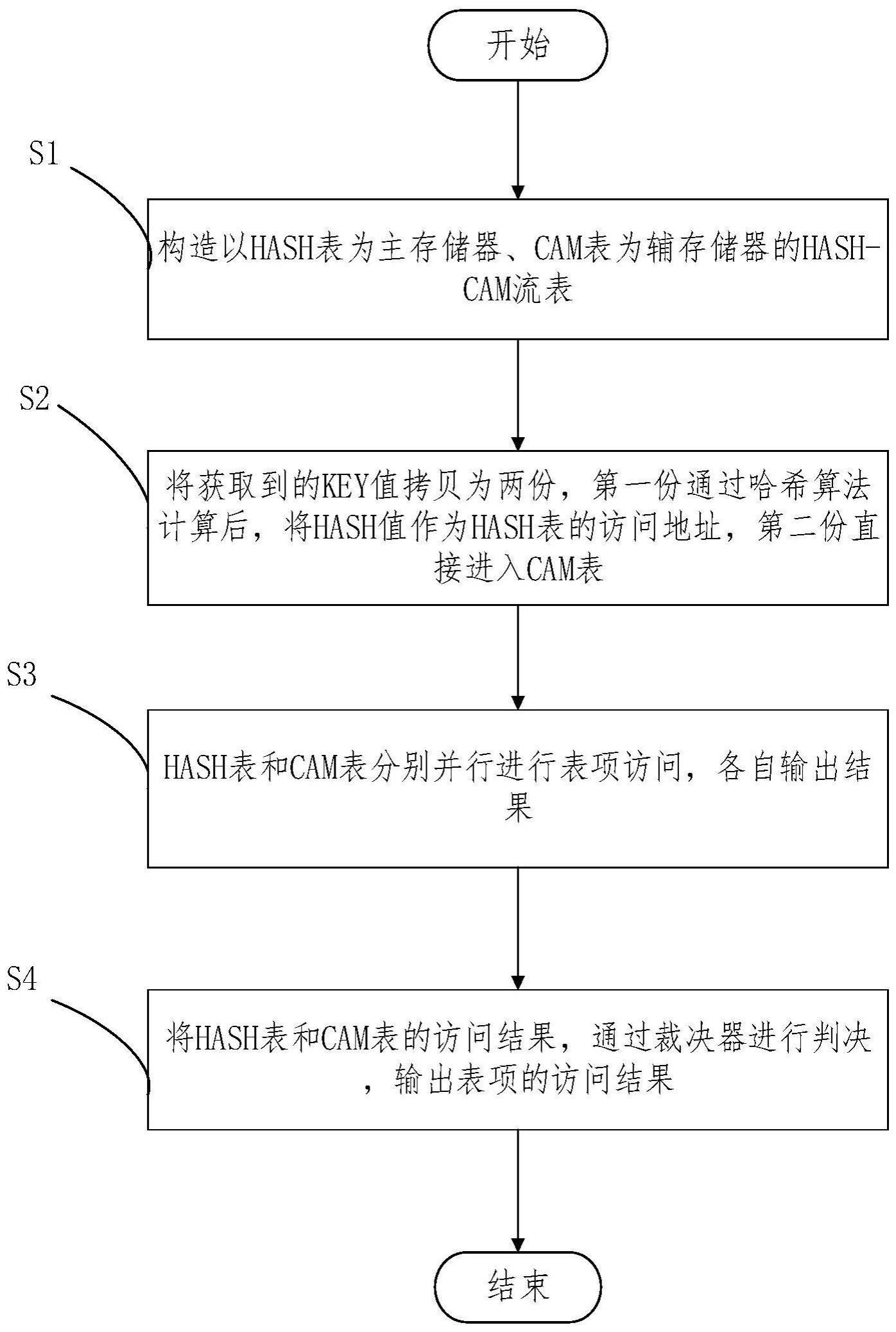

3、一种基于fpga实现的高效网络流表设计方法,该方法包括以下步骤:构造以hash表为主存储器、cam表为辅存储器的hash-cam流表;将获取到的key值拷贝为两份,第一份通过哈希算法计算后,将hash值作为hash表的访问地址,第二份直接进入cam表;hash表和cam表分别并行进行表项访问,各自输出结果;将hash表和cam表的访问结果,通过裁决器进行判决,输出表项的访问结果;其中,对hash-cam流表的访问,包括查找、新建修改、删除等功能。

4、根据本发明提供的一种基于fpga实现的高效网络流表设计方法,在构造hash-cam流表时,还执行:在表项的新建时,优先使用hash表进行存储,若发生冲突,则使用cam表进行存储;在表项的查询时,并行对hash表和cam表进行同时匹配,若二者其一命中,则为匹配命中。

5、根据本发明提供的一种基于fpga实现的高效网络流表设计方法,hash-cam流表当中的存储数据包括三类字段:key值、value值、en值;key值为五元组,用于流的匹配;value值为处置方法,用于匹配后流的处理,为用户自定义项;en值为当前表项的使用状态,用于流的有效验证和快速删除。

6、根据本发明提供的一种基于fpga实现的高效网络流表设计方法,hash表以fpga内部的块状ram为基本存储实体,按照hash方法进行内容匹配;对于ram访问地址的生成,需要将key值进行hash运算,运算结果作为ram的访问地址;对于hash变换函数的选择,使用随机性好、便于fpga实现的crc序列。

7、根据本发明提供的一种基于fpga实现的高效网络流表设计方法,对于m>1的多个表项,hash表的比较流程包括:将key值附加于crc序列,得出crc值;根据hash表的深度n,从crc值选取相同的位宽,作为hash表的读取地址;对于读出的表项,并行进行宽度m个比较操作;输出比较结果,在m个结果中,若有1个命中,即为hash表命中;若m个未命中且至少1个空闲,即为hash表空闲;若m个冲突,即为hash表冲突。

8、根据本发明提供的一种基于fpga实现的高效网络流表设计方法,cam表以寄存器逻辑单元为基本存储实体,按照所有空间遍历的方法进行内容匹配;在使用时,需要对cam覆盖的所有寄存器逻辑单元同时进行比较,对各个单元的比较结果进行仲裁,最终输出cam的匹配结果。

9、根据本发明提供的一种基于fpga实现的高效网络流表设计方法,cam寄存器堆积的多级实现包括:在输入侧,将待匹配key值按照1-k的方式逐级扇出,使其到达每一个寄存器;在存储侧,对寄存器中存储的表项进行内容比较和空闲检测;在输出侧,将比较结果按照k-1的方式逐级汇聚,最终输出匹配结果、匹配的位置和空闲的位置。

10、根据本发明提供的一种基于fpga实现的高效网络流表设计方法,hash-cam流表查找操作的处理包括:其输入为匹配key值,输出为命中结果和命中位置的value值;其中,hash表的读操作和cam表的匹配操作可以并行执行,key值经过hash计算后输出为hash值,作为hash表的读地址,读取其中存储的key值、value值和en值,若en值有效且存储的key值与匹配的key值相同,则查找结果为hash表命中;若hash表未命中,需要查看cam表的命中结果;若cam表命中,则查找结果为命中,若cam表未命中,则查找结果为未命中。

11、根据本发明提供的一种基于fpga实现的高效网络流表设计方法,hash-cam流表新建修改操作的处理包括:其输入为匹配key值和value值;其中,新建修改操作前需要执行查找操作,若查找结果为未命中时,执行的实际效果为新建,若查找结果为命中,说明该表项已经存在,执行的实际效果为修改;在新建过程中,若hash表的en值无效,则写入表项内容至hash表,若hash表的en值有效,则说明发送冲突,此位置已经占有,则将表项内容写入cam表当中。

12、根据本发明提供的一种基于fpga实现的高效网络流表设计方法,hash-cam流表删除操作的处理包括:其输入为匹配key值;其中,删除操作前需要执行查找操作,查找结果为未命中时,说明该表项不存在,无需删除,若查找结果为命中,则将表项的en值失效。

13、由此可见,相对于现有技术,本发明提供的hash-cam流表可以减小和处理哈希冲突,基于fpga实现的hash-cam流表,在提供可靠的流表功能基础上,充分发挥fpga并行计算的优势,有着实时性能高、资源能耗低、访问时延小的优点,可在fpga系统时钟下进行流水工作,比较轻松的实现千万量级pps(packets per second,每秒吞吐包个数)的流表操作。

14、下面结合附图和具体实施方式对本发明作进一步详细说明。

技术特征:

1.一种基于fpga实现的高效网络流表设计方法,其特征在于,该方法包括以下步骤:

2.根据权利要求1所述的方法,其特征在于,在构造hash-cam流表时,还执行:

3.根据权利要求1所述的方法,其特征在于:

4.根据权利要求1所述的方法,其特征在于:

5.根据权利要求4所述的方法,其特征在于:

6.根据权利要求1所述的方法,其特征在于:

7.根据权利要求6所述的方法,其特征在于:

8.根据权利要求1至7任一项所述的方法,其特征在于:

9.根据权利要求1至7任一项所述的方法,其特征在于:

10.根据权利要求1至7任一项所述的方法,其特征在于:

技术总结

本发明提供一种基于FPGA实现的高效网络流表设计方法,其包括构造以HASH表为主存储器、CAM表为辅存储器的HASH‑CAM流表;将获取到的KEY值拷贝为两份,第一份通过哈希算法计算后,将HASH值作为HASH表的访问地址,第二份直接进入CAM表;HASH表和CAM表分别并行进行表项访问,各自输出结果;将HASH表和CAM表的访问结果,通过裁决器进行判决,输出表项的访问结果;其中,对HASH‑CAM流表的访问,包括查找、新建修改、删除等功能。本发明基于高效哈希表与CAM表相结合,以大容量哈希表结合小容量CAM表的方法,构造以哈希表为主存储器、CAM表为辅存储器的联合存储结构体,来减小和处理哈希冲突。

技术研发人员:张建军,耿世磊,杨少波,余军,范建超,赵洋

受保护的技术使用者:珠海高凌信息科技股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!