基于高阶LDPC长码的通信方法及系统与流程

本发明是关于信道编码,特别是关于一种基于高阶ldpc长码的通信方法及系统。

背景技术:

1、1962年,r.g.gallager创造性地提出了ldpc(low density parity check,低密度奇偶校验)码的概念,但由于当时硬件条件的制约而被长期搁置。受turbo码[2]的启发,1995年,d.j.c.mackay深入发掘了ldpc码的价值,构造长码并采用迭代译码,从而获得极高的编码增益。尽管在纠错能力上有turbo码和polar码的强力竞争,但是ldpc码是在高可靠和低延时两方面兼顾最好的信道编码方案。ldpc码已经应用于ieee 802.16e、dvb-s2以及5g等标准中,是当前最流行的信道编码。

2、高阶信道编码具有更强的抗随机噪声和突发干扰的能力,且在级联高阶调制与空时编码时能够减少软信息的损失,是未来信道编码的重要备选方案,其中高阶ldpc码已经成功应用于“北斗”卫星导航系统中。然而,高阶ldpc码的研究主要集中在抗随机噪声的中短码,其纠错能力不足以与二阶ldpc长码相比,且其抗突发干扰的潜力依然有待开发。目前需要高阶ldpc长码有效的构造及编译码方法,特别是抗突发干扰能力强的码字结构。

3、“北斗”卫星导航系统采用的信道编码是典型的中等长度高阶ldpc码,由随机设计的整个二阶校验基矩阵,对其非零元素随机替换为高阶有限域非零元素,从而得到行满秩的高阶ldpc码。由于码长相对较短,编码增益仍有较大的提升空间。

4、ieee 802.16e与5g nr均是二阶ldpc长码,由半随机设计产生校验基矩阵,进而由扩展因子产生扩展校验矩阵。标准中的ldpc码需要覆盖多种码长与码率,对于特定的码长、码率均非最优。在工程中,往往需要特定的码长、码率,标准难以完全匹配,导致资源浪费。由编码理论的基本常识可知,如采用高阶编码,可以进一步提高编码增益。

5、当前高阶ldpc长码的基本思想是,依据现有标准中的二阶校验基矩阵,对其固定结构部分保持不变,对其随机设计部分的非零元素随机替换为高阶有限域非零元素,扩展因子适当减小,以使整个码长保持不变。这种设计也存在码长、码率种类有限的问题,且固定结构部分在高阶编码时也有随机化的可能。

6、此外,在译码时,现有的高阶译码算法均为逐符号运算,难以直接实现编码阶数的并行和扩展因子级的并行。

7、公开于该背景技术部分的信息仅仅旨在增加对本发明的总体背景的理解,而不应当被视为承认或以任何形式暗示该信息构成已为本领域一般技术人员所公知的现有技术。

技术实现思路

1、本发明的目的在于提供一种基于高阶ldpc长码的通信方法及系统,其提高了编码增益、抗删除增益,并减少了与高阶调制或空时编码级联时提取软信息的损失。

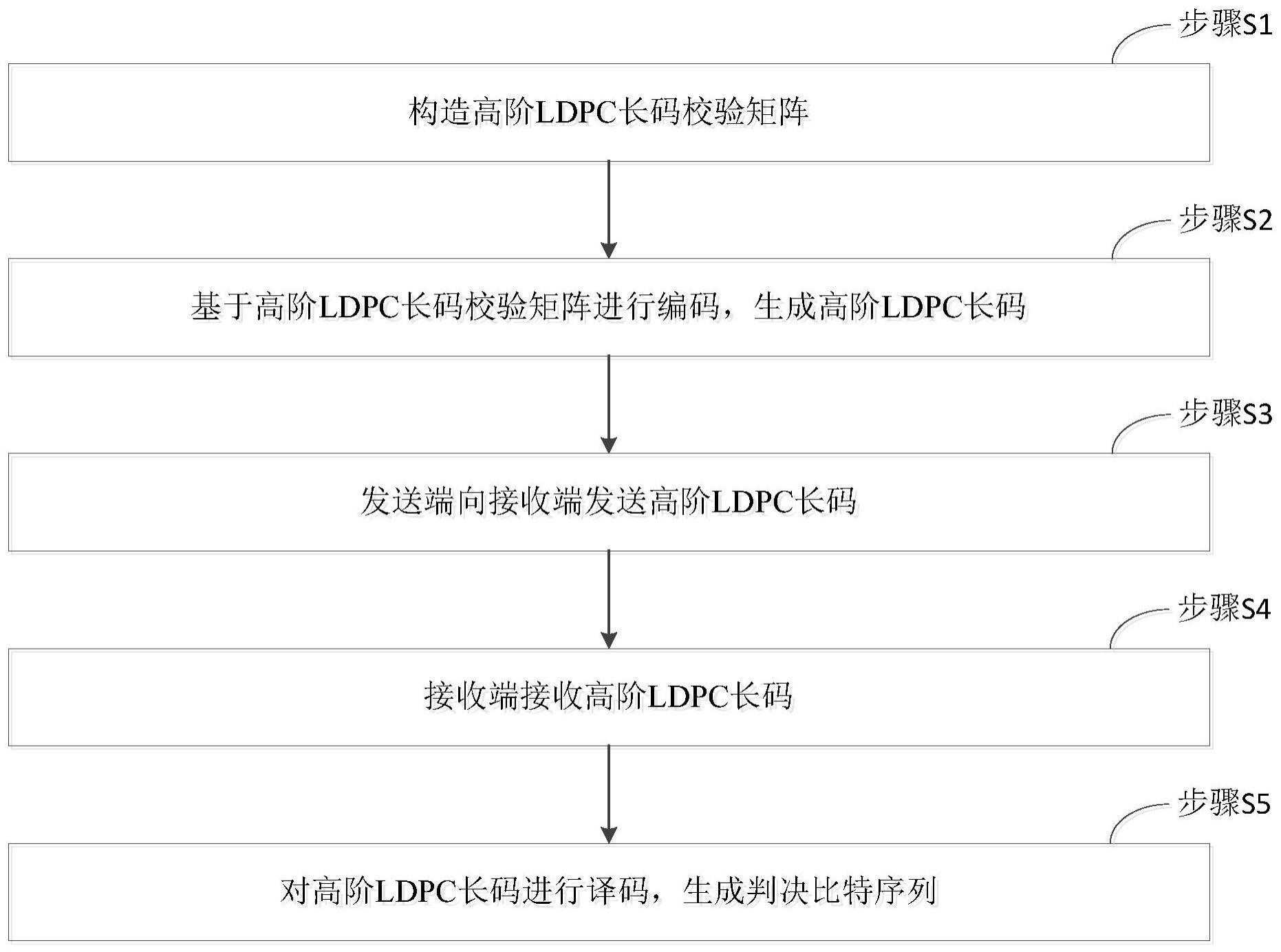

2、为实现上述目的,第一方面,本发明提供了一种基于高阶ldpc长码的通信方法及系统,基于高阶ldpc长码的通信方法应用于通信系统,通信系统包括发送端和接收端,且基于高阶ldpc长码的通信方法包括:构造高阶ldpc长码校验矩阵。基于高阶ldpc长码校验矩阵进行编码,生成高阶ldpc长码。发送端向接收端发送高阶ldpc长码。接收端接收高阶ldpc长码。对高阶ldpc长码进行译码,生成判决比特序列。

3、在本发明的一实施方式中,在发送端构造高阶ldpc长码校验矩阵具体包括:在发送端构造二阶基矩阵。扩展二阶基矩阵,生成高阶校验矩阵。确定扩展因子,产生扩展因子矩阵,生成长码。根据高阶校验矩阵和长码,生成高阶ldpc长码校验矩阵。

4、在本发明的一实施方式中,在发送端构造二阶基矩阵具体为:二阶基矩阵表示为h0=[a0,b0]。a0和b0分别为m0×k0矩阵和为m0×m0方阵,且子矩阵b0为双对角结构。令k0=n0-m0,m0×k0矩阵a0依据符号节点的度分布采用随机法构造。m0×m0方阵b0为一对角阵与其向上循环移位一个单位所得矩阵之和,并令非零元素以确保方阵b0满秩,且m′0∈{1,...,m0-2}。其中,子矩阵b0由其主对角线元素及元素确定。扩展二阶基矩阵,生成高阶校验矩阵具体为:扩展二阶基矩阵h0编码阶数,生成m0×n0高阶校验矩阵hh。确定扩展因子,产生扩展因子矩阵,生成长码具体为:确定扩展因子z,产生m0×n0扩展因子矩阵hz,以生成长码hz。根据高阶校验矩阵和长码,生成高阶ldpc长码校验矩阵具体为:根据高阶校验矩阵hh和长码hz,生成高阶ldpc长码校验矩阵h。

5、在本发明的一实施方式中,发送端基于高阶ldpc长码校验矩阵进行编码,生成高阶ldpc长码具体包括:采用预设运算方法对高阶ldpc长码校验矩阵进行运算,生成高阶ldpc长码。其中,预设运算方法包括列向量求和、加权循环移位方阵求逆、加权循环移位方阵与列向量之积及两个加权循环移位方阵之积。

6、在本发明的一实施方式中,接收端对高阶ldpc长码进行译码,生成判决比特序列具体包括:

7、接收端基于循环移位矩阵的分组译码算法对高阶ldpc长码进行译码,生成判决比特序列;

8、其中,接收端基于循环移位矩阵的分组译码算法对高阶ldpc长码进行译码,生成判决比特序列具体包括:

9、第一步,初始化:

10、第二步,更新符号节点度量:

11、

12、第三步,更新校验节点度量:

13、

14、第四步,重复第二步、第三步直到达到最大迭代次数,计算对数似然值:

15、

16、其中,通过对数似然值,由每列最大值对应的行序确定判决符号序列进而生成判决比特序列

17、第二方面,本发明提供了一种基于高阶ldpc长码的发送方法,应用于通信系统,通信系统包括发送端,且该方法包括:构造高阶ldpc长码校验矩阵。基于高阶ldpc长码校验矩阵进行编码,生成高阶ldpc长码。发送端发送高阶ldpc长码。其中,接收高阶ldpc长码的接收端对高阶ldpc长码进行译码,生成判决比特序列。

18、第三方面,本发明提供了一种基于高阶ldpc长码的接收方法,应用于通信系统,通信系统包括接收端,其特征在于,方法包括:接收高阶ldpc长码。对高阶ldpc长码进行译码,生成判决比特序列。其中,高阶ldpc长码是发送端基于高阶ldpc长码校验矩阵编码生成的,且高阶ldpc长码校验矩阵是由发送端构造的。

19、第四方面,本发明提供了一种基于高阶ldpc长码的通信系统,包括:发送端以及接收端。发送端包括通信连接的信道编码模块和时空映射模块。以及接收端与发送端通信连接,且接收端包括通信连接的空时检测模块和信道译码模块。

20、第五方面,本发明提供了一种通信装置,包括通信接口和处理器,处理器用于执行计算机程序或指令,使得通信装置执行如上述的通信方法。

21、第六方面,本发明提供了一种计算机可读存储介质,包括计算机程序和指令,当计算机程序或指令在计算机上运行时,使得计算机执行如上述的通信方法。

22、与现有技术相比,根据本发明的基于高阶ldpc长码的通信方法及系统,具有如下有益效果:

23、1、采用间接半随机法构造扩展高阶ldpc长码,具有更高的编码增益和抗删除增益;

24、2、以ieee 802.16e与5g nr为代表的二阶ldpc长码,纠错性能仍有提升空间,本发明正是利用高阶编码的增益填补了这一空间;

25、3、可以更好地适配实际应用中的码长和码率;

26、4、减少了与高阶调制或空时编码级联时提取软信息的损失。

- 还没有人留言评论。精彩留言会获得点赞!