一种互联芯片通信链路检测装置及方法与流程

本发明涉及芯片,具体涉及一种互联芯片通信链路检测装置及方法。

背景技术:

1、近年来,随着集成电路技术的快速发展和数据通信传输性能需求的不断提升,多处理器技术受到了越来越多的关注。互联芯片用于连接不同的处理器,为多处理器之间信息的交互提供了数据通道。互联芯片维护了全局系统数据访存的一致性,对保证数据通信的稳定和可靠起到了极为重要的作用。

2、互联芯片对外物理通信链路采用高速串并转换收发器链路,高速串并转换收发器链路的传输性能是衡量互联芯片整体带宽的关键。伪随机二进制序列是一种只包含0和1的二进制码序列,它可以预先确定并可以重复地产生和复制,又具有随机统计特性,因此常被用来对高速串并转换收发器链路的误码率进行检测。

3、目前,互联芯片一般为固定系统定制,由于互联芯片的带宽受限于系统带宽,因而互联芯片的带宽比较固定。当系统带宽提升时,现有的互联芯片的架构相应地需要重构升级,随之互联芯片的高速串并转换收发器链路也需要重新检测,对应的使用伪随机二进制序列检测高速串并转换收发器链路的逻辑也需要重新调整,缺少通用性,增加了开发成本,影响了开发效率。

技术实现思路

1、有鉴于此,本发明提供了一种互联芯片通信链路检测装置及方法,以解决当系统带宽提升时,使用伪随机二进制序列信号检测互联芯片的串并转换收发器链路的逻辑需要重新调整的问题。

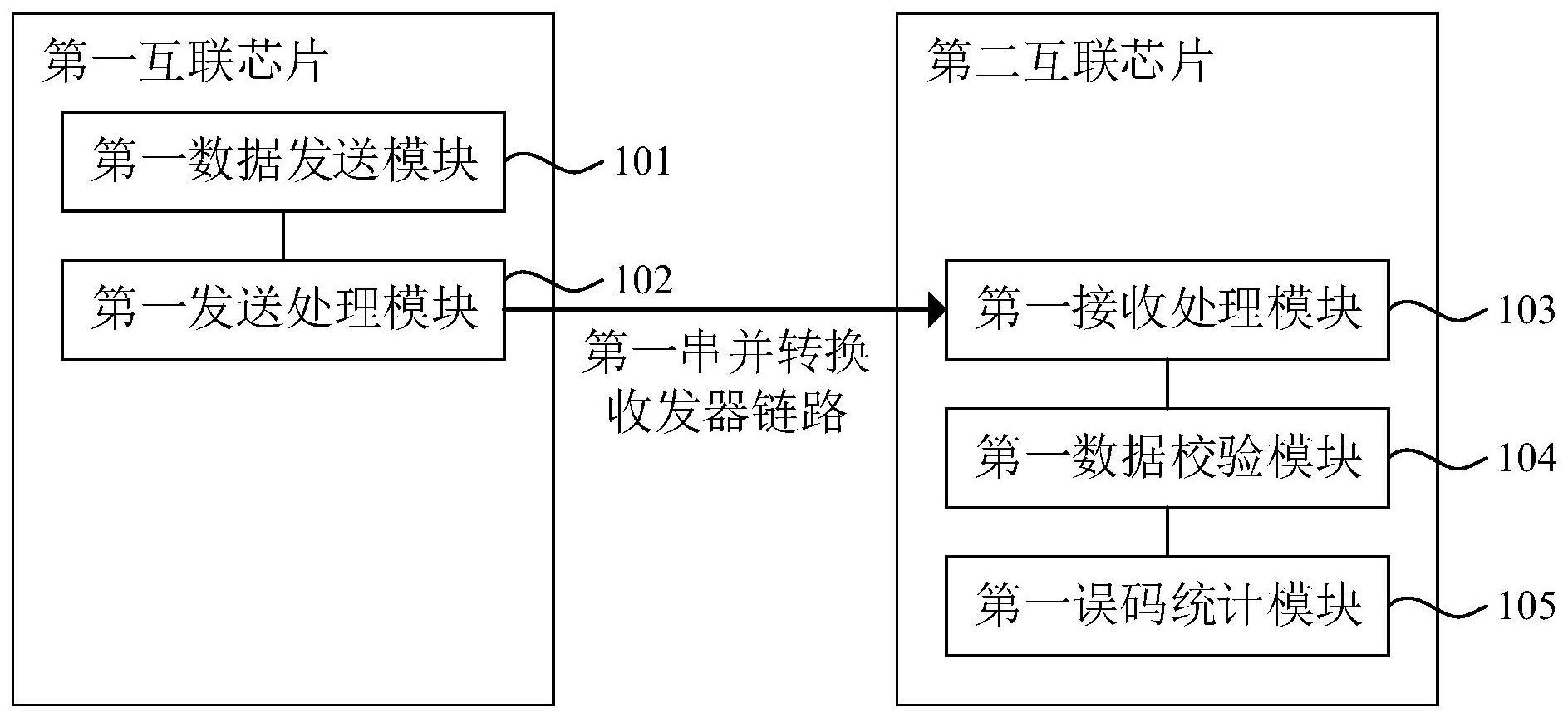

2、第一方面,本发明提供了一种互联芯片通信链路检测装置,包括如下模块:

3、第一数据发送模块,用于根据系统带宽产生第一伪随机二进制序列信号,以及用于将第一伪随机二进制序列信号发送至第一发送处理模块;

4、第一发送处理模块,用于通过第一串并转换收发器链路发送第一伪随机二进制序列信号至第一接收处理模块;

5、第一接收处理模块,用于接收第一伪随机二进制序列信号,以及用于将第一伪随机二进制序列信号转发至第一数据校验模块;

6、第一数据校验模块,用于通过根据系统带宽产生的第二伪随机二进制序列信号校验第一伪随机二进制序列信号,得到校验结果;第一数据校验模块还用于将校验结果发送至第一误码统计模块;

7、第一误码统计模块,用于根据校验结果确定正确数据量和错误数据量,以根据正确数据量和错误数据量确定第一串并转换收发器链路的误码率。

8、其中,第一数据发送模块和第一发送处理模块设置于第一互联芯片上,第一接收处理模块、第一数据校验模块和第一误码统计模块设置于第二互联芯片上。

9、通过本装置,解决了当系统带宽提升时,现有的互联芯片的架构相应地需要重构升级,随之互联芯片的串并转换收发器链路也需要重新检测,对应的使用伪随机二进制序列信号检测串并转换收发器链路的逻辑也需要重新调整的问题,增加了通用性,降低了开发成本,提升了开发效率。

10、在一种可选的实施方式中,本装置的第一数据发送模块,包含多个并行线性反馈移位寄存器产生模块,第一数据发送模块用于根据系统带宽选取对应数量的并行线性反馈移位寄存器产生模块;对应数量的并行线性反馈移位寄存器产生伪随机二进制序列信号和输出值;对应数量的并行线性反馈移位寄存器中的第一个并行线性反馈移位寄存器产生模块的输入值由初始值和除第一个之外的并行线性反馈移位寄存器产生模块的输出值得出;对应数量的并行线性反馈移位寄存器中的除第一个之外的并行线性反馈移位寄存器产生模块的输入值为上一个并行线性反馈移位寄存器产生模块的输出值;合并对应数量的并行线性反馈移位寄存器产生模块产生的伪随机二进制序列信号,形成第一伪随机二进制序列信号。

11、根据系统带宽选取对应数量的并行线性反馈移位寄存器产生模块,合并它们产生的伪随机二进制序列信号,形成第一伪随机二进制序列信号,这样即使系统带宽提升,也能够产生与系统带宽相适应的第一伪随机二进制序列信号。对应数量的并行线性反馈移位寄存器中的第一个并行线性反馈移位寄存器产生模块的输入值由初始值和除第一个之外的并行线性反馈移位寄存器产生模块的输出值得出,除第一个之外的并行线性反馈移位寄存器产生模块的输入值为上一个并行线性反馈移位寄存器产生模块的输出值,这样形成一个循环,能够持续高效地产生第一伪随机二进制序列信号。

12、在一种可选的实施方式中,本装置的第一数据校验模块,用于根据第一伪随机二进制序列信号和第二伪随机二进制序列信号相同,确定第一伪随机二进制序列信号为正确的数据。

13、通过比较第一伪随机二进制序列信号和第二伪随机二进制序列信号,能够简单高效地校验出第一伪随机二进制序列信号是正确数据还是错误数据,进而能够为计算第一串并转换收发器链路的误码率提供了依据。

14、在一种可选的实施方式中,本装置的第一数据校验模块,包含多个并行线性反馈移位寄存器产生模块,第一数据校验模块用于根据系统带宽选取对应数量的并行线性反馈移位寄存器产生模块;对应数量的并行线性反馈移位寄存器产生伪随机二进制序列信号和输出值;对应数量的并行线性反馈移位寄存器中的第一个并行线性反馈移位寄存器产生模块的输入值为第一伪随机二进制序列信号的一部分;对应数量的并行线性反馈移位寄存器中的除第一个之外的并行线性反馈移位寄存器产生模块的输入值为上一个并行线性反馈移位寄存器产生模块的输出值;合并对应数量的并行线性反馈移位寄存器产生模块产生的伪随机二进制序列信号,形成第二伪随机二进制序列信号。

15、根据系统带宽选取对应数量的并行线性反馈移位寄存器产生模块,合并它们产生的伪随机二进制序列信号,形成第二伪随机二进制序列信号,这样即使系统带宽提升,也能够产生与系统带宽相适应的第二伪随机二进制序列信号。对应数量的并行线性反馈移位寄存器中的第一个并行线性反馈移位寄存器产生模块的输入值为第一伪随机二进制序列信号的一部分,除第一个之外的并行线性反馈移位寄存器产生模块的输入值为上一个并行线性反馈移位寄存器产生模块的输出值,这样根据第一伪随机二进制序列信号,能够高效地产生与之对应的第二伪随机二进制序列信号。

16、在一种可选的实施方式中,本装置的第一数据校验模块,还包含多个并行线性反馈移位寄存器产生模块,第一数据校验模块用于根据系统带宽选取对应数量的并行线性反馈移位寄存器产生模块;对应数量的并行线性反馈移位寄存器产生伪随机二进制序列信号和输出值;对应数量的并行线性反馈移位寄存器中的第一个并行线性反馈移位寄存器产生模块的输入值为当前时刻第二伪随机二进制序列信号时最后一个并行线性反馈移位寄存器产生模块的输出值;对应数量的并行线性反馈移位寄存器中的除第一个之外的并行线性反馈移位寄存器产生模块的输入值为上一个并行线性反馈移位寄存器产生模块的输出值;合并对应数量的并行线性反馈移位寄存器产生模块产生的伪随机二进制序列信号,形成第三伪随机二进制序列信号,第三伪随机二进制序列信号用于校验下一时刻形成的第一伪随机二进制序列信号。

17、根据系统带宽选取对应数量的并行线性反馈移位寄存器产生模块,合并它们产生的伪随机二进制序列信号,形成第三伪随机二进制序列信号,这样即使系统带宽提升,也能够产生与系统带宽相适应的第三伪随机二进制序列信号。对应数量的并行线性反馈移位寄存器中的第一个并行线性反馈移位寄存器产生模块的输入值为当前时刻第二伪随机二进制序列信号时最后一个并行线性反馈移位寄存器产生模块的输出值,除第一个之外的并行线性反馈移位寄存器产生模块的输入值为上一个并行线性反馈移位寄存器产生模块的输出值,这样根据当前时刻第二伪随机二进制序列信号时最后一个并行线性反馈移位寄存器产生模块的输出值,能够高效地产生与之对应的第三伪随机二进制序列信号。

18、在一种可选的实施方式中,本装置的第一数据校验模块,用于根据下一时刻形成的第一伪随机二进制序列信号和下一时刻形成的第二伪随机二进制序列信号相同,并且下一时刻产生的第一伪随机二进制序列信号和第三伪随机二进制序列信号不同,确定下一时刻形成的第一伪随机二进制序列信号为丢失的数据。

19、通过比较第一伪随机二进制序列信号和第二伪随机二进制序列信号,以及比较第一伪随机二进制序列信号和第三伪随机二进制序列信号,能够简单高效地校验出第一伪随机二进制序列信号是否是丢失的数据。

20、在一种可选的实施方式中,本装置的第一发送处理模块,根据第一伪随机二进制序列信号的位宽选通第一串并转换收发器链路中对应的通道。

21、互联芯片通信链路由不同的通道绑定组成,本装置的第一发送处理模块,能够根据第一伪随机二进制序列信号的位宽选通第一串并转换收发器链路中相适应的通道。

22、在一种可选的实施方式中,本装置还包括如下模块:

23、第一寄存器配置模块,设置于第一互联芯片,用于配置系统带宽,系统带宽用于供产生第一伪随机二进制序列信号时使用。

24、通过本装置的第一寄存器配置模块,能够灵活地调整系统带宽,以供在检测过程中产生第一伪随机二进制序列信号时使用。

25、在一种可选的实施方式中,本装置还包括如下模块:

26、第二寄存器配置模块,设置于第二互联芯片,用于配置系统带宽,系统带宽用于供产生第二伪随机二进制序列信号时使用。

27、通过本装置的第二寄存器配置模块,能够灵活地调整系统带宽,以供在检测过程中产生第二伪随机二进制序列信号时使用。

28、在一种可选的实施方式中,本装置的第一多路复用器,设置于第一互联芯片,用于根据第一伪随机测试使能信号选通第一伪随机二进制序列信号和第一输入数据。

29、通过本装置的第一多路复用器,能够根据第一伪随机测试使能信号选通第一伪随机二进制序列信号和第一输入数据。

30、在一种可选的实施方式中,本装置的第二多路复用器,设置于第二互联芯片,用于根据第二伪随机测试使能信号选通第一伪随机二进制序列信号和第一输入数据。

31、通过本装置的第二多路复用器,能够根据第二伪随机测试使能信号选通第一伪随机二进制序列信号和第一输入数据。

32、在一种可选的实施方式中,本装置的第一寄存器配置模块,还用于配置第一伪随机测试使能信号,第一伪随机测试使能信号用于控制第一多路复用器选通第一伪随机二进制序列信号和第一输入数据。

33、通过本装置的第一寄存器配置模块,配置第一伪随机测试使能信号,能够控制第一多路复用器选通第一伪随机二进制序列信号和第一输入数据。

34、在一种可选的实施方式中,本装置的第一寄存器配置模块,还用于配置第二伪随机测试使能信号,第二伪随机测试使能信号用于控制第一多路复用器选通第一伪随机二进制序列信号和第一输入数据。

35、通过本装置的第一寄存器配置模块,配置第二伪随机测试使能信号,能够控制第二多路复用器选通第一伪随机二进制序列信号和第一输入数据。

36、在一种可选的实施方式中,本装置还包括如下模块:

37、第二数据发送模块,用于根据系统带宽产生第四伪随机二进制序列信号,以及用于将第四伪随机二进制序列信号发送至第二发送处理模块;

38、第二发送处理模块,用于通过第二串并转换收发器链路发送第四伪随机二进制序列信号至第二接收处理模块;

39、第二接收处理模块,用于接收第四伪随机二进制序列信号,以及用于将第四伪随机二进制序列信号转发至第二数据校验模块;

40、第二数据校验模块,用于通过根据系统带宽产生的第五伪随机二进制序列信号校验第四伪随机二进制序列信号,得到校验结果;第二数据校验模块还用于将校验结果发送至第二误码统计模块;

41、第二误码统计模块,用于根据校验结果确定正确数据量和错误数据量,以根据正确数据量和错误数据量确定第二串并转换收发器链路的误码率。

42、其中,第二数据发送模块和第二发送处理模块设置于第二互联芯片上,第二接收处理模块、第二数据校验模块和第二误码统计模块设置于第一互联芯片上。

43、通过本装置,既能够通过第一串并转换收发器链路从第一串并转换收发器链路发送第一伪随机二进制序列信号到第二互联芯片对第一串并转换收发器链路进行检测,也能通过第二串并转换收发器链路从第二串并转换收发器链路发送第四伪随机二进制序列信号到第一互联芯片对第二串并转换收发器链路进行检测。

44、第二方面,本发明提供了一种互联芯片通信链路检测方法,包括如下步骤:

45、通过第一数据发送模块,根据系统带宽产生第一伪随机二进制序列信号,将第一伪随机二进制序列信号发送至第一发送处理模块;

46、通过第一发送处理模块,将第一伪随机二进制序列信号通过第一串并转换收发器链路发送至第一接收处理模块;

47、通过第一接收处理模块,接收第一伪随机二进制序列信号,将第一伪随机二进制序列信号转发至第一数据校验模块;

48、通过第一数据校验模块,根据系统带宽产生的第二伪随机二进制序列信号,通过第二伪随机二进制序列信号校验第一伪随机二进制序列信号,得到校验结果,将校验结果发送至第一误码统计模块;

49、通过第一误码统计模块,根据校验结果确定正确数据量和错误数据量,以根据正确数据量和错误数据量确定第一串并转换收发器链路的误码率。

50、其中,第一数据发送模块和第一发送处理模块设置于第一互联芯片上,第一接收处理模块、第一数据校验模块和第一误码统计模块设置于第二互联芯片上。

51、通过本方法,解决了当系统带宽提升时,现有的互联芯片的架构相应地需要重构升级,随之互联芯片的串并转换收发器链路也需要重新检测,对应的使用伪随机二进制序列信号检测串并转换收发器链路的逻辑也需要重新调整的问题,增加了通用性,降低了开发成本,提升了开发效率。

- 还没有人留言评论。精彩留言会获得点赞!