一种网络芯片组网仿真验证系统的制作方法

本发明涉及通信,特别是涉及一种网络芯片组网仿真验证系统。

背景技术:

1、随着集成电路的发展,芯片的设计越来越复杂,芯片应用场景也更加广泛。在芯片设计过程中,芯片验证对芯片的成功与否起到了决定性作用,因此芯片验证阶段需要做到充分且完备。

2、目前芯片验证方案都是采用仿真验证平台来完成,主流的仿真验证平台包括eda(electronic design automation,电子设计自动化)、emulation(硬件仿真)、fpga(fieldprogrammable gate array,现场可编程门阵列)等原型验证平台。其中,eda原型验证平台仿真速度较慢,一般适用于芯片验证初期芯片模块级验证。对于系统级验证主要由emulation或者fpga原型验证平台完成。

3、目前部分网络通信芯片的应用场景十分复杂,大多都会涉及多芯片之间的组网场景。而对于以上原型验证平台,一个原型验证设备通常只能模拟一个芯片功能。因此上述单个原型验证平台由于资源限制难以模拟出需要多个芯片的组网模型验证场景。对于这种多个芯片的组网的场景验证,就需要多个原型验证平台来对多颗芯片进行模拟。但这类原型验证平台价格非常昂贵,维护成本也非常高,这种方案无疑大大增加验证成本。如果待验证芯片的组网模型需要的芯片数量较多,该方案成本太高基本无法实现。其次,通常原型验证平台的运行频率较低,当芯片中存在大量的寄存器配置和sram(static random-accessmemory,静态随机存取存储器)/外部存储读写操作,会导致运行时间久,间接地增加了验证时间成本。

技术实现思路

1、本技术实施例的目的在于提供一种网络芯片组网仿真验证系统,以实现在节约芯片验证成本的同时,缩短芯片验证周期,提高芯片设计的质量。具体技术方案如下:

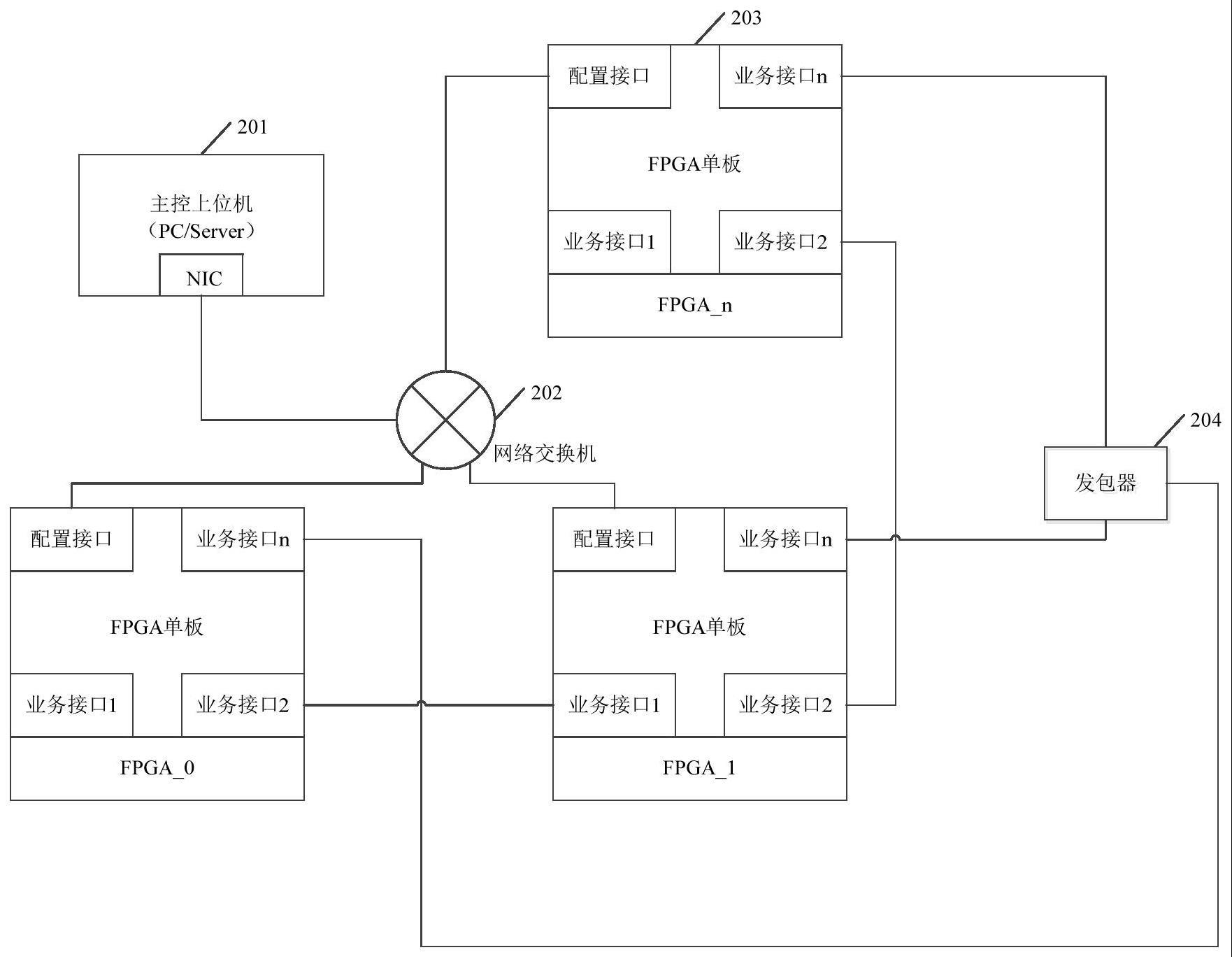

2、本发明实施提供了一种网络芯片组网仿真验证系统,所述系统包括:主控上位机、网络交换机、发包器和至少一个fpga单板,所述主控上位机与每个fpga单板均接入同一网络交换机,每个fpga单板预先被配置为待验证芯片;

3、所述主控上位机,用于将业务流表封装为第一配置报文,向所述网络交换机发送所述第一配置报文;

4、所述网络交换机,用于将接收到的所述第一配置报文转发至所述fpga单板;

5、所述fpga单板,用于解析所述第一配置报文得到所述业务流表;

6、所述发包器,用于构造第一业务报文,并发送所述第一业务报文至所述fpga单板;

7、所述fpga单板,还用于根据所述业务流表对所接收的所述第一业务报文进行转发;

8、所述发包器,还用于接收第二业务报文,所述第二业务报文是经过一个或多个fpga单板转发的业务报文,根据所述第一业务报文和所述第二业务报文进行芯片功能验证。

9、可选的,所述fpga单板包括一个配置接口和至少一个业务接口;

10、所述fpga单板,具体用于通过配置接口接收所述主控上位机发送的配置报文;

11、所述fpga单板,具体还用于通过一个业务接口接收所述第一业务报文,并基于所述第一业务报文的地址信息进行业务流表查找,确定连接下一fpga单板的目的业务接口,并通过所述目的业务接口发送所述第一业务报文。

12、可选的,所述主控上位机,还用于存储多个设备标识,所述设备标识分别标记所述fpga单板的媒体访问控制mac地址,其中,每个fpga单板均预先被设置有与自身对应的mac地址。

13、可选的,所述主控上位机,还用于将寄存器配置信息封装为第二配置报文,向所述网络交换机发送所述第二配置报文;

14、所述网络交换机,还用于将接收到的所述第二配置报文转发至所述fpga单板;

15、所述fpga单板,还用于解析所述第二配置报文得到所述寄存器配置信息,根据所述寄存器配置信息,对寄存器进行初始化配置。

16、可选的,所述fpga单板,具体用于解析所述第二配置报文得到所述寄存器配置信息,根据所述寄存器配置信息,对业务接口和所述fpga单板中的业务转发单元进行初始化配置。

17、可选的,所述fpga单板,还用于在接收到配置报文后,查询所述配置报文携带的mac地址是否与自身预先被设置的mac地址一致,若不是,则丢弃所述配置报文;所述配置报文为第一配置报文或第二配置报文。

18、可选的,所述主控上位机与所述fpga单板之间传递的所述配置报文是基于自定义私有协议封装的。

19、可选的,所述fpga单板,还用于在所述配置报文携带的mac地址与自身预先被设置的mac地址一致时,判断所述配置报文的标识号是否与所述主控上位机发送的基于自定义私有协议封装的报文的标识号一致,若不是,则丢弃所述配置报文。

20、可选的,根据所述第一业务报文和所述第二业务报文进行芯片功能验证可以包括以下的一种或多种:

21、根据所述第一业务报文和所述第二业务报文的负载是否一致;

22、根据所述第一业务报文和所述第二业务报文判断网络芯片组网仿真验证系统转发报文性能是否达到预设标准;

23、根据所述第一业务报文和所述第二业务报文判断网络芯片组网仿真验证系统转发报文过程中是否出现报文错包、丢包;

24、根据所述第一业务报文和所述第二业务报文判断网络芯片组网仿真验证系统转发报文过程中是否有系统异常问题。

25、可选的,所述fpga单板的业务接口通过支持热插拔光模块与另一个fpga单板的业务接口连接。

26、本技术实施例有益效果:

27、本技术实施例提供的一种网络芯片组网仿真验证系统,包括主控上位机、网络交换机、发包器和至少一个fpga单板,主控上位机与每个fpga单板均接入同一网络交换机,每个fpga单板预先被配置为待验证芯片。主控上位机用于将业务流表封装为第一配置报文,向网络交换机发送第一配置报文。网络交换机将接收到的第一配置报文转发至fpga单板,然后fpga单板解析第一配置报文得到业务流表。在配置完成后,发包器构造第一业务报文,并发送第一业务报文至fpga单板。fpga单板根据业务流表对接收的第一业务报文进行转发。发包器在接收第二业务报文后,根据第一业务报文和第二业务报文进行芯片功能验证,其中,第二业务报文是经过一个或多个fpga单板转发的业务报文。在本技术方案中通过fpga单板模拟网络芯片功能,来完成网络芯片组网模型各个场景功能的覆盖验证,在节约成本的同时,提高了芯片设计质量,保证了芯片在组网场景下使用的正确性和稳定性。在主控上位机和fpga单板之间通过自定义私有协议配置报文实现寄存器配置数据交换,因此fpga单板不需要实现协议栈开发工作,节约开发成本。

28、相较于现有技术,fpga单板的运行频率一般在30m~50m左右,而现有技术中其他原型验证平台的运行频率为1m左右。因此,基于fpga单板进行芯片仿真验证,可以有效的缩短芯片验证周期。

29、当然,实施本发明的任一产品或方法并不一定需要同时达到以上所述的所有优点。

- 还没有人留言评论。精彩留言会获得点赞!