一种基于忆阻器的混沌同步系统的构建及FPGA电路实现方法与流程

本发明涉及模拟电路,特别涉及一种基于忆阻器的混沌同步系统的构建及fpga电路实现方法。

背景技术:

1、非线性科学是一门综合性学科,其发展基于以非线性等为特征的各个学科分支,其中,混沌理论作为非线性科学中最重要的部分之一,在保密通信系统、神经网络、人工智能、负荷预测、信号检测等领域具有广阔的应用前景,近年来受到越来越多的关注。混沌系统表现出对初始条件的敏感性以及混沌信号的复杂性,这使得它在非线性科学、信息科学、保密通信以及其他工程领域得到了广泛的应用。在信号检测和处理领域,混沌系统的非线性特性可以用于改善信号的识别和提取,并且混沌信号处理技术可以应用于通信系统、雷达系统等,提高信号的抗干扰能力和信息提取效果。

2、混沌现象的产生主要依赖于电路系统中的非线性器件,现有生成混沌信号的方法主要是通过运放、电容、电阻等分立元件搭建基本运算电路后通过组合连接来实现,这种方案的不足主要体现在以下两点:(1)模拟器件易受温度、电压变化等影响,并且元器件参数会随器件老化而发生变化,环境因素也可能对元器件产生一定的电磁干扰和噪声,使其数值改变,影响实验结果;(2)模拟电路搭建后不能重复使用,每个电路只能对应一种混沌电路,通用性差。

技术实现思路

1、本发明提出一种基于忆阻器的混沌同步系统的构建及fpga电路实现方法,扩展了混沌系统的状态空间和动力学范围,使得系统的动力学行为更加丰富和复杂。

2、具体的,本发明提供了一种基于忆阻器的混沌同步系统的构建及fpga电路实现方法,所述基于忆阻器的混沌同步系统的构建及fpga电路实现方法包括以下步骤:

3、步骤1,对忆阻混沌同步系统进行构建;

4、步骤2,对忆阻混沌同步系统进行离散化处理,得到离散化方程;

5、步骤3,设计fpga混沌信号发生器各个模块,将离散化方程转换为硬件设计语言;

6、步骤4,基于状态机进行设计,对混沌序列进行求解;

7、步骤5,对所设计的程序进行仿真和板级验证,并分析实现效果。

8、更近一步地,在步骤1中,还包括以下步骤:

9、步骤11,将忆阻器加入到van der pol-duffing混沌系统,获取数学模型;

10、步骤12,将数学模型添加一个控制器u,得到基于忆阻器的混沌同步系统模型;

11、步骤13,定义误差系统,将同步系统的同步问题转换成误差系统的稳定性问题。

12、更近一步地,在步骤11中,所述数学模型以及其微分方程为:

13、

14、

15、其中,x(t)表示电压,α表示非线性阻尼系数,f表示正弦信号的幅值,ω表示正弦信号的角频率,表示忆阻器的忆阻值,它由磁通量表示,即a、b均为常数,磁通量等于忆阻器两端电压对时间的积分;x1、x2、x3是该系统的状态变量。

16、更近一步地,在步骤12中,对所述数学模型的微分方程添加控制器u,得到:

17、

18、其中,y1、y2、y3是该系统的状态变量,基于忆阻器的混沌同步系统的公式为:

19、

20、其中,u为控制器,设计控制器u为:

21、

22、其中,u1,u2,u3为常量,e1,e2,e3分别表示y1-x1,y2-x2,y3-x3。

23、更近一步地,在步骤13中,定义误差系统为e=y-x,有:

24、

25、将同步系统的同步问题转换成误差系统的稳定性问题,对于控制器u需要满足i=1,2,3,4。

26、更近一步地,在步骤2中,还包括以下步骤:

27、步骤21,构建忆阻混沌同步系统振子模型;

28、选定控制器参数:u1=0、u2=-2、u3=-1,忆阻混沌同步系统的数学模型可表示为:

29、

30、步骤22,对忆阻混沌同步系统振子模型进行离散化处理

31、使用改进euler算法对上式(7)进行离散化处理,得到如下离散化方程:

32、

33、其中:

34、

35、

36、其中,xn、yn、zn、jn、kn、ln为当前时刻的状态变量离散值,xn+1、yn+1、zn+1、jn+1、kn+1、ln+1为下一时刻的状态变量离散值,h为迭代步长,为驱动力信号。

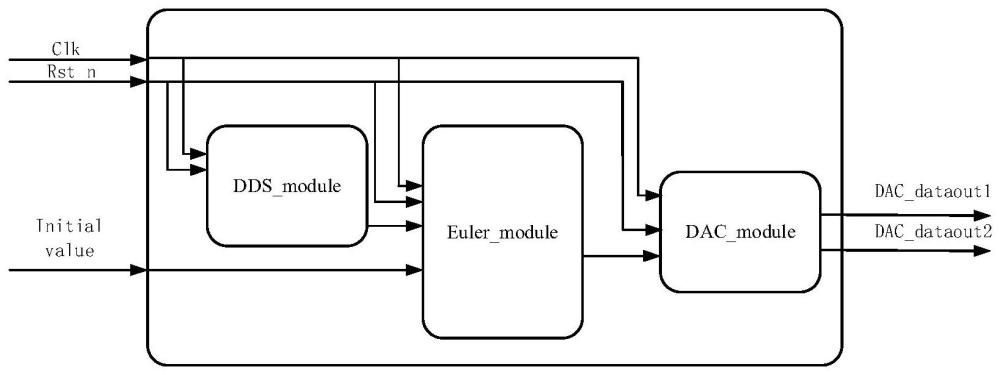

37、更近一步地,在步骤3中,所述fpga混沌信号发生器包括dds模块、euler模块、dac输出模块;

38、所述dds模块产生系统所需的驱动力信号,将正弦信号分解为4096等份,存入fpga的rom块中,通过读取ram的地址,将正弦信号的数值读取出来提供给euler模块进行运算;

39、所述euler模块对输入的离散信号进行计算,得到迭代后的下一时刻的状态变量离散值;

40、所述dac输出模块将euler模块计算后得到的混沌变量值转换为模拟信号,并传输到示波器进行显示。

41、更近一步地,在步骤4中,所述euler模块采用状态机的方式对混沌序列进行求解,状态机的状态包括:

42、s0状态:在主时钟的上升沿初始化所有寄存器,对xn、yn、zn进行赋初始值,并令cnt=0,flag=0,同时状态机跳转到s1状态;

43、s1状态:通过计算w*t的值得到rom的地址,进而读出此时的正弦值,同时计算xn2、yn2,并令flag=0,状态机跳转到s2状态;

44、s2状态:更新计算三次项yn2zn、xn2yn,同时状态机跳转到s3状态;

45、s3状态:在主时钟的上升沿计算fx、fy、fz,同时判断cnt值是否为0,如果cnt为0,状态机跳转到s4状态,如果cnt不为0,状态机跳转到s6状态;

46、s4状态:在主时钟的上升沿保存g1、g2、g3,同时寄存此时的xn、yn、zn值,状态机跳转到s5状态;

47、s5状态:在主时钟的上升沿计算xn+1、yn+1、zn+1,并令cnt=1,更新t值,状态机跳转到s1状态;

48、s6状态:在主时钟的上升沿保存f1、f2、f3,状态机跳转到s7状态;

49、s7状态:计算xn、yn、zn的输出值,令flag为1,状态机跳转到s1状态。

50、本发明达到的有益效果是:

51、本发明提出了一种基于忆阻器的混沌同步系统的构建及fpga电路实现方法。与已知的混沌同步系统相比,该混沌同步系统加入了忆阻器,使其具有更加复杂的动力学行为和抗噪性能,并且能够更快的达到同步状态,误差能够稳定收敛,并且该方案解决现阶段混沌系统使用模拟电路产生的信号不稳定、电路易受外界环境干扰等缺陷,在较大程度上抵抗温度变化和电磁干扰,生成高质量的混沌信号,并且系统同步时间相较于模拟电路更短,稳定性更好,因此在微弱信号检测领域中的应用具有明显的优势。

技术特征:

1.一种基于忆阻器的混沌同步系统的构建及fpga电路实现方法,其特征在于,所述基于忆阻器的混沌同步系统的构建及fpga电路实现方法包括以下步骤:

2.根据权利要求1所述基于忆阻器的混沌同步系统的构建及fpga电路实现方法,其特征在于,在步骤1中,还包括以下步骤:

3.根据权利要求2所述基于忆阻器的混沌同步系统的构建及fpga电路实现方法,其特征在于,在步骤11中,所述数学模型以及其微分方程为:

4.根据权利要求3所述基于忆阻器的混沌同步系统的构建及fpga电路实现方法,其特征在于,在步骤12中,对所述数学模型的微分方程添加控制器u,得到:

5.根据权利要求4所述基于忆阻器的混沌同步系统的构建及fpga电路实现方法,其特征在于,在步骤13中,定义误差系统为e=y-x,有:

6.根据权利要求5所述基于忆阻器的混沌同步系统的构建及fpga电路实现方法,其特征在于,在步骤2中,还包括以下步骤:

7.根据权利要求6所述基于忆阻器的混沌同步系统的构建及fpga电路实现方法,其特征在于,在步骤3中,所述fpga混沌信号发生器包括dds模块、euler模块、dac输出模块;

8.根据权利要求7所述基于忆阻器的混沌同步系统的构建及fpga电路实现方法,其特征在于,在步骤4中,所述euler模块采用状态机的方式对混沌序列进行求解,状态机的状态包括:

技术总结

本发明提供了一种基于忆阻器的混沌同步系统的构建及FPGA电路实现方法,包括以下步骤:步骤1,对忆阻混沌同步系统进行构建;步骤2,对忆阻混沌同步系统进行离散化处理,得到离散化方程;步骤3,设计FPGA混沌信号发生器各个模块,将离散化方程转换为硬件设计语言;步骤4,基于状态机进行设计,对混沌序列进行求解;步骤5,对所设计的程序进行仿真和板级验证,并分析实现效果。本发明在沌同步系统加入了忆阻器,使其具有更加复杂的动力学行为和抗噪性能,能够更快的达到同步状态,误差能够稳定收敛;该方案解决现阶段混沌系统使用模拟电路产生的信号不稳定、电路易受外界环境干扰等缺陷,能够抵抗温度变化和电磁干扰,生成高质量的混沌信号。

技术研发人员:左超,陈盟,王作帅,王建勋,肖涵琛,耿攀,董凯锋,周优优,晋芳,宋俊磊

受保护的技术使用者:中国船舶集团有限公司第七一九研究所

技术研发日:

技术公布日:2024/2/1

- 还没有人留言评论。精彩留言会获得点赞!