数据传输方法和相关设备与流程

本技术涉及通信,尤其涉及一种数据传输方法和相关设备。

背景技术:

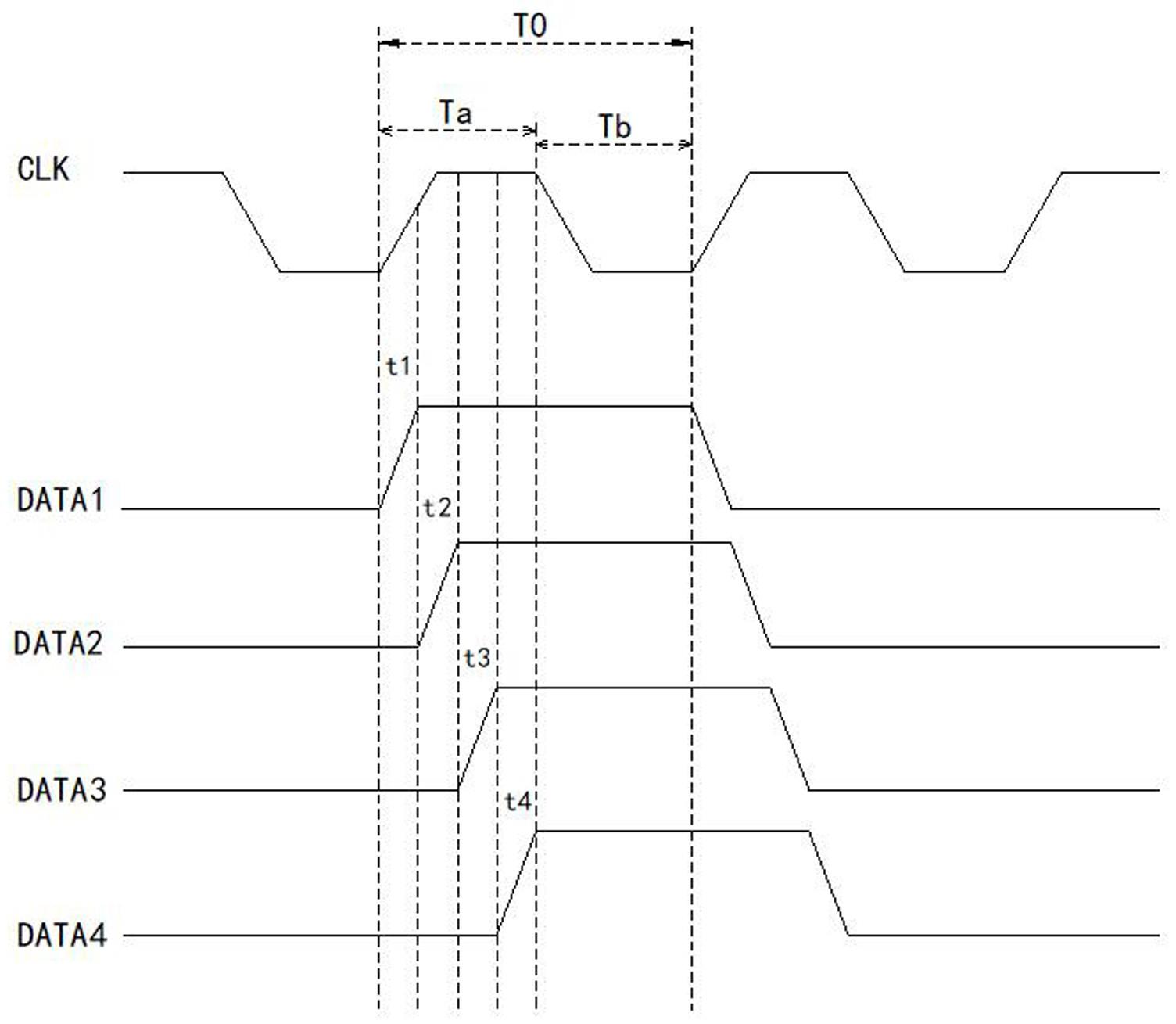

1、在通信技术中,时钟脉冲信号(简称时钟信号)是按一定电压幅度、一定时间间隔连续发出的信号。时钟脉冲信号之间的时间间隔称为时钟周期,而将在单位时间(如1秒)内所产生的脉冲个数称为时钟频率,每个时钟周期具有上升沿和下降沿。图1示出了一组时钟脉冲信号,其中,一个时钟脉冲周期的时间为t,并至少包括上升沿时段和下降沿时段。

2、当两个通信设备之间进行数据传输时,若采用同步通信进行数据传输,传输链路上有负责传递数据信息的通道,另外还需要一条时钟线,以专门传递时钟信号。在发送数据时,发送端要按照一定的时钟频率发送数据,如100hz,代表1秒内有100个时钟脉冲,可以在每个时钟脉冲处于上升沿或者下降沿时,在数据链路发送一个电平信号,100hz则可以发送100个电平信号,而在数据的接收端也需要按照同样的时钟频率,在上升沿或者下降沿来接收数据,才能完成整个数据的传输。

3、诸如,在显示屏检测领域,通常需要用图形信号发生器(pattern generator,pg)对未出厂的液晶显示屏半成品进行画面异常检测。具体操作时,需要pc端向pg发送图像数据、控制指令以及屏端各种参数以完成检测。为了节省成本,往往利用fpga芯片来处理高速的图像数据,而单片机用于下放速率较低的指令信息及屏端的各种参数。不同的屏,在进行通讯时能够支持的传输协议有所不同,如iic、spi、qspi等,单片机在下发数据时,需要根据屏端规定的协议传输数据。

4、如qspi协议,要求同时并行传输四路数据,因此,利用单片机工作时,需要进行串并转换。目前,单片机输出并行数据,采用的是固定延迟输出数据,具体方法是:单片机控制单条数据线的0与1的转换来传输数据,那么在多条数据线的数据传输过程中单片机需要控制一条数据线来传输数据,待这条线数据传输完后,再换为下一条数据线传输数据,直到所有的数据线的数据发送完成。这样,在一条数据线传输数据的时候,其他数据线都是在延迟等待,一直等轮到该数据线发送数据为止。

5、因为一些芯片例如单片机,本身硬件不支持并行操作,故采用前述固定延迟的方式来传输数据,但这会导致数据传输的速率较慢,影响传输效率。例如,对于包含4条数据线的通信系统,采用固定延迟传输方式,在8个时钟周期一共只能传输8个比特(bit)的数据;而对于具有并行传输能力的通信设备(例如fpga设备),在8个时钟周期,每条数据线均可以传输8个比特的数据,那么在8个时钟周期内4条数据一共可以传输8×4=32个比特的数据,但fpga设备存在硬件成本较高的缺点。

技术实现思路

1、有鉴于此,本技术提出一种数据传输方法和相关设备。

2、第一方面,本技术一种向数据接收端发送数据的方法,应用于具有n个数据输出端口的数据发送端,n不小于2,所述n个数据输出端口分别为第1至第n数据输出端口,所述n个数据输出端口分别通过n个数据线连接至所述数据接收端,且所述数据发送端与所述数据接收端之间连接有用于传送时钟信号的时钟线,所述时钟信号包括多个时钟周期,每个所述时钟周期包括在先时段和在后时段,所述在先时段和所述在后时段中的一者包括所述时钟周期的上升沿时段,另一者包括所述时钟周期的下降沿时段,所述在先时段包括n个子时段,所述n个子时段按照时序依次为第1至第n子时段,所述方法包括:

3、对于所述多个时钟周期中的每一个时钟周期:

4、在所述第1子时段,使所述第1数据输出端口产生第1个比特的数据;

5、在所述第2子时段,使所述第2数据输出端口产生第2个比特的数据;

6、依此类推,在所述第n子时段,使所述第n数据输出端口产生第n个比特的数据。

7、在一些可能的实施方式中,所述n个子时段等分设置。

8、在一些可能的实施方式中,所述数据发送端为单片机或fpga芯片。

9、第二方面,本技术提出一种在数据发送端和数据接收端之间传输数据的方法,所述数据发送端具有n个数据输出端口,n不小于2,所述n个数据输出端口分别为第1至第n数据输出端口,所述n个数据输出端口分别通过n个数据线连接至所述数据接收端,且所述数据发送端与所述数据接收端之间连接用于传送时钟信号的时钟线,所述时钟信号包括多个时钟周期,每个所述时钟周期包括在先时段和在后时段,所述在先时段和所述在后时段的一者包括所述时钟周期的上升沿时段,另一者包括所述时钟周期的下降沿时段,所述在先时段包括n个子时段,所述n个子时段按照时序依次为第1至第n子时段,所述方法包括:

10、对于所述多个时钟周期中的每一个时钟周期:

11、在所述第1子时段,所述数据发送端使所述第1数据输出端口产生第1个比特的数据;

12、在所述第2子时段,所述数据发送端使所述第2数据输出端口产生第2个比特的数据;

13、依此类推,在所述第n子时段,所述数据发送端使所述第n数据输出端口产生第n个比特的数据;

14、在所述在后时段,所述数据接收端读取每个所述数据线上的数据。

15、在一些可能的实施方式中,所述n个子时段等分设置。

16、在一些可能的实施方式中,所述数据发送端为单片机或fpga芯片,所述数据接收端均为fpga芯片。

17、第三方面,本技术提出一种数据发送端,包括:

18、至少两个数据输出端口,

19、存储器,

20、处理器,及

21、存储在所述存储器中并可被所述处理器执行的程序指令;

22、当所述程序指令被所述处理器执行时,使所述数据发送端执行如第一方面所述的方法。

23、第四方面,本技术提出一种芯片,包括:

24、至少两个数据输出端口,

25、存储器,

26、处理器,及

27、存储在所述存储器中并可被所述处理器执行的程序指令;

28、当所述程序指令被所述处理器执行时,使所述数据发送端执行如第一方面所述的方法。

29、第五方面,本技术提出一种通信系统,包括:

30、数据发送端,具有n个数据输出端口,n不小于2,并包括第一存储器、第一处理器、及存储在所述第一存储器中并可被所述第一处理器执行的第一程序指令;

31、数据接收端,包括第二存储器、第二处理器、及存储在所述第二存储器中并可被所述第二处理器执行的第二程序指令;

32、n个数据线,分别将所述n个数据输出端口连接至所述数据接收端;

33、时钟线,连接所述数据发送端和所述数据接收端;

34、其中,当所述第一程序指令被所述第一处理器执行,且所述第二程序指令被所述第二处理器执行时,使所述通信系统执行如第二方面所述的方法。

35、第六方面,本技术提出一种计算机可读存储介质,存储有程序指令,当所述程序指令在通信设备上运行时,使所述通信设备执行如第一方面或第二方面所述的方法。

36、根据本技术提出的数据传输方法,发送端在一个时钟周期的在先时段的内部灵活分配多个数据通道的时长占比,并让接收端在一个时钟周期的在后时段读取各通道上的数据,既可以保证数据传输效率,又有助于节省硬件成本。

- 还没有人留言评论。精彩留言会获得点赞!