多通道错误码元标志的数量确定方法、装置、设备及介质与流程

本发明涉及计算机通信领域,特别涉及一种多通道错误码元标志的数量确定方法、装置、设备及介质。

背景技术:

1、rs(即reed-solomon)解码是fec(即forward error correction,前向纠错码)解码技术,它被广泛应用于通信系统中的编码技术以保证数据的准确性,它的基本思路是在发送端,把要发送的信息重新编码,加入一定的冗余校验信息,组成长度较长的codeword(即码块),待到达接收端之后,如果错误在可纠范围之内,通过解码检查后纠正错误,从而降低误码率,提高通信系统的可靠性。在光通信系统中,通过fec的处理,可以以很小的冗余开销,有效降低系统的误码率,延长传输距离,实现降低系统成本的目的。

2、虽然rs并行解码已被广泛应用,但大多数应用于rs(255,239)等,虽然有应用于rs(544,514),或者提出了rs解码器的实现方式,直接解码后也只是将数据恢复,并没有给出多通道错误symbol的计算方法。目前只有集成在fpga(即field programmable gatearray,可编程逻辑器件)芯片内部的硬核rs解码器ip,但需要购买lisence,有些硬核也给出了多通道错误symbold的数量,也有些组织或企业已经实现,但以上实现方式都保密。虽然有些论文或专利中提出了100grs解码器,但很少给出多通道错误symbol数量计算方法,400g rs解码器多通道错误symbol的计算方法对于衡量单通道的信号质量、抖动、性能尤为重要,对于研发设计模块或者优化模块通道时起到关键的指导作用。

3、由上可见,在rs并行解码过程中,如何提供一种多通道错误symbol数量的计算方式是本领域有待解决的问题。

技术实现思路

1、有鉴于此,本发明的目的在于提供一种多通道错误码元标志的数量确定方法、装置、设备及介质,能够实现多通道错误symbol数量的计算。其具体方案如下:

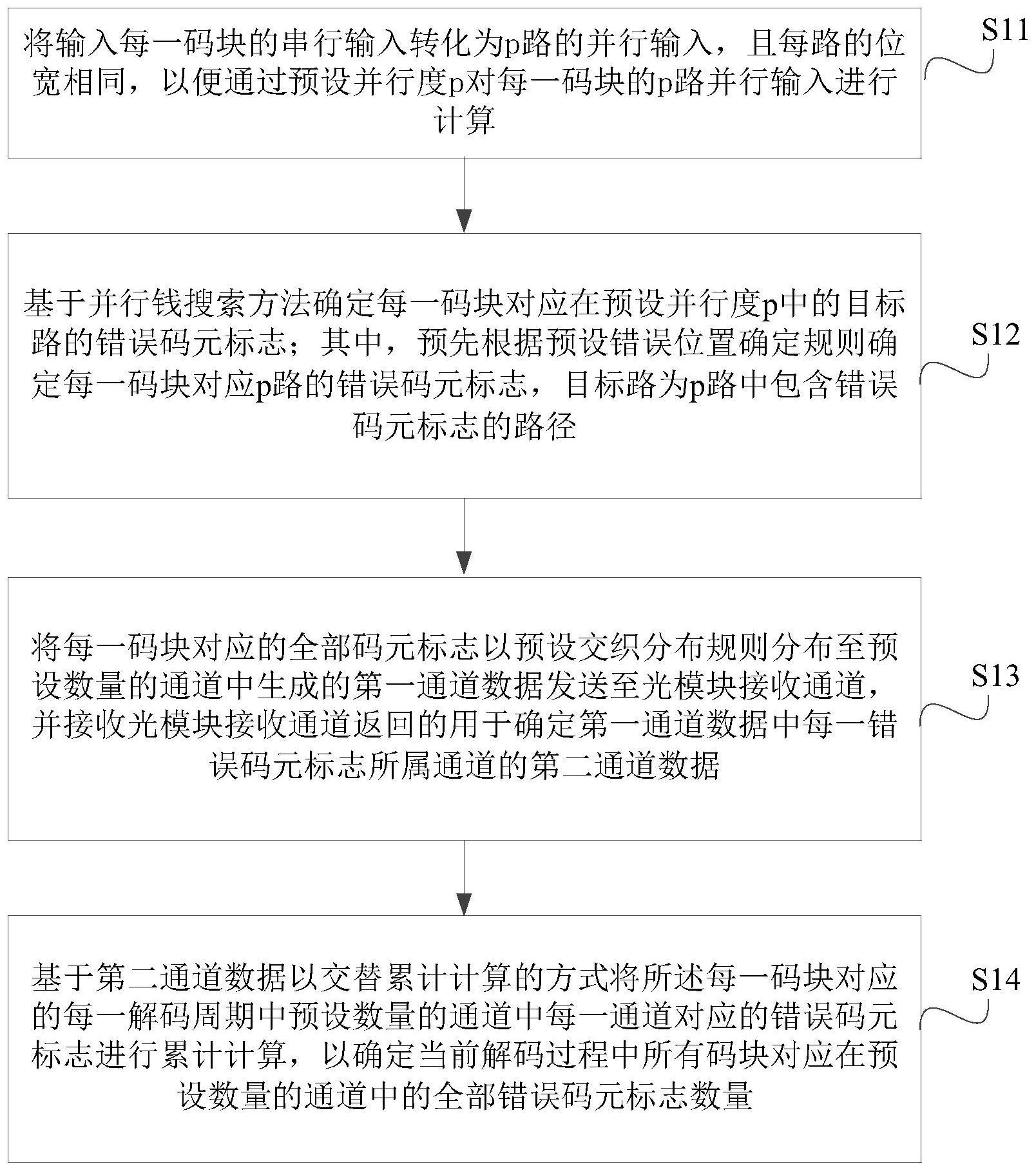

2、第一方面,本技术公开了一种多通道错误码元标志的数量确定方法,包括:

3、将输入每一码块的串行输入转化为p路的并行输入,且每路的位宽相同,以便通过预设并行度p对所述每一码块的p路并行输入进行计算;

4、基于并行钱搜索方法确定所述每一码块对应在所述预设并行度p中的目标路的错误码元标志;其中,预先根据预设错误位置确定规则确定所述每一码块对应p路的错误码元标志,所述目标路为p路中包含错误码元标志的路径;

5、将所述每一码块对应的全部码元标志以预设交织分布规则分布至预设数量的通道中生成的第一通道数据发送至光模块接收通道,并接收所述光模块接收通道返回的用于确定所述第一通道数据中每一错误码元标志所属通道的第二通道数据;

6、基于所述第二通道数据以交替累计计算的方式将所述每一码块对应的每一解码周期中所述预设数量的通道中每一通道对应的错误码元标志进行累计计算,以确定当前解码过程中所有码块对应在所述预设数量的通道中的全部错误码元标志数量。

7、可选的,所述基于并行钱搜索方法确定每一码块对应在预设并行度p中的目标路的错误码元标志,包括:

8、基于并行钱搜索方法确定当前解码过程中每一解码周期中以预设并行度p为依据确定的错误位置多项式系数,并基于每一解码周期对应的所述错误位置多项式系数确定错误位置多项式;

9、将所述预设并行度p中所述错误位置多项式中偶数项相加值与奇数项相加值相等时对应的路确定为包含错误码元标志的目标路。

10、可选的,所述将所述每一码块对应的全部码元标志以预设交织分布规则分布至预设数量的通道中生成的第一通道数据发送至光模块接收通道,包括:

11、通过高速光收发器的发送端将所述每一码块对应的全部码元标志以预设交织分布规则分布至预设数量的通道中生成的第一通道数据发送至光模块接收通道;

12、相应的,所述接收所述光模块接收通道返回的用于确定所述第一通道数据中每一错误码元标志所属通道的第二通道数据,包括:

13、通过高速光收发器的接收端接收所述光模块接收通道返回的用于确定所述第一通道数据中每一错误码元标志所属通道的第二通道数据。

14、可选的,所述基于并行钱搜索方法确定每一码块对应在预设并行度p中的目标路的错误码元标志,包括:

15、利用位宽为p比特的寄存器基于并行钱搜索方法确定每一码块对应在预设并行度p中的目标路的错误码元标志。

16、可选的,所述基于所述第二通道数据以交替累计计算的方式将所述每一码块对应的每一解码周期中所述预设数量的通道中每一通道对应的错误码元标志进行累计计算,以确定当前解码过程中所有码块对应在所述预设数量的通道中的全部错误码元标志数量,包括:

17、定义用于计算每一码块对应预设数量的通道中每一通道对应的错误码元标志值的第一计算组与第二计算组;

18、基于每一码块的起始输入信号确定用于控制电平翻转的目标标志位;

19、利用基于所述第二通道数据、所述第一计算组、第二计算组以及所述目标标志位确定的错误标志交替累计方法,将所述每一码块对应的每一解码周期中所述预设数量的通道中每一通道对应的错误码元标志进行累计计算,以确定当前解码过程中所有码块对应在所述预设数量的通道中的全部错误码元标志数量。

20、可选的,所述利用基于所述第二通道数据、所述第一计算组、第二计算组以及所述目标标志位确定的错误标志交替累计方法,将所述每一码块对应的每一解码周期中所述预设数量的通道中每一通道对应的错误码元标志进行累计计算的过程中,包括:

21、当所述目标标志位为第一标志位时,利用所述第二通道数据为所述第一计算组赋值,并将所述第二计算组赋值为0;

22、当所述目标标志位为第二标志位时,利用所述第二通道数据为所述第二计算组赋值,并将所述第一计算组赋值为0。

23、可选的,所述基于所述第二通道数据以交替累计计算的方式将所述每一码块对应的每一解码周期中所述预设数量的通道中每一通道对应的错误码元标志进行累计计算,以确定当前解码过程中所有码块对应在所述预设数量的通道中的全部错误码元标志数量的过程中,包括:

24、生成用于对码块的输入信号进行计数的计数器,以便当所述计数器中的计数值为当前码块对应的目标周期数时,控制所述计数器中的计数进行更新,并控制用于记录码块处理过程的目标信号的标志位切换为表征当前码块处理完成的标志位;

25、当所述目标信号的标志位为表征当前码块处理完成的标志位时,利用当前所述第一计算组与所述第二计算组中的计算值对错误码元标志进行累计计算。

26、第二方面,本技术公开了一种多通道错误码元标志的数量确定装置,包括:

27、输入转化模块,用于将输入每一码块的串行输入转化为p路的并行输入,且每路的位宽相同,以便通过预设并行度p对所述每一码块的p路并行输入进行计算;

28、并行钱搜索模块,用于基于并行钱搜索方法确定每一码块对应在预设并行度p中的目标路的错误码元标志;其中,预先根据预设错误位置确定规则确定所述每一码块对应p路的错误码元标志,所述目标路为p路中包含错误码元标志的路径;

29、数据处理模块,用于将所述每一码块对应的全部码元标志以预设交织分布规则分布至预设数量的通道中生成的第一通道数据发送至光模块接收通道,并接收所述光模块接收通道返回的用于确定所述第一通道数据中每一错误码元标志所属通道的第二通道数据;

30、数据累加模块,用于基于所述第二通道数据以交替累计计算的方式将所述每一码块对应的每一解码周期中所述预设数量的通道中每一通道对应的错误码元标志进行累计计算,以确定当前解码过程中所有码块对应在所述预设数量的通道中的全部错误码元标志数量。

31、第三方面,本技术公开了一种电子设备,包括:

32、存储器,用于保存计算机程序;

33、处理器,用于执行所述计算机程序,以实现前述的多通道错误码元标志的数量确定方法。

34、第四方面,本技术公开了一种计算机存储介质,用于保存计算机程序;其中,所述计算机程序被处理器执行时实现前述公开的多通道错误码元标志的数量确定方法的步骤。

35、本发明的有益效果在于,提供了一种多通道错误码元标志的数量确定方法、装置、设备及介质:先将输入每一码块的串行输入转化为p路的并行输入,以便通过预设并行度p对每一码块的p路并行输入进行计算;基于并行钱搜索方法确定每一码块对应在预设并行度p中的目标路的错误码元标志;其中所述目标路为p路中包含错误码元标志的路径;将所述每一码块对应的全部码元标志以预设交织分布规则分布至预设数量的通道中生成的第一通道数据发送至光模块接收通道,并接收所述光模块接收通道返回的用于确定所述第一通道数据中每一错误码元标志所属通道的第二通道数据;基于所述第二通道数据以交替累计计算的方式将所述每一码块对应的每一解码周期中所述预设数量的通道中每一通道对应的错误码元标志进行累计计算,以确定当前解码过程中所有码块对应在所述预设数量的通道中的全部错误码元标志数量。这样一来,本发明中通过并行钱搜索方法确定每一码块对应在预设并行度p中的目标路的错误码元标志,并在确定每一错误码元标志所属通道后,以交替累计计算的方式将所述每一码块对应的每一解码周期中所述预设数量的通道中每一通道对应的错误码元标志进行累计计算,以确定当前解码过程中所有码块对应在所述预设数量的通道中的全部错误码元标志数量,最终解决了多通道错误symbol数量计算问题,实现了多通道错误symbol数量的计算。

- 还没有人留言评论。精彩留言会获得点赞!