并行传输下IQ延迟对齐与定时同步联合实现方法和系统与流程

本发明涉及无线通信,尤其涉及并行传输下iq延迟对齐与定时同步联合实现方法和系统。

背景技术:

1、在无线通信系统中,由于发送端或接收端的滤波器等模拟器件的性能不完全一致,同相分量i与正交分量q两路信号分别经过不同的器件和线路后,所受到的延迟量不同,会使i、q两路时域信号有一个相对群延迟,即iq延迟误差,产生噪声干扰,从而导致系统性能下降。同时,由于接收端模数转换器(analog-to-digital converter,adc)和发送端数模转换器(digital-to-analog converter,dac)之间采样频率存在差异,造成接收端实际采样时刻和最佳采样时刻出现偏差,即定时误差,影响了接收机的解调性能。而且随着通信系统的传输速率不断提升,符号速率越高,iq延迟误差和定时误差对接收机解调性能的影响更加明显。在传统低速率系统中,对于iq延迟精度100ps的器件,若符号速率是100mhz,符号间隔是10ns,则iq延迟的影响可忽略;且可以通过多倍符号速率过采样,并从中选择一个最佳采样点输出,从而实现定时同步。但在高速系统中,若符号速率是10ghz,符号间隔为100ps,则iq延迟误差会导致接收机无法正常工作;而且定时同步所需的多倍采样率高达数十ghz,对adc的采样率要求极高,难以实现。因此,对无线通信系统中的接收机进行iq延迟误差补偿和定时误差校正非常重要。

2、常规的iq延迟误差补偿方式是在数字基带通过一个fir插值滤波器来做卷积运算,以获得对应延迟下的接收信号,达到i/q两路时域信号对齐的目的。经典的定时误差计算方法为gardner 算法,通过两倍符号速率采样下的两个采样点得到定时误差估计值。所以,在利用gardner算法计算定时误差之前,需要将采样率转换到两倍过采样频率,两倍过采样信号则可以通过插值滤波器来实现。因此,iq延迟校正和定时同步独立实现时需要使用两个fir滤波器。然而,对于超高传输速率的无线通信链路,数字基带必须通过提高计算的并行度才能实现极高的吞吐率,且高并行度需要消耗更多的硬件资源,带来较高的逻辑复杂度。因此,如何尽可能地减少滤波器的使用,节约乘法器和加法器等逻辑资源,并在硬件上实现高速并行信号处理十分重要。

3、一种现有的基于gardner算法的高速iq延时校正方案如图1所示,通过一个插值滤波器,在获得两倍过采样信号的同时,调整iq两路信号之间的延迟误差,再将两倍过采样信号进行匹配滤波,并根据gardner算法分别提取iq延迟误差和定时误差,iq延迟误差经过一个一阶环路滤波器进行平滑,定时误差经过一个二阶环路滤波器和数控振荡器(numerically controlled oscillator,nco)调整插值采样点的位置,再同时将iq延迟误差和定时误差相位信息送给插值滤波器,以完成定时同步和iq延迟校正。该方案提供的iq延迟校正方案与定时同步相结合,可以有效补偿iq延迟误差的影响,但是插值滤波器没有与匹配滤波进行结合,无法抑制定时同步环路中的带外噪声,不能直接实现采样时刻信噪比(signal-to-noise ratio,snr)的最大化,且在高速并行处理系统中,插值滤波器消耗较多的乘法器和加法器,需要大量逻辑资源。而且定时同步的性能受iq延迟一阶环路滤波器收敛速度的影响。

技术实现思路

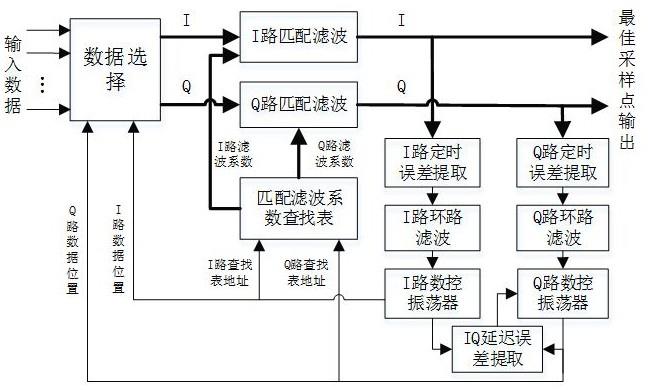

1、本发明的目的在于针对现有技术的不足,本发明拟提出一种面向多路并行传输下iq延迟对齐与定时同步联合实现方法和系统,将并行的插值滤波器和匹配滤波相结合,分别对i/q两路信号做定时误差检测和环路滤波,检测iq延迟误差并对q路信号进行校正,i/q两路定时同步环路收敛速度一致,可在获得最佳采样信号的同时,补偿iq延迟带来的信号损伤,且节约大量的逻辑资源。

2、本发明的技术方案如下:

3、本发明首先提供了一种并行传输下iq延迟对齐与定时同步联合实现系统,其包括:

4、i/q匹配滤波模块,分别对i路和q路输入数据进行低通滤波,获得两倍符号速率下的i路和q路输出信号;

5、i/q两路定时误差提取模块,对i/q匹配滤波模块输出的i路和q路输出信号分别进行定时误差检测,获得i/q两路定时误差均值;

6、i/q环路滤波模块,对i/q两路定时误差均值分别进行平滑处理,获得平滑后的i路定时误差和q路定时误差;

7、i/q数控振荡模块,根据i路定时误差和q路定时误差,计算中心采样点的相位累加值,并获取匹配滤波输入数据的起始位置和匹配滤波系数地址索引;

8、iq延迟误差提取模块,用于提取iq延迟误差;并根据iq延迟误差对q路数控振荡器的累加相位进行校正;

9、数据选择模块,根据匹配滤波输入数据的起始位置获得i路和q路匹配滤波输入数据送给i/q匹配滤波模块;

10、匹配滤波系数查找表,根据匹配滤波系数地址索引查找匹配滤波系数并发送给i/q匹配滤波模块。

11、本发明还提供了一种基于所述系统的iq延迟对齐与定时同步联合实现方法,其包括如下步骤:

12、1)数据选择模块根据i路和q路匹配滤波所需的输入数据的位置从移位寄存器中选择采样输入数据给i/q匹配滤波模块,匹配滤波系数查找表根据匹配滤波系数地址索引选择i路和q路所需的匹配滤波系数输送给i/q匹配滤波模块,

13、2)i/q匹配滤波模块对i路和q路输入数据进行低通滤波,获得两倍符号速率的i路以及q路输出信号;

14、3)i/q两路定时误差提取模块对i路和q路输出信号分别提取定时误差,并获得i/q两路定时误差均值;

15、4)i/q路环路滤波模块对i/q两路定时误差均值分别进行平滑处理,获得平滑后的i路和q路定时误差;

16、5)i/q数控振荡模块根据平滑后的i路和q路定时误差,对中心采样点的相位进行累加;

17、6)iq延迟误差提取模块根据相位累加结果提取iq延迟误差;并根据iq延迟误差对i/q路数控振荡模块中的q路数控振荡器的累加相位进行校正;

18、7)i/q数控振荡模块根据校正后的累加相位,获取匹配滤波输入数据的起始位置并发送给i/q数据选择模块,获取匹配滤波系数地址索引发送给匹配滤波系数查找表;重复步骤1)-步骤7),当i/q两路环路滤波模块同时收敛时,i/q两路匹配滤波的输出信号则为无iq延迟的最佳采样信号,即实现并行传输下的iq延迟对齐与定时同步。

19、与现有技术相比,本发明对i路信号和q路信号分别进行定时误差检测、环路滤波和相位累加,获得i/q两路匹配滤波所需的输入数据和匹配滤波系数。当i/q两路信号同时为最佳采样时刻的信号时,定时同步环路收敛,i/q两路信号之间的相位误差则为iq延迟,输出信号即为无iq延迟的最佳采样信号。本发明能够灵活支持任意倍符号速率的采样和一个符号周期内的iq延时校正,同时解决了定时同步和iq延迟对齐的问题。其中i/q两路定时误差经过相同的环路滤波器,定时环路收敛速度一致,定时同步的性能不受iq延迟收敛速度的限制。相位可配的匹配滤波器与插值滤波器相融合,节省了大量的乘法器和加法器,降低了硬件成本。

- 还没有人留言评论。精彩留言会获得点赞!