毫米波雷达收发前端芯片级联同步方法及级联系统与流程

本公开涉及雷达,可应用于多雷达级联场景下,尤其涉及一种毫米波雷达收发前端芯片级联同步方法及级联系统。

背景技术:

1、4维(4-dimensional,4d)毫米波雷达是指可以获取目标的距离、相对径向速度、方位角度及俯仰角度四个维度信息的毫米波雷达。其中,毫米波收发前端芯片是4维毫米波雷达的核心元器件之一,毫米波收发前端芯片将多通道接收模块、多通道发射模块、调频连续波本振源、模数转换器以及数字接口等核心功能模块集成为单颗片上系统(system onchip,soc)芯片。

2、由于4d毫米波成像雷达的高分辨率测向及高密度点云数据要求,4d毫米波雷达需集成大规模收发通道,典型如16收/16发、32收/32发以及64收/64发等。但受芯片散热、功耗、成本以及良率等因素影响,当前芯片技术水平难以支撑单颗收发前端芯片就集成4d毫米波雷达所需的收发通道数量,因而需要将多颗毫米波收发前端芯片进行级联,实现雷达收发通道数量的扩展。

3、但是,现有的将多颗毫米波收发前端芯片进行级联的方案,各毫米波收发前端芯片在级联之后的一致性较差。

技术实现思路

1、本公开提供了一种毫米波雷达收发前端芯片级联同步方法及级联系统,能够提高多毫米波收发前端芯片级联的一致性。

2、根据本公开的第一方面,提供了一种毫米波雷达收发前端芯片级联同步方法,包括:

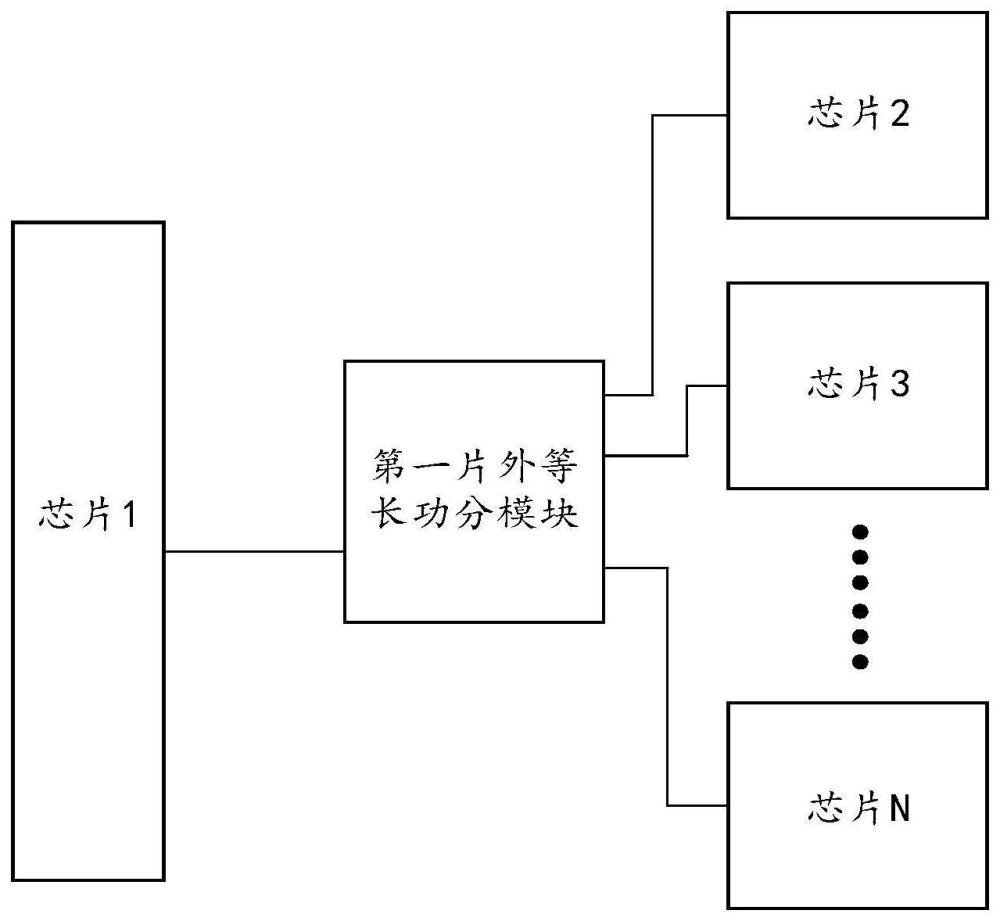

3、第一芯片接收外部参考时钟信号,第一芯片处于主芯片工作模式;第一芯片根据外部参考时钟信号,生成第一参考时钟信号;第一片外等长功分模块将第一参考时钟信号均分为至少两路第二参考时钟信号,并将至少两路第二参考时钟信号中的一路输出至第一芯片,其他路一一对应输出至第二芯片,第二芯片处于从芯片工作模式,至少两路第二参考时钟信号中任意两路第二参考时钟信号到达对应的芯片的时长相差小于第一预设阈值;第一芯片将接收到的第二参考时钟信号,作为第一芯片的内部参考时钟信号;第二芯片将接收到的第二参考时钟信号,作为第二芯片的内部参考时钟信号。

4、进一步地,在第一芯片接收外部参考时钟信号之前,该方法还包括:

5、第一芯片接收第一指令,第一指令用于指示第一芯片进入主芯片工作模式;第二芯片接收第二指令,第二指令用于指示第二芯片进入从芯片工作模式。

6、进一步地,第一芯片和第二芯片均包括参考时钟输出控制模块、主时钟锁相环参考时钟控制模块;其中,进入主芯片工作模式的芯片用于通过参考时钟输出控制模块根据外部参考时钟信号,生成第一参考时钟信号,以及通过主时钟锁相环参考时钟控制模块将接收到的第二参考时钟信号,作为内部参考时钟信号;进入从芯片工作模式的芯片用于通过主时钟锁相环参考时钟控制模块将接收到的第二参考时钟信号,作为内部参考时钟信号。

7、进一步地,该方法还包括:

8、第一芯片根据第一芯片的内部参考时钟信号,生成第一芯片的时序逻辑控制数字时钟信号;第二芯片根据第二芯片的内部参考时钟信号,生成第二芯片的时序逻辑控制数字时钟信号;第一芯片接收波形调制触发信号;第一芯片根据第一芯片的时序逻辑控制数字时钟信号,对波形调制触发信号进行采样,生成第一波形触发同步信号;第二片外等长功分模块根据第一波形触发同步信号,生成至少两路第二波形触发同步信号,并将至少两路第二波形触发同步信号中的一路输出至第一芯片,其他路一一对应输出至第二芯片,至少两路第二波形触发同步信号到达对应的芯片的时长相同;第一芯片根据第一芯片的时序逻辑控制数字时钟信号,对接收到的第二波形触发同步信号进行采样,生成第一芯片的内部波形调制及处理指示信号;第二芯片根据第二芯片的时序逻辑控制数字时钟信号,对接收到的第二波形触发同步信号进行采样,生成第二芯片的内部波形调制及处理指示信号。

9、进一步地,第一芯片和第二芯片均包括主时钟锁相环模块、第一整数分频器、第二整数分频器、时钟同步校准控制模块、第一可控时间延迟模块;其中,第一芯片用于通过主时钟锁相环模块根据得到的内部参考时钟信号,生成高频参考时钟信号,通过第一整数分频器根据高频参考时钟信号,生成调频本振源参考时钟信号;还用于通过第二整数分频器根据生成的高频参考时钟信号,生成初始时序逻辑控制数字时钟信号;还用于通过时钟同步校准控制模块根据得到的内部参考时钟信号和第一可控时间延迟模块的输出信号,通过第一可控时间延迟模块对生成的初始时序逻辑控制数字时钟信号进行时间延迟调整,得到时序逻辑控制数字时钟信号;第二芯片用于通过主时钟锁相环模块根据得到的内部参考时钟信号,生成高频参考时钟信号,通过第二整数分频器根据生成的高频参考时钟信号,生成初始时序逻辑控制数字时钟信号;还用于通过时钟同步校准控制模块根据得到的内部参考时钟信号和第一可控时间延迟模块的输出信号,通过第一可控时间延迟模块对生成的初始时序逻辑控制数字时钟信号进行时间延迟调整,得到时序逻辑控制数字时钟信号。

10、进一步地,第一芯片和第二芯片均还包括第三整数分频器和第二可控时间延迟模块;其中,第一芯片和第二芯片均还用于通过第三整数分频器根据主时钟锁相环模块生成的高频参考时钟信号,生成初始模数转换器采样时钟信号;还用于通过时钟同步校准控制模块根据得到的内部参考时钟信号和第二可控时间延迟模块的输出信号,通过第二可控时间延迟模块对生成的初始模数转换器采样时钟信号进行时间延迟调整,得到模数转换器采样时钟信号。

11、进一步地,第一芯片和第二芯片均还包括第四整数分频器和第三可控时间延迟模块;其中,第一芯片和第二芯片均还用于通过第四整数分频器根据主时钟锁相环模块生成的高频参考时钟信号,生成初始数据接口时钟信号;还用于通过时钟同步校准控制模块根据得到的内部参考时钟信号和第三可控时间延迟模块的输出信号,通过第三可控时间延迟模块对生成的初始数据接口时钟信号进行时间延迟调整,得到数据接口时钟信号。

12、进一步地,该方法还包括:

13、第一芯片根据所述第一芯片的内部参考时钟信号,生成调频本振源参考时钟信号;根据调频本振源参考时钟信号,生成第一调频连续波本振信号;第三片外等长功分模块根据第一调频连续波本振信号,生成至少两路第二调频连续波本振信号,并将至少两路第二调频连续波本振信号中的一路输出至第一芯片,其他路一一对应输出至第二芯片,至少两路第二调频连续波本振信号到达对应的芯片的时长相同;第一芯片将接收到的第二调频连续波本振信号,生成第一芯片的射频信号;第二芯片将接收到的第二调频连续波本振信号,生成第二芯片的射频信号。

14、进一步地,第一芯片和第二芯片均还包括调频本振源模块、调频本振信号输出控制模块、本振信号选择控制模块、倍频器、功分器;其中,第一芯片用于通过调频本振源模块根据调频本振源参考时钟信号,生成调频本振信号,通过调频本振信号输出控制模块根据调频本振源模块得到的调频本振信号,生成第一调频连续波本振信号;还用于通过本振信号选择控制模块将接收到的第二调频连续波本振信号,作为倍频器的输入信号,通过倍频器根据接收到的第二调频连续波本振信号,生成射频信号,通过功分器对射频信号进行功分并输出至收发通道;第二芯片用于通过本振信号选择控制模块将接收到的第二调频连续波本振信号,作为倍频器的输入信号,通过倍频器根据接收到的第二调频连续波本振信号,生成射频信号,通过功分器对射频信号进行功分并输出至收发通道。

15、根据本公开的第二方面,提供了一种毫米波雷达收发前端芯片级联系统,该系统包括:

16、至少两个芯片和第一片外等长功分模块;第一片外等长功分模块分别与每个芯片连接,至少两个芯片包括处于主芯片工作模式的第一芯片和处于主芯片工作模式的第二芯片;第一片外等长功分模块与任意两个所述芯片的连接走线的距离相差小于第二预设阈值;该系统用于实现如第一方面的方法。其中,第一芯片用于根据外部参考时钟信号生成第一参考时钟信号,第一片外等长功分模块用于根据第一参考时钟信号生成至少两路第二参考时钟信号,并将至少两路第二参考时钟信号一一对应地分别输出至至少两个芯片。

17、进一步地,第一片外等长功分模块分别与每个芯片等长走线连接。

18、进一步地,至少两个芯片均包括参考时钟输出控制模块、主时钟锁相环参考时钟控制模块;参考时钟输出控制模块与第一片外等长功分模块连接,第一片外等长功分模块与主时钟锁相环参考时钟控制模块连接。其中,参考时钟输出控制模块用于根据外部参考时钟信号生成第一参考时钟信号;主时钟锁相环参考时钟控制模块用于接收第二参考时钟信号,将第二参考时钟信号作为内部参考时钟信号。

19、进一步地,该系统还包括第二片外等长功分模块,第二片外等长功分模块分别与每个芯片连接。其中,第一芯片还用于生成第一波形触发同步信号,第二片外等长功分模块用于根据第一波形触发同步信号生成至少两路第二波形触发同步信号,并将至少两路第二波形触发同步信号一一对应地分别输出至至少两个芯片。

20、进一步地,至少两个芯片均包括主时钟锁相环模块、第一整数分频器、第二整数分频器、时钟同步校准控制模块、第一可控时间延迟模块;主时钟锁相环模块分别与第一整数分频器、第二整数分频器连接,第二整数分频器与第一可控时间延迟模块连接,时钟同步校准控制模块与第一可控时间延迟模块连接。

21、其中,主时钟锁相环模块用于根据内部参考时钟信号生成高频参考时钟信号;第一整数分频器用于根据高频参考时钟信号生成调频本振源参考时钟信号;第二整数分频器用于根据高频参考时钟信号生成初始时序逻辑控制数字时钟信号;时钟同步校准控制模块用于根据内部参考时钟信号以及第一可控时间延迟模块的输出信号,控制第一可控时间延迟模块对初始时序逻辑控制数字时钟信号进行时间延迟调整,得到时序逻辑控制数字时钟信号;第一可控时间延迟模块用于对初始时序逻辑控制数字时钟信号进行时间延迟调整。

22、进一步地,至少两个芯片均还包括第三整数分频器和第二可控时间延迟模块;主时钟锁相环模块还与第三整数分频器连接,第三整数分频器与第二可控时间延迟模块连接,时钟同步校准控制模块还与第二可控时间延迟模块连接。

23、其中,第三整数分频器用于根据高频参考时钟信号生成初始模数转换器采样时钟信号;时钟同步校准控制模块还用于根据内部参考时钟信号以及第二可控时间延迟模块的输出信号,控制第二可控时间延迟模块对初始模数转换器采样时钟信号进行时间延迟调整,得到模数转换器采样时钟信号;第二可控时间延迟模块用于对初始模数转换器采样时钟信号进行时间延迟调整。

24、进一步地,至少两个芯片均还包括第四整数分频器和第三可控时间延迟模块;主时钟锁相环模块还与第四整数分频器连接,第四整数分频器与第三可控时间延迟模块连接,时钟同步校准控制模块还与第三可控时间延迟模块连接。

25、其中,第四整数分频器用于根据高频参考时钟信号生成初始数据接口时钟信号号;时钟同步校准控制模块还用于根据内部参考时钟信号以及第三可控时间延迟模块的输出信号,控制第三可控时间延迟模块对初始数据接口时钟信号进行时间延迟调整,得到数据接口时钟信号;第三可控时间延迟模块用于对初始数据接口时钟信号进行时间延迟调整。

26、进一步地,该系统还包括第三片外等长功分模块,第三片外等长功分模块分别与每个芯片连接。其中,第一芯片还用于生成第一调频连续波本振信号,第二片外等长功分模块用于根据第一调频连续波本振信号生成至少两路第二调频连续波本振信号,并将至少两路第二调频连续波本振信号一一对应地分别输出至至少两个芯片。

27、进一步地,至少两个芯片均还包括调频本振源模块、调频本振信号输出控制模块、本振信号选择控制模块、倍频器、功分器;

28、调频本振源模块与调频本振信号输出控制模块连接,调频本振信号输出控制模块第三片外等长功分模块连接,第三片外等长功分模块与本振信号选择控制模块连接,本振信号选择控制模块与倍频器连接,倍频器与功分器连接。

29、其中,调频本振源模块用于根据调频本振源参考时钟信号生成调频本振信号;调频本振信号输出控制模块用于根据调频本振信号生成第一调频连续波本振信号;本振信号选择控制模块用于将第二调频连续波本振信号作为倍频器的输入信号;倍频器用于根据接收到的第二调频连续波本振信号,生成射频信号;功分器用于对射频信号进行功分处理。

30、应当理解,本部分所描述的内容并非旨在标识本公开的实施例的关键或重要特征,也不用于限制本公开的范围。本公开的其它特征将通过以下的说明书而变得容易理解。

- 还没有人留言评论。精彩留言会获得点赞!