一种信号完整性检测方法、装置、电子设备及存储介质与流程

本申请涉及信号检测,尤其涉及一种信号完整性检测方法、装置、电子设备及存储介质。

背景技术:

1、随着电子信息技术的飞速发展,高速pcb(printed circuit board,印制电路板)信号传输系统被越来越多地应用在通信、计算机、电子产品等领域。随着信号频率的提高,电路板从单层板和双层板发展到了多层电路板。当信号传输速度速率达到50mhz时,相应的电路板就被定义成高速pcb。对于高速pcb,如果高频率信号的传输线延迟超过信号上升时间的一半时,将产生传输线效应,极易造成信号完整性问题。电子设备对信号传输和处理速度具有较高需求的同时,对如何保证pcb板信号传输完整性也提出了较高要求。

2、目前较多电子产品都向着超薄轻巧的方向发展,其高速pcb主板在走线上非常密集,由于传输的信号频率太高,易导致传输线之间的信号干扰,并进一步造成电子设备故障。对于电子设备的此类故障无法通过排除法进行检测实现对元器件的检测,并且目前的高速pcb板信号完整性检测方法存在检测耗时过长、检测完整性较低等问题。

技术实现思路

1、本申请实施例为了解决上述技术问题,提供一种信号完整性检测方法、装置、电子设备及存储介质。

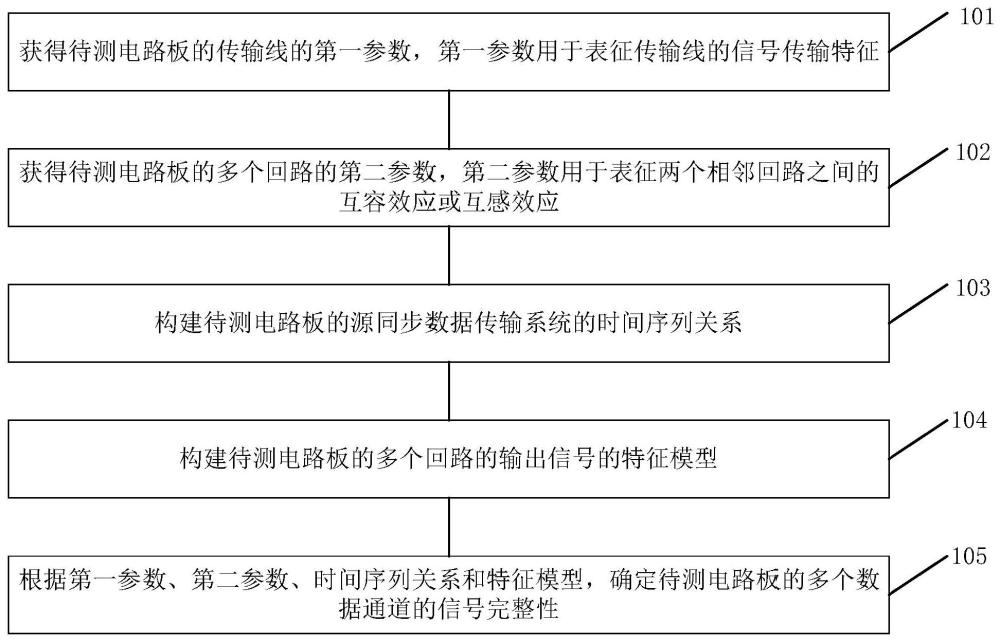

2、根据本申请第一方面,提供了一种信号完整性检测方法,所述方法包括:获得待测电路板的传输线的第一参数,所述第一参数用于表征所述传输线的信号传输特征;获得所述待测电路板的多个回路的第二参数,所述第二参数用于表征两个相邻回路之间的互容效应或互感效应;构建所述待测电路板的源同步数据传输系统的时间序列关系;构建所述待测电路板的多个所述回路的输出信号的特征模型;根据所述第一参数、所述第二参数、所述时间序列关系和所述特征模型,确定所述待测电路板的多个数据通道的信号完整性。

3、根据本申请一实施方式,所述第一参数为定向阻抗;相应的,所述获得待测电路板的传输线的第一参数,包括:确定所述传输线的单位长度和所述单位长度的传输线的电容;检测所述传输线的传输延迟;根据所述单位长度、所述电容值和所述传输延迟,确定所述定向阻抗。

4、根据本申请一实施方式,所述第二参数包括电流逆差;相应的,所述获得所述待测电路板的多个回路的第二参数,包括:在所述两个相邻回路的第一回路电压发生变化时,获取所述第一回路的电压变化率和所述两个相邻回路的互容值;根据所述电压变化率和所述互容值,确定所述电流逆差。

5、根据本申请一实施方式,所述第二参数还包括电压逆差;相应的,所述获得所述待测电路板的多个回路的第二参数,包括:在所述两个相邻回路的第一回路电流发生变化时,获取所述第一回路的电流变化率和所述两个相邻回路的互感值;根据所述电流变化率和所述互感值,确定所述电压逆差。

6、根据本申请一实施方式,所述构建所述待测电路板的源同步数据传输系统的时间序列关系,包括:将所述多个回路的数据传输至所述源同步数据传输系统的数据转换器;获取数据转换器的内部低频传输延时时间和高频传输延时时间;获取所述源同步数据传输系统的源数据输出的最短时间和输出数据的有效保留时间;基于所述低频传输延时时间、所述高频传输延时时间、所述源数据输出的最短时间和所述有效保留时间,确定数据传输到终端时的有效传输时间和接收数据保留的有效接收时间。

7、根据本申请一实施方式,所述构建所述待测电路板的多个所述回路的输出信号的特征模型,包括:将设定芯片的信号传输驱动前端作为线性结构,所述设定芯片作为高速数据实时采集芯片,对回路的输出信号进行采集;获得所述回路的驱动时间和驱动效果;根据所述驱动时间和驱动效果模拟建立所述回路的输出信号的特征模型。

8、根据本申请一实施方式,所述根据所述第一参数、所述第二参数、所述时间序列关系和所述特征模型,确定所述待测电路板的多个数据通道的信号完整性,包括:基于所述第一参数、所述第二参数、所述时间序列关系和所述特征模型,在所述传输线的为不同长度时,对所述待测电路板的状态进行模拟;获得在所述传输线的为不同长度时所述待测电路板的信号完整性参数。

9、根据本申请第二方面,还提供了一种信号完整性检测装置,所述装置包括:第一获得模块,用于获得待测电路板的传输线的第一参数,所述第一参数用于表征所述传输线的信号传输特征;第二获得模块,用于获得所述待测电路板的多个回路的第二参数,所述第二参数用于表征两个相邻回路之间的互容效应或互感效应;序列构建模块,用于构建所述待测电路板的源同步数据传输系统的时间序列关系;模型构建模块,用于构建所述待测电路板的多个所述回路的输出信号的特征模型;检测模块,用于根据所述第一参数、所述第二参数、所述时间序列关系和所述特征模型,确定所述待测电路板的多个数据通道的信号完整性。

10、根据本申请第三方面,又提供了一种计算机可读存储介质,所述存储介质包括一组计算机可执行指令,当所述指令被执行时用于执行上述信号完整性检测方法。

11、根据本申请第四方面,又提供了一种设备,所述设备包括至少一个处理器、以及与所述处理器连接的至少一个存储器、总线;其中,所述处理器、所述存储器通过所述总线完成相互间的通信;所述处理器用于调用所述存储器中的程序指令,以执行上述信号完整性检测方法。

12、本申请实施例提供的信号完整性检测方法、装置、电子设备及存储介质中,信号完整性检测方法包括:获得待测电路板的传输线的第一参数,所述第一参数用于表征所述传输线的信号传输特征;获得所述待测电路板的多个回路的第二参数,所述第二参数用于表征两个相邻回路之间的互容效应或互感效应;构建所述待测电路板的源同步数据传输系统的时间序列关系;构建所述待测电路板的多个所述回路的输出信号的特征模型;根据所述第一参数、所述第二参数、所述时间序列关系和所述特征模型,确定所述待测电路板的多个数据通道的信号完整性。由此,在分析数据信号和高速信号传输时序要求的基础上,通过采集传输线自身信号传输特征的参数以及相邻回路之间互感互容效应的参数,仿真得到pcb板信号完整性的检测结果,显著缩短检测时间,有效保证检测的完整性和有效性。

13、需要理解的是,本申请的教导并不需要实现上面所述的全部有益效果,而是特定的技术方案可以实现特定的技术效果,并且本申请的其他实施方式还能够实现上面未提到的有益效果。

技术特征:

1.一种信号完整性检测方法,其特征在于,所述方法包括:

2.根据权利要求1所述的方法,其特征在于,所述第一参数为定向阻抗;相应的,所述获得待测电路板的传输线的第一参数,包括:

3.根据权利要求1所述的方法,其特征在于,所述第二参数包括电流逆差;相应的,所述获得所述待测电路板的多个回路的第二参数,包括:

4.根据权利要求1所述的方法,其特征在于,所述第二参数还包括电压逆差;相应的,所述获得所述待测电路板的多个回路的第二参数,包括:

5.根据权利要求1所述的方法,其特征在于,所述构建所述待测电路板的源同步数据传输系统的时间序列关系,包括:

6.根据权利要求1所述的方法,其特征在于,所述构建所述待测电路板的多个所述回路的输出信号的特征模型,包括:

7.根据权利要求1所述的方法,其特征在于,所述根据所述第一参数、所述第二参数、所述时间序列关系和所述特征模型,确定所述待测电路板的多个数据通道的信号完整性,包括:

8.一种信号完整性检测装置,其特征在于,所述装置包括:

9.一种计算机可读存储介质,其特征在于,所述存储介质包括一组计算机可执行指令,当所述指令被执行时用于执行权利要求1-7中任一项所述的信号完整性检测方法。

10.一种设备,所述设备包括至少一个处理器、以及与所述处理器连接的至少一个存储器、总线;其中,所述处理器、所述存储器通过所述总线完成相互间的通信;所述处理器用于调用所述存储器中的程序指令,以执行权利要求1-7中任一项所述的信号完整性检测方法。

技术总结

本申请公开了一种信号完整性检测方法、装置、电子设备及存储介质,该方法包括:获得待测电路板的传输线用于表征传输线的信号传输特征的第一参数;获得待测电路板的多个回路用于表征两个相邻回路之间的互容效应或互感效应的第二参数;构建待测电路板的源同步数据传输系统的时间序列关系;构建待测电路板的多个回路的输出信号的特征模型;根据第一参数、第二参数、时间序列关系和特征模型,确定待测电路板的多个数据通道的信号完整性。由此,通过采集传输线自身信号传输特征的参数以及相邻回路之间互感互容效应参数,仿真得到PCB板信号完整性检测结果,显著缩短检测时间,有效保证检测的完整性和有效性。

技术研发人员:王占营,唐宝玲,程亮

受保护的技术使用者:合肥联宝信息技术有限公司

技术研发日:

技术公布日:2024/3/11

- 还没有人留言评论。精彩留言会获得点赞!