一种多台测试仪器时钟同步装置及方法与流程

本发明属于测试仪器,特别是涉及一种多台测试仪器时钟同步装置及方法。

背景技术:

1、对于像航空发动机高空模拟试验这类大型测试试验而言,需要测试的信号种类和通道很多、关联性很强。这就要求多个测试仪器能够同时启动采集,且基于同一个共同的时间基准采集,同时要求采集数据具有时间属性,方便事后处理时将数据对齐。即要求系统里不同设备的采集时钟要同步。

2、ieee1588协议,又称ptp(precise time protocol--精准时间协议),是一种高精度网络时间同步协议。该协议具有可扩展性强、成本低、网络化等特点,非常适合于多台测试仪器的时间同步。然而现有技术解决方案只能在时钟同步周期(通常为1秒)时刻进行调整,同步周期内无法进行调整。这样由于本地时钟频率偏差导致的误差会在一个周期内不断累积,造成较大的同步误差。

3、因此针对上述问题,迫切需要设计一种本地实时时钟调整装置和方法来减小ieee1588协议同步周期内的时钟误差,达到更高的同步精度,以满足实际使用的需要。

技术实现思路

1、为了解决上述问题,本发明提出了一种多台测试仪器时钟同步装置及方法,解决现有测试设备无法实现采集时钟同步的技术问题。

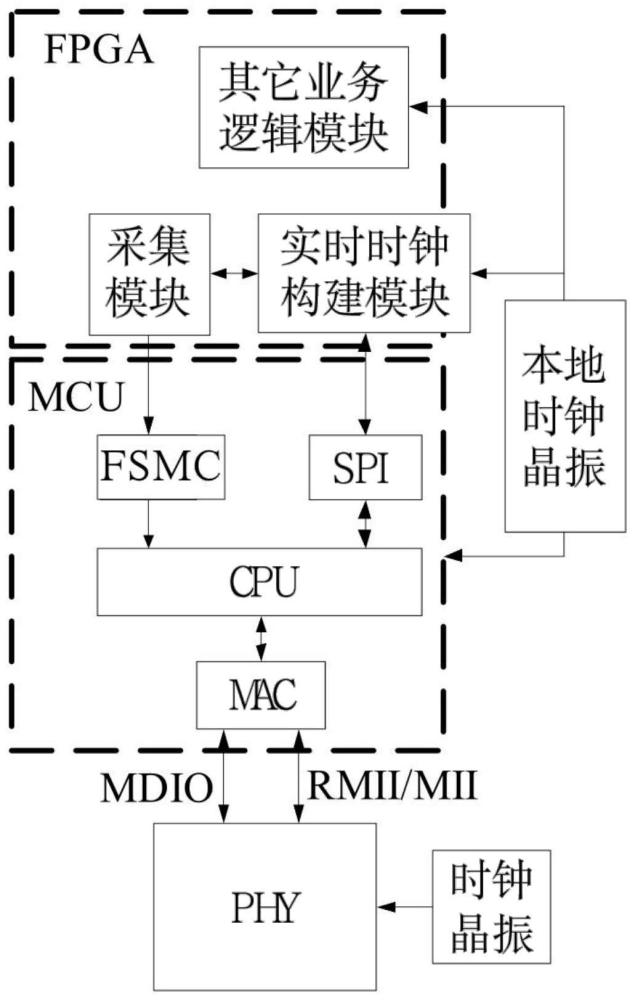

2、为达到上述目的,本发明采用的技术方案是:一种多台测试仪器时钟同步装置,以太网物理层控制phy模块、微控制器mcu模块、现场可编程逻辑门阵列fpga模块、时钟晶振模块和本地时钟晶振模块;

3、所述以太网物理层控制phy模块,通过管理数据输入输出mdio接口和媒体独立接口与微控制器mcu模块相连,通过时钟输入接口与时钟晶振模块输出相连;

4、所述微控制器mcu模块,通过静态存储控制器fsmc接口和串行外设接口spi与现场可编程逻辑门阵列fpga模块相连,通过时钟输入接口与本地时钟晶振模块输出相连;所述现场可编程逻辑门阵列fpga模块的时钟输入接口与本地时钟晶振模块输出相连。

5、进一步的是,所述微控制器mcu模块包括:

6、介质访问控制层mac子模块,用于通过管理数据输入输出接口mdio接口配置和读取以太网物理层控制phy模块的寄存器,通过媒体独立rmii/mii接口读取和发送以太网消息和业务数据,并将业务数据转换成通用的8bit数据供cpu子模块使用;

7、spi子模块,用于配置和读取现场可编程逻辑门阵列fpga模块中的寄存器;

8、fsmc子模块,用于读取现场可编程逻辑门阵列fpga模块中的采集数据;

9、和cpu子模块,用于运行ieee1588协议栈,根据接收到的时间戳计算得到与主时钟的时间偏移、频率偏移和相位偏移,并将所有偏移通过spi子模块写入现场可编程逻辑门阵列fpga模块中;用于通过fsmc子模块读取现场可编程逻辑门阵列fpga模块中的采集数据,根据业务需求进行相应计算,并将其通过mac子模块发送到以太网中。

10、进一步的是,所述现场可编程逻辑门阵列fpga模块包括:

11、采集子模块,用于根据实时时钟构建子模块生成的采集时钟采集数据,并存入缓冲区中,供微控制器mcu模块读取;

12、实时时钟构建子模块,根据微控制器mcu模块发送的本地时钟与主时钟的时间偏移量、频率偏移量和相位偏移量对本地时钟晶振产生的未同步时钟进行同步,生成所需要的经过同步的高精度采集时钟;

13、和业务逻辑模块,用于现场可编程逻辑门阵列fpga模块的程序配置、在线调试,业务逻辑使用非同步时钟。

14、进一步的是,所述实时时钟构建子模块包括:直接频率写入寄存器、临时频率写入寄存器、直接时间写入亚秒寄存器、直接时间写入秒寄存器、频率调整寄存器、δ-σ调制器、亚秒累加器和秒累加器;

15、所述直接频率写入寄存器和临时频率写入寄存器的值是微控制器mcu模块通过spi子模块将计算得到的与主时钟的频率偏差和相位偏差写入修改的;临时频率写入寄存器用来实现相位临时调整,一般情况下该寄存器为0,当临时调整值写入该寄存器后,直接频率写入寄存器会加或减上这个调整值再送入频率调整寄存器,然后临时频率写入寄存器会自动清0;

16、频率调整寄存器经过δ-σ调制器转变成亚秒累加器所需要的位宽后送入亚秒累加器进行累加;亚秒累加器累加溢出后秒累加器加1,从而实现时间的不断计数;

17、所述直接时间写入亚秒寄存器和直接时间写入秒寄存器实现直接写时间功能,即微控制器mcu模块通过spi子模块将计算得到的与主时钟的时间偏差写入这两个寄存器,秒以上的部分写入直接时间写入秒寄存器,秒以下的部分写入直接时间写入亚秒寄存器;这两个寄存器的值在直接时间写入功能有效后的第一个时钟周期自动加载到亚秒累加器和秒累加器中;

18、所述亚秒累加器和秒累加器的值输出作为本地时钟的时间;当亚秒累加器累加到指定值时溢出生成需要的采样时钟。

19、另一方面,本发明还提供了一种多台测试仪器时钟同步方法,包括步骤:

20、步骤1:从太网物理层控制模块中获取精准时间协议事件消息的时间戳信息;

21、步骤2:根据获得的时间戳信息,计算本地时钟的时间偏移量、频率偏移量和相位偏移量,并将这些偏移量写入实时时钟构建子模块的相应寄存器中;

22、步骤3:实时时钟构建子模块根据写入的时间偏移量、相位偏移量和频率偏移量,调整本地时钟的时间、相位和频率;

23、步骤4:将调整好的本地时钟发送给多台测试仪器完成多台测试仪器时钟同步。

24、进一步的是,在所述步骤3中,实时时钟构建子模块根据写入的时间偏移量、相位偏移量和频率偏移量调整本地时钟的时间、相位和频率,包括步骤:

25、步骤3.1:在同步的最初若干次时,直接将精准时间协议报文中与主时钟的时间偏差值写入直接时间写入亚秒寄存器和直接时间写入秒寄存器,完成本地时钟的时间偏差调整;

26、步骤3.2:在接下来的若干次调整中,将计算出的时钟频率偏移量写入直接频率写入寄存器,并使能固定频率调整功能,完成本地时钟的频率偏差调整;直接频率写入寄存器由纳秒部分和纳秒的小数部分组成,通过改变直接频率写入寄存器的值来控制输出信号的分频比,从而达到频率补偿的效果,使本地频率同步于主钟频率;

27、步骤3.3:在本地时钟的频率与主时钟的频率基本一致后,将计算出的时钟相位偏移量写入临时频率调整寄存器,并使能临时频率调整功能;此时,本地时钟在固定频率调整值的基础上加上或减去临时频率调整值,在使能临时频率调整功能后的第一个时钟周期调整一次,调整结束后本地时钟的频率自动恢复固定频率调整值,完成本地时钟的相位偏差调整;

28、步骤3.4:重复步骤3.2和3.3直至同步精度小于设定的同步误差门限值。

29、进一步的是,还包括步骤3.5:实时时钟构建子模块根据设定的采集时钟频率生成经过同步的高精度采集时钟。

30、进一步的是,时间偏移量计算包括步骤:

31、步骤2.1.1:主时钟定期向从时钟发送同步报文sync,记下它发出的准确时刻t0,并将时标t0装入跟随报文follow_up发送给从时钟;

32、步骤2.1.2:从时钟接收到sync报文时立刻把当前时刻t1记下来;

33、步骤2.1.3:从时钟接收到follow_up报文后,提取其中的时标t0,并利用以下公式来估计出时间偏移量toffset:

34、toffset=t1-t0+delay1;

35、其中,delay1为该过程中主时钟到从时钟的线路延时误差;

36、步骤2.1.4:将所述时间偏移量加上当前本地时间,组成调整后的本地时间,并将该时间分解成整秒时间和纳秒时间,整秒时间即为直接时间写入秒寄存器值;将纳秒时间扩展出若干小数部分位得到直接时间写入亚秒寄存器值。

37、进一步的是,频率偏移量计算包括步骤:

38、步骤2.2.1:在每发送完两组sync报文和follow_up报文后,得到sync报文的发出时刻和sync报文的接收时间和其中k为正整数;估算出从时钟的时钟频率漂移为:

39、

40、步骤2.2.2:变换不同的k值得出多个driftk值,然后再取平均值作为最终的drift值:

41、

42、步骤2.2.3:将drift值扩展出若干小数部分位得到直接频率写入寄存器值。

43、进一步的是,相位偏移量计算包括步骤:

44、步骤2.3.1:从时钟向主时钟发送一个延时请求报文delay_req,并记录报文发出的时刻t2;

45、步骤2.3.2:主时钟在接收到delay_req报文的时刻立即打上时标t3,并将时标t3装入延时响应报文delay_resp送给从时钟;

46、步骤2.3.3:从时钟接收到delay_resp报文后,提取其中的时标t3,并利用下列公式计算出相位偏移量poffset:

47、

48、步骤2.3.4:将相位偏移量poffset扩展出若干小数部分位得到临时频率调整寄存器值。

49、采用本技术方案的有益效果:

50、本发明提供了一种多台测试仪器时钟同步装置及方法,主从时钟间通过交换ptp报文,计算出本地时钟的时间偏移、频率偏移和相位偏移,根据计算出的偏移量调整本地时钟。相较于现有技术只能在时钟同步周期时刻进行时间调整和相位调整的方式,本发明增加了频率调整,即将一个调整周期内积累的频率误差分摊到每个本地时钟周期进行调整,实现与主时钟同频同相,可达到更快的时钟收敛速度和更高的同步精度。除此之外,可以在本发明的基础上,通过修改亚秒累加器的溢出频率,生成用户需要的经过同步的采样时钟,供采样使用。本发明能够实现多台测试仪器的有效时钟同步。

- 还没有人留言评论。精彩留言会获得点赞!