一种高精度时间戳的获取方法、系统、设备及存储介质与流程

本发明的实施方式涉及计算机系统领域,更具体地,本发明的实施方式涉及一种高精度时间戳的获取方法、系统、设备及存储介质。

背景技术:

1、本部分旨在为权利要求书中陈述的本发明的实施方式提供背景或上下文。此处的描述不因为包括在本部分中就承认是现有技术。

2、时延是网络测试的重要参数,而时间戳(timestamp)机制是时间同步和时延测试的关键要素之一。图1显示了时延测试的一个常见实例流程。发送方和接收方均采用400m时钟产生时间戳,对应2.5ns的时戳精度,而fpga的网络包发送逻辑运行在350mhz,所以为了处理跨时钟域的问题,400m的时钟所产生的时戳会经过一个异步fifo,再被350m的发送逻辑使用。每个网络包被发送的时候,取出相应的时戳,内嵌到网络包当中,在接收端,接收逻辑取出发送时刻的时戳t1,再得到包接收时刻的时间t2,通过t2-t1即可得到网络包的延迟。很明显,时延测试的精度取决于时间戳的精度。

3、随着5g时代的到来和更高速率的以太网技术出现,比如400ge/800ge网络技术,对时间戳的精度的要求越来越高。5g通信设备对网元间的时间同步偏差的要求是5ns。而800ge发送一个64字节的网络帧所需的时间为0.84ns,理论上需要小于0.84ns的时间戳才能区分出两个不同网络包的时延差异。

4、提高时间戳精度的常用方法,有以下三种:

5、一是提高产生时间戳所用的时钟的频率,比如对于1000m网络,采用125m的时钟产生时间戳,对应8ns的精度;当网速来到了100g时,普遍采用400m的时钟产生时间戳,对应2.5ns的时戳精度。目前在采用硬件精确测试时延的实现方案中,fpga是一类重要的器件。fpga由于自身的工艺和器件特点,内部逻辑的运行频率相比cpu要低很多,要实现500mhz以上的时钟就非常困难或者不可能了,而当我们要实现小于1ns的时间戳,对应1ghz的时钟,这种方法在fpga的场景下直接实现不可行。

6、第二种方法是多相位采样,在专利文件cn112953669中提到“本发明公开了一种提高时间戳精度的方法及系统,涉及时间同步领域,该方法包括将秒脉冲信号或otn业务处理芯片输出的帧定位标识信号发送至fpga的lvds serdes接口;通过lvds serdes接口得到帧定位标识信号的上升沿位置,同时生成一个实时时间采样指示信号,并取当前的实时时间作为初始时间戳t;基于实时时间采样指示信号对应的非零采样值,生成采样误差补偿值△t1;基于统计结果得到当前的过采样状态,且不同的过采样状态对应不同的过采样误差补偿值△t2,则最终的时间戳等于初始时间戳t、采样误差补偿值△t1和过采样误差补偿值△t2三者之和。本发明实施简单,对fpga器件的时序要求较低。,该方法在fpga中由于时钟和数据的走线不易精确控制,导致误差很大,具体实施效果不理想。多相位采样,如果没有巧妙的机制,确实会存在数据和时钟的走线不易控制,出现采样错误等问题,而该申请中提到的补偿法,其实不能直接地提高时间戳精度,只是减小了时间戳的误差值。

技术实现思路

1、在本上下文中,本发明的实施方式期望提供一种高精度时间戳的获取方法、系统、设备及存储介质。

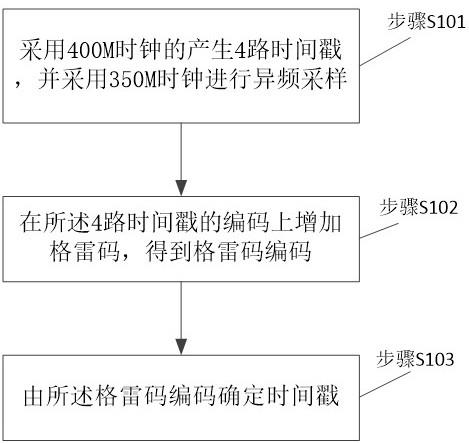

2、在本发明实施方式的第一方面中,提供了一种高精度时间戳的获取方法,包括:

3、采用400m时钟的产生4路时间戳,并采用350m时钟进行异频采样;

4、在所述4路时间戳的编码上增加格雷码,得到格雷码编码;

5、由所述格雷码编码确定时间戳。

6、在本实施方式的一个实施例中,所述采用400m时钟的产生4路时间戳,包括:

7、通过fpga的锁相环pll产生出400m时钟的4个不同相位的基准时钟,相位分别偏差0度、90度、180度和270度;

8、四路基准时钟分别驱动四个二进制计数器,产生四路时间戳,每路时间戳的分辨率为2.5ns,相位也相应相差0度、90度、180度和270度。

9、在本实施方式的一个实施例中,所述在所述4路时间戳的编码上增加格雷码,得到格雷码编码,包括:

10、在所述4路时间戳的编码上均增加一个格雷码,得到4路时间戳对应的格雷码编码。

11、在本实施方式的一个实施例中,所述由所述格雷码编码确定时间戳,包括:

12、由四路格雷码编码确定当前时间戳对应的格雷码编码;

13、由所述格雷码编码转换为当前时间戳。

14、在本实施方式的一个实施例中,所述由四路格雷码编码确定当前时间戳对应的格雷码编码,包括:

15、当四路格雷码编码为n’,n-1’,n-1’,n-1’时,当前的时间戳为(n-1’);

16、当四路格雷码编码为n’,n’,n-1’,n-1’,那么当前的时间戳为(n-1’+1/4);

17、当四路格雷码编码为n’,n’,n’,n-1’,那么当前的时间戳为(n-1’+1/2);

18、当四路格雷码编码为n’,n’,n’,n’,那么当前的时间戳为(n-1’+3/4)。

19、在本发明实施方式的第二方面中,提供了一种高精度时间戳的获取系统,包括:

20、采样模块,用于采用400m时钟的产生4路时间戳,并采用350m时钟进行异频采样;

21、修正模块,用于在所述4路时间戳的编码上增加格雷码,得到格雷码编码;

22、时间戳确定模块,用于由所述格雷码编码确定时间戳。

23、在本实施方式的一个实施例中,所述采样模块中的采用400m时钟的产生4路时间戳,具体实现步骤包括:

24、通过fpga的锁相环pll产生出400m时钟的4个不同相位的基准时钟,相位分别偏差0度、90度、180度和270度;

25、四路基准时钟分别驱动四个二进制计数器,产生四路时间戳,每路时间戳的分辨率为2.5ns,相位也相应相差0度、90度、180度和270度。

26、在本实施方式的一个实施例中,修正模块具体用于:

27、在所述4路时间戳的编码上均增加一个格雷码,得到4路时间戳对应的格雷码编码。

28、在本实施方式的一个实施例中,时间戳确定模块包括:

29、初步确定子模块,用于由四路格雷码编码确定当前时间戳对应的格雷码编码;

30、转换子模块,用于由所述格雷码编码转换为当前时间戳。

31、在本实施方式的一个实施例中,初步确定子模块具体用于:

32、当四路格雷码编码为n’,n-1’,n-1’,n-1’时,当前的时间戳为(n-1’);

33、当四路格雷码编码为n’,n’,n-1’,n-1’,那么当前的时间戳为(n-1’+1/4);

34、当四路格雷码编码为n’,n’,n’,n-1’,那么当前的时间戳为(n-1’+1/2);

35、当四路格雷码编码为n’,n’,n’,n’,那么当前的时间戳为(n-1’+3/4)。

36、在本发明实施方式的第三方面中,提供了一种计算设备,所述计算设备包括:至少一个处理器、存储器和输入输出单元;其中,所述存储器用于存储计算机程序,所述处理器用于调用所述存储器中存储的计算机程序来执行第一方面中任一项所述的方法。

37、在本发明实施方式的第四方面中,提供了一种计算机可读存储介质,其包括指令,当其在计算机上运行时,使得计算机执行第一方面中任一项所述的方法。

38、根据本发明实施方式的一种高精度时间戳的获取方法、系统、设备及存储介质,在用fpga实现高精度时戳的应用场景下,基于多相位采样的想法,通过增加异频多相位采样、格雷时间戳编码、采样数据校正等多种新方法,实现低于1ns的时间戳精度,将目前普遍采用的2.5ns时间戳精度提高4倍或者更多。

- 还没有人留言评论。精彩留言会获得点赞!