一种针对硬件链路的通用型JTAG下载系统以及方法与流程

本发明属于集成电路设计领域,尤其涉及一种针对硬件链路的通用型jtag下载系统以及方法。

背景技术:

1、现场可编程门阵列(field programmable gate array,fpga)作为专用集成电路(asic)领域中的一种半定制电路而出现,既解决了定制电路功能固定的不足,又克服了原有可编程器件门电路数有限的缺点。fpga的逻辑功能按照用户对器件编程来确定,集成度很高。随着fpga技术的发展,fpga市场已经涉及到通信、工业控制、机器人、图像处理及消费类电子等各个领域。

2、fpga下载器将码流下载到fpga芯片进行配置时,下载器的通用性显得至关重要。下载器将码流下载到不同型号的器件时,由于不同型号的器件支持不同的烧写方式,因此下载器需要针对不同型号的器件采用不同的下载方式。

3、prom(programmable read-only memory)类型器件也十分常见,往往与fpga器件配合使用。下载器将码流存储于prom中,从而对fpga直接进行配置。不同型号对应不同存储方式,同时存储模式分为串行和并行两种,因此下载器的通用性显得十分重要。

技术实现思路

1、本发明解决的技术问题是:克服现有技术的不足,提供一种针对硬件链路的通用型jtag下载系统以及方法,能够适用于多型号、多参数调节、多下载方式,而且下载速度更快、下载器结构更简单。

2、本发明解决技术的方案是:一种针对硬件链路的通用型jtag下载系统,所述硬件链路包含n个待下载目标芯片,n大于等于1,该系统包括下载器和上位机;

3、上位机,根据接口配置文件配置下载器;向下载器发送扫描指令;根据收到的idcode信息,索引待下载目标芯片的名称、器件类型;根据待下载目标芯片的个数及器件类型,自动化生成目标芯片配置文件和下载函数;根据目标芯片配置文件配置待下载目标芯片,调用下载函数将待下载目标芯片的码流传输至下载器;所述接口配置文件用于配置下载器的属性,包括:下载器类型、数据传输速度、数据传输协议;所述目标芯片的配置文件包括目标芯片的器件类型、型号、个数、指令寄存器的长度;

4、下载器,收到扫描指令后,扫描待下载硬件链路,获得待下载目标芯片的个数及每个待下载目标芯片对应的idcode,反馈给上位机;将待下载目标芯片的码流转换为jtag形式,通过jtag接口传输至待下载目标芯片。

5、优选地,所述上位机发出扫描指令或者码流传输完成后,向下载器发送获取状态寄存器指令;

6、下载器,执行获取状态寄存器指令,以获得每个待下载目标芯片对应的状态寄存器的数值,反馈给上位机;

7、上位机,解析下载目标芯片对应的状态寄存器的数值并将其显示在界面上。

8、优选地,所述下载器包括type-c接口模块、jtag电缆、协议转换模块、usb-typec电缆;

9、usb-typec电缆的usb端连接上位机,typec端连接type-c接口模块;

10、type-c接口模块,用于上位机与协议转换模块之间实现usb协议数据传输;

11、协议转换模块,收到扫描指令后,扫描待下载硬件链路,获得待下载目标芯片的个数及每个待下载目标芯片对应的idcode,通过type-c接口模块反馈给上位机;将待下载目标芯片的码流转换为jtag形式,通过jtag电缆传输至待下载目标芯片。

12、优选地,所述协议转换模块由ftdi芯片实现。

13、优选地,当待下载目标芯片的器件类型为fpga型器件时,下载函数执行如下步骤:

14、往fpga器件的cfg_in指令寄存器写入第一预设固定值,之后,向cfg_in指令寄存器对应的数据寄存器中注入码流的二进制数据,直至码流注入完成。

15、优选地,当待下载目标芯片的器件类型为prom型器件时,下载函数执行如下步骤:

16、s1、向isc_enable指令寄存器写入第二预设固定值,使能prom型器件下载功能;

17、s2、向isc_address_shift寄存器写入下载地址;

18、s3、再向isc_data_shift寄存器注入一段码流,prom自动从isc_data_shift寄存器将码流搬移到以下载地址为首的一段存储空间;

19、s4、重复执行步骤s2~步骤s3,直至注入全部码流;

20、s5、向xsc_data_ccb寄存器写入第三预设值,所述第三预设值表示向cfg_in指令寄存器对应的数据寄存器中注入码流的模式;

21、s6、向isc_disable寄存器写入第四预设固定值,关闭prom型器件下载功能,烧写完毕。

22、优选地,待下载目标芯片的码流传输完成后,上位机还发送回读指令至下载器;下载器通过jtag接口回读目标芯片上的码流,反馈至上位机以文件形式保存。

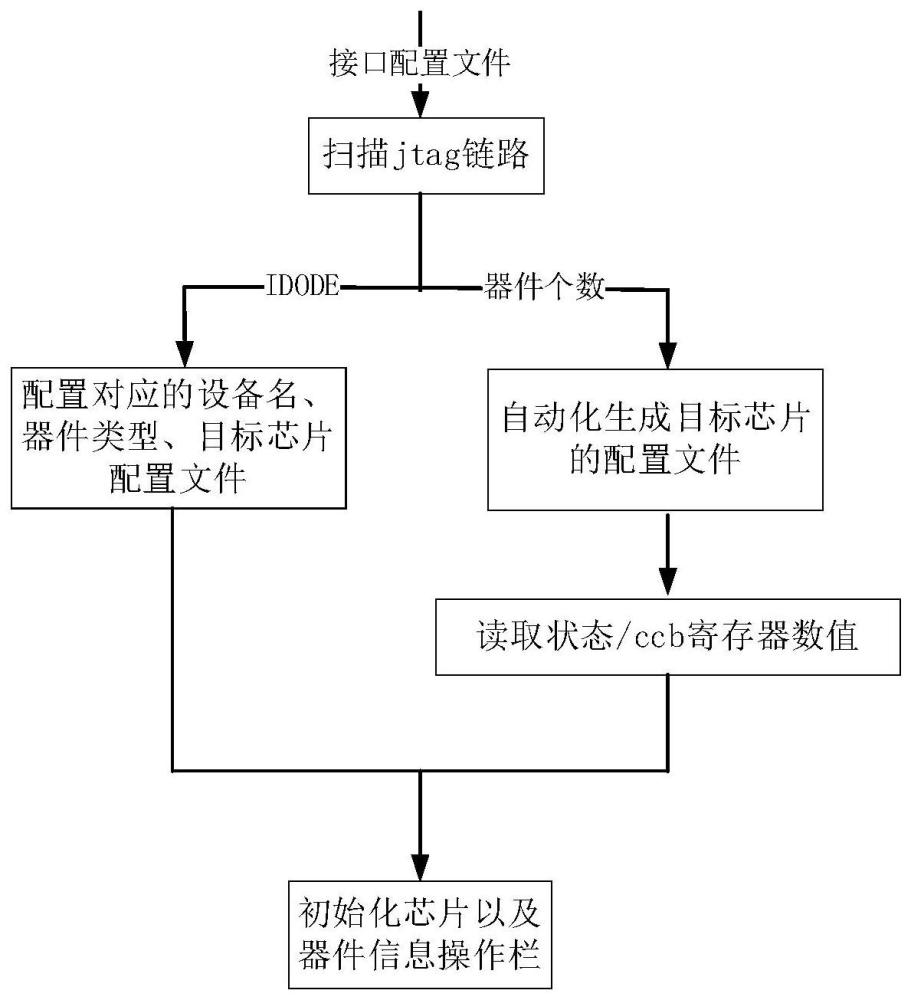

23、本发明的另一个技术方案是:一种针对硬件链路的通用型jtag下载方法,该方法包括如下步骤:

24、根据接口配置文件配置下载器;所述接口配置文件用于配置下载器的属性,包括:下载器类型、数据传输速度、数据传输协议;

25、向下载器发送扫描指令,控制下载器扫描待下载硬件链路,获得待下载目标芯片的个数及每个待下载目标芯片对应的idcode;

26、根据待下载目标芯片的idcode信息,索引待下载目标芯片的名称、器件类型;

27、根据待下载目标芯片的个数及器件类型,自动化生成目标芯片配置文件和下载函数;所述目标芯片的配置文件包括目标芯片的器件类型、型号、个数、指令寄存器的长度;

28、根据目标芯片配置文件配置待下载目标芯片,调用下载函数将待下载目标芯片的码流传输至下载器,由将待下载目标芯片的码流转换为jtag形式,通过jtag接口传输至待下载目标芯片。

29、优选地,当待下载目标芯片的器件类型为fpga型器件时,下载函数执行如下步骤:

30、往fpga器件的cfg_in指令寄存器写入第一预设固定值,之后,向cfg_in指令寄存器对应的数据寄存器中注入码流的二进制数据,直至码流注入完成。

31、优选地,当待下载目标芯片的器件类型为prom型器件时,下载函数执行如下步骤:

32、s1、向isc_enable指令寄存器写入第二预设固定值,使能prom型器件下载功能;

33、s2、向isc_address_shift寄存器写入下载地址;

34、s3、再向isc_data_shift寄存器注入一段码流,prom自动从isc_data_shift寄存器将码流搬移到以下载地址为首的一段存储空间;

35、s4、重复执行步骤s2~步骤s3,直至注入全部码流;

36、s5、向xsc_data_ccb寄存器写入第三预设值,0xffff表示串行模式写入,0xfff9表示并行模式写入;

37、s6、向isc_disable寄存器写入第四预设固定值,关闭prom型器件下载功能,烧写完毕。

38、本发明与现有技术相比的有益效果是:

39、(1)、本发明通过设计接口配置文件,对多种参数设为配置可选,实现了接口类型的多样性、下载速度的可调节性;

40、(2)、本发明通过全自动扫描流程设计,实现对多种器件的信息获取和通用的器件扫描流程;

41、(3)、本发明利用idcode信息区分芯片型号以对应不同的下载方式,目前支持fpga和prom类型的芯片。

42、(4)、根据实际演示效果,本发明满足支持多器件扫描、多型号器件以及多参数调节,提升了芯片下载的通用性。

43、(5)、本发明实现了对硬件芯片的通用性下载,提升了下载器的可调节性和可扩展性。

- 还没有人留言评论。精彩留言会获得点赞!