数据传输的方法、装置、设备、系统及可读存储介质与流程

本技术实施例涉及通信,尤其涉及一种数据传输的方法、装置、设备、系统及可读存储介质。

背景技术:

1、前向纠错码(forward error correction,fec)是一种通过为被传递的数据提供校验位,提高信道中的数据传输速率以及传输距离的数据编码方法。在数据传输过程中,发送端通过特定的fec码型将原始数据进行编码,将编码后的数据发送至接收端,接收端通过相同的fec码型将接收的数据进行解码,得到原始数据。

技术实现思路

1、本技术提出一种数据传输的方法、装置、设备、系统及可读存储介质,用于对fec码型进行增强,以适配高速率和/或远距离的数据传输。

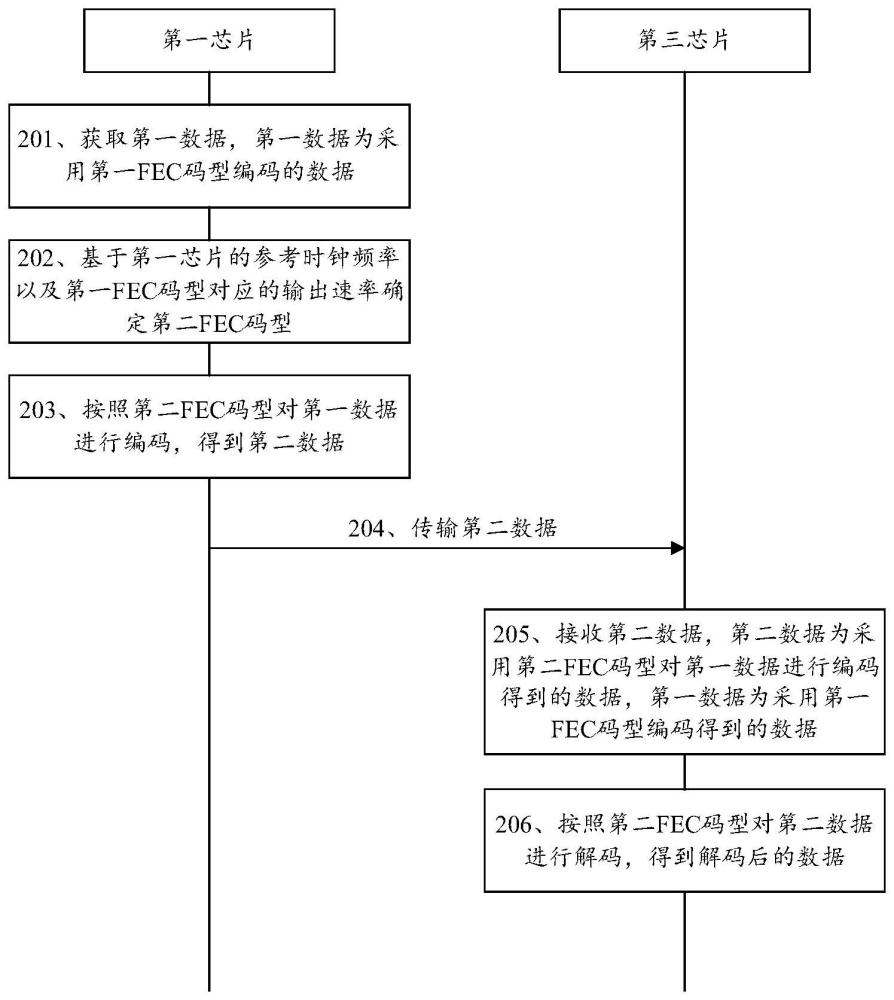

2、第一方面,提供了一种数据传输的方法,该方法包括:第一芯片获取采用第一fec码型编码的第一数据;基于第一芯片的参考时钟频率以及第一fec码型对应的输出速率确定第二fec码型;之后,该第一芯片按照第二fec码型对第一数据进行编码,得到第二数据,传输该第二数据。

3、该方法基于第一芯片的参考时钟频率以及第一fec码型对应的输出速率确定第二fec码型,将获取的采用第一fec码型编码的第一数据通过第二fec码型进行再一次编码,得到级联编码的第二数据,使该第二数据具有更高的编码增益,在容易出现误码的通道中传输时,能够对出现误码的数据进行有效的纠错,从而提高数据传输的质量。其次,由于第二数据为在第一数据的基础上直接编码获得的数据,该方法的实现过程较为简便,提高了数据传输的效率。

4、在一种可能的实现方式中,所述第一芯片的参考时钟频率、所述第一fec码型对应的输出速率与所述第二数据的码字长度以及所述第二数据的码字内信息长度满足开销比例关系;所述基于所述第一芯片的参考时钟频率以及所述第一fec码型对应的输出速率确定第二fec码型,包括:基于所述第一芯片的参考时钟频率及所述第一fec码型对应的输出速率,按照所述开销比例关系确定所述第二fec码型。通过按照开销比例关系来确定第二fec码型,可以保证采用第二fec码型编码后的开销,进一步提高了数据传输的性能。

5、在一种可能的实现方式中,所述开销比例关系,包括:

6、

7、其中,所述n为第二数据的码字长度,所述k为所述第二数据的码字内信息长度,所述v1为所述第一fec码型对应的输出速率,所述p为调整参数,所述f为所述第一芯片的参考时钟频率,所述p为正整数。

8、在一种可能的实现方式中,所述第二数据的码字长度与所述第二数据被分发时的逻辑通道数量成整数倍关系。在确定第二fec码型时,通过考虑该整数倍关系,使得确定出的第二fec码型更加适合传输场景,提高了数据传输的性能。

9、在一种可能的实现方式中,所述第一芯片按照所述第二fec码型对所述第一数据进行编码,得到第二数据,包括:所述第一芯片分发所述第一数据得到多个第一子数据,所述第一芯片按照所述第二fec码型分别对所述多个第一子数据进行编码,得到多个第二子数据;所述第一芯片传输所述第二数据,包括:所述第一芯片对所述多个第二子数据进行传输。

10、在一种可能的实现方式中,所述第一芯片分发所述第一数据得到多个第一子数据,包括:所述第一芯片通过物理编码子层pcs通道分发所述第一数据得到多个第一子数据;或者,所述第一芯片通过物理介质接入子层pma分发所述第一数据流得到多个第一子数据。

11、在一种可能的实现方式中,所述第一芯片传输所述第二数据,包括:所述第一芯片对所述第二数据进行分发,得到多个第三子数据,通过多条逻辑通道发送所述多个第三子数据。

12、在一种可能的实现方式中,所述基于所述第一芯片的参考时钟频率以及所述第一fec码型对应的输出速率确定第二fec码型之前,所述方法还包括:所述第一芯片与接收所述第一芯片发送的数据的第三芯片进行自协商;响应于自协商结果指示需要级联编码,所述第一芯片执行所述基于所述第一芯片的参考时钟频率以及所述第一fec码型对应的输出速率确定第二fec码型。通过自协商来确定是否进行级联编码,适用性更强,更加符合实际场景需求。

13、在一种可能的实现方式中,所述第一数据为所述第一芯片内部的数据,或所述第一数据为所述第一芯片接收的由第二芯片发送的数据。由于第一数据可以为第一芯片内部的数据,也可以为接收的其他芯片传输的数据,该方法应用的数据传输场景较为灵活。

14、第二方面,提供了一种数据传输的方法,该方法包括:第三芯片接收第二数据,所述第二数据为采用第二前向纠错码fec码型对第一数据进行编码得到的数据,所述第一数据为采用第一fec码型编码的数据;所述第三芯片按照所述第二fec码型对所述第二数据进行解码,得到解码后的数据。由于第二数据是对第一数据采用第二fec码型编码得到的,而第一数据又是采用第一fec码型编码得到的,因而第三芯片收到的第二数据的编码增益更高,纠错能力更高,通过对该第二数据进行解码,得到的解码后的数据的准确性更高。

15、在一种可能的实现方式中,所述第三芯片按照所述第二fec码型对所述第二数据进行解码,包括:所述第三芯片按照所述第二fec码型对所述第二数据进行软判决解码。

16、在一种可能的实现方式中,所述第三芯片按照所述第二fec码型对所述第二数据进行解码,得到解码后的数据之后,所述方法还包括:所述第三芯片按照第三fec码型对所述解码后的数据进行再次编码,传输经过再次编码后的数据。通过按照第三fec码型对解码后的数据进行再次编码,可以保护下一段链路的数据传输质量。

17、在一种可能的实现方式中,所述第三fec码型为所述第二fec码型。

18、第三方面,提供了一种数据传输的装置,所述装置包括:

19、获取模块,用于获取第一数据,所述第一数据为采用第一前向纠错码fec码型编码的数据;

20、确定模块,用于基于所述第一芯片的参考时钟频率以及所述第一fec码型对应的输出速率确定第二fec码型;

21、编码模块,用于按照所述第二fec码型对所述第一数据进行编码,得到第二数据;

22、传输模块,用于传输所述第二数据。

23、在一种可能的实现方式中,所述第一芯片的参考时钟频率、所述第一fec码型对应的输出速率与所述第二数据的码字长度以及所述第二数据的码字内信息长度满足开销比例关系;所述确定模块,用于基于所述第一芯片的参考时钟频率及所述第一fec码型对应的输出速率,按照所述开销比例关系确定所述第二fec码型。

24、在一种可能的实现方式中,所述开销比例关系,包括:

25、

26、其中,所述n为第二数据的码字长度,所述k为所述第二数据的码字内信息长度,所述v1为所述第一fec码型对应的输出速率,所述p为调整参数,所述f为所述第一芯片的参考时钟频率,所述p为正整数。

27、在一种可能的实现方式中,所述第二数据的码字长度与所述第二数据被分发时的逻辑通道数量成整数倍关系。

28、在一种可能的实现方式中,所述编码模块,用于分发所述第一数据得到多个第一子数据,按照所述第二fec码型分别对所述多个第一子数据进行编码,得到多个第二子数据;所述传输模块,用于对所述多个第二子数据进行传输。

29、在一种可能的实现方式中,所述编码模块,用于通过物理编码子层pcs通道分发所述第一数据得到多个第一子数据;或者,通过物理介质接入子层pma分发所述第一数据流得到多个第一子数据。

30、在一种可能的实现方式中,所述传输模块,用于对所述第二数据进行分发,得到多个第三子数据,通过多条逻辑通道发送所述多个第三子数据。

31、在一种可能的实现方式中,所述装置还包括:自协商模块,用于与接收所述第一芯片发送的数据的第三芯片进行自协商;响应于自协商结果指示需要级联编码,所述确定模块执行所述基于所述第一芯片的参考时钟频率以及所述第一fec码型对应的输出速率确定第二fec码型。

32、在一种可能的实现方式中,所述第一数据为所述第一芯片内部的数据,或所述第一数据为所述第一芯片接收的由第二芯片发送的数据。

33、第四方面,提供了一种数据传输的装置,所述装置包括:

34、接收模块,用于接收第二数据,所述第二数据为采用第二前向纠错码fec码型对第一数据进行编码得到的数据,所述第一数据为采用第一fec码型编码的数据;

35、解码模块,用于按照所述第二fec码型对所述第二数据进行解码,得到解码后的数据。

36、在一种可能的实现方式中,所述解码模块,用于按照所述第二fec码型对所述第二数据进行软判决解码,得到解码后的数据。

37、在一种可能的实现方式中,所述装置还包括:编码模块,用于按照第三fec码型对所述解码后的数据进行再次编码;传输模块,用于传输经过再次编码后的数据。

38、在一种可能的实现方式中,所述第三fec码型为所述第二fec码型。

39、第五方面,提供了一种数据传输的设备,该设备包括:处理器,处理器与存储器耦合,存储器中存储有至少一条程序指令或代码,至少一条程序指令或代码由处理器加载并执行,以使设备实现如第一方面或第二方面中任一的数据传输的方法。

40、第六方面,提供了一种数据传输的系统,该系统包括:第一数据传输的设备,用于执行上述第一方面或第一方面任一所述的方法,第二数据传输的设备,用于执行上述第二方面或第二方面任一所述的方法。

41、第七方面,提供了一种计算机可读存储介质,该计算机可读存储介质中存储有至少一条程序指令或代码,程序指令或代码由处理器加载并执行时以使计算机实现如第一方面或第二方面中任一的数据传输的方法。

42、提供了另一种通信装置,该装置包括:通信接口、存储器和处理器。其中,该存储器和该处理器通过内部连接通路互相通信,该存储器用于存储指令,该处理器用于执行该存储器存储的指令,以控制通信接口接收数据,并控制通信接口发送数据,并且当该处理器执行该存储器存储的指令时,使得该处理器执行第一方面或第一方面的任一种可能的实施方式中的方法,或者执行第二方面或第二方面的任一种可能的实施方式中的方法。

43、作为一种示例性实施例,所述处理器为一个或多个,所述存储器为一个或多个。

44、作为一种示例性实施例,所述存储器可以与所述处理器集成在一起,或者所述存储器与处理器分离设置。

45、在具体实现过程中,存储器可以为非瞬时性(non-transitory)存储器,例如只读存储器(read only memory,rom),其可以与处理器集成在同一块芯片上,也可以分别设置在不同的芯片上,本技术实施例对存储器的类型以及存储器与处理器的设置方式不做限定。

46、提供了一种计算机程序(产品),所述计算机程序(产品)包括:计算机程序代码,当所述计算机程序代码被计算机运行时,使得所述计算机执行上述各方面中的方法。

47、提供了一种芯片,包括处理器,用于从存储器中调用并运行所述存储器中存储的指令,使得安装有所述芯片的设备执行上述各方面中的方法。

48、提供另一种芯片,包括:输入接口、输出接口、处理器和存储器,所述输入接口、输出接口、所述处理器以及所述存储器之间通过内部连接通路相连,所述处理器用于执行所述存储器中的代码,当所述代码被执行时,所述处理器用于执行上述各方面中的方法。

49、提供一种设备,包括上述方案中任一所述的芯片。

50、提供一种设备,包括上述方案中任一所述的第一芯片,和/或,上述方案中任一所述的第三芯片。

- 还没有人留言评论。精彩留言会获得点赞!