时间同步的方法、装置和电子设备与流程

本发明涉及通信的,尤其是涉及一种时间同步的方法、装置和电子设备。

背景技术:

1、针对于车载网络的应用场景需求,autosar规范中ethtsyn模块基于以太网的时间同步协议兼容了ieee802.1as规范中定义的gptp协议,并做了一定的调整和限制。时间同步分为时间同步(以下简称sync)和链路传输延迟(以下简称pdelay)计算两大流程。sync流程需要两帧以太网报文,pdelay计算流程需要三帧以太网报文,这两个流程分开进行。在全局时间的计算过程中会使用到sync过程的时间戳和pdelay计算流程中的pdelay值(即信号传输消耗时间,其中,全局时间=sync过程的时间戳(即主芯片进行时间同步所对应的时间)+信号传输消耗时间,该全局时间也就是从芯片同步的主芯片的时间戳对应的准确的现在的时间)。

2、但是,在实际应用中,一个显著的问题是:sync流程和pdelay计算流程的分开进行和大量的报文交互,一方面增加了网络的负荷,另一方面在sync流程发生网络拥塞时,仍然使用的是上一次的pdelay值来计算全局时间,会造成较大的误差。也就是,当主芯片发给从芯片sync报文时,这一次的pdelay值还没计算得到,所以在计算全局时间时,就只能使用上一次计算的pdelay值,导致全局时间计算错误。例如,假设sync周期为100ms,pdelay请求的周期为100ms。在某一时刻的sync流程中发生了网络拥塞。上一次成功计算的pdelay值为20ns,此时真实的pdelay值应该为100ms,但由于autosar规范中pdelay的计算流程和sync流程是分开进行的,所以在计算全局时间时,仍使用上一次的pdelay值(20ns,实际应该是100ms)参与计算,最终导致全局时间计算错误,即从芯片时间同步错误。

3、综上,如何进行准确的时间同步成为目前亟需解决的技术问题。

技术实现思路

1、有鉴于此,本发明的目的在于提供一种时间同步的方法、装置和电子设备,以缓解现有技术无法进行准确的时间同步的技术问题。

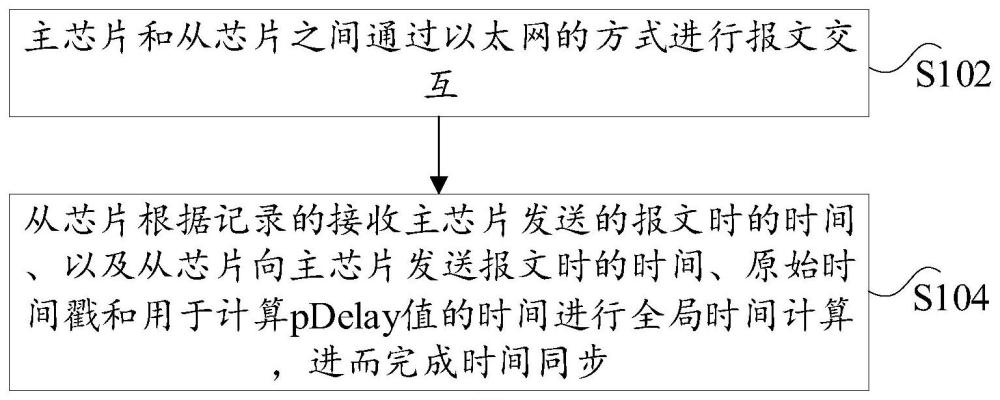

2、第一方面,本发明实施例提供了一种时间同步的方法,应用于autosar规范中的ethtsyn模块,其中,在所述autosar规范中,ethtsynmessagecompliance模式不开启,所述ethtsyn模块中的ethtsynmessageefficientmode模式开启,所述方法包括:

3、主芯片和从芯片之间通过以太网的方式进行报文交互,其中,所述主芯片向所述从芯片发送的最后一次报文中携带有原始时间戳和用于计算pdelay值的时间;

4、所述从芯片根据记录的接收所述主芯片发送的报文时的时间、以及所述从芯片向主芯片发送报文时的时间、所述原始时间戳和用于计算pdelay值的时间进行全局时间计算,进而完成时间同步。

5、进一步的,主芯片和从芯片之间通过以太网的方式进行报文交互,包括:

6、所述主芯片向所述从芯片发送sync报文,并记录发送时的第一时间,其中,所述第一时间为所述原始时间戳;

7、所述从芯片接收所述sync报文,并记录接收时的第二时间;

8、所述从芯片向所述主芯片发送sync_resp报文,并记录发送时的第三时间;

9、所述主芯片接收所述sync_resp报文,并记录接收时的第四时间;

10、所述主芯片向所述从芯片发送follow-up报文,其中,所述follow-up报文中携带有所述第一时间和所述第四时间;

11、所述从芯片接收所述follow-up报文,记录接收时的第五时间。

12、进一步的,所述从芯片根据记录的接收所述主芯片发送的报文时的时间、以及所述从芯片向主芯片发送报文时的时间、所述原始时间戳和用于计算pdelay值的时间进行全局时间计算,包括:

13、根据全局时间计算算式t=t0+t5-t1+[(t3-t0)-(t2-t1)]/2计算所述全局时间,其中,t表示所述全局时间,t0表示所述第一时间,t5表示所述第五时间,t1表示所述第二时间,t3表示所述第四时间,t2表示所述第三时间。

14、进一步的,在进行全局时间计算之后,所述方法还包括:

15、将所述全局时间作为当前时间,进而完成时间同步。

16、进一步的,在所述全局时间计算算式中,[(t3-t0)-(t2-t1)]/2表示pdelay值,t0+t5-t1表示sync时间戳。

17、第二方面,本发明实施例还提供了一种时间同步的装置,应用于autosar规范中的ethtsyn模块,其中,在所述autosar规范中,ethtsynmessagecompliance模式不开启,所述ethtsyn模块中的ethtsynmessageefficientmode模式开启,所述装置包括:

18、报文交互单元,用于主芯片和从芯片之间通过以太网的方式进行报文交互,其中,所述主芯片向所述从芯片发送的最后一次报文中携带有原始时间戳和用于计算pdelay值的时间;

19、计算单元,用于所述从芯片根据记录的接收所述主芯片发送的报文时的时间、以及所述从芯片向主芯片发送报文时的时间、所述原始时间戳和用于计算pdelay值的时间进行全局时间计算,进而完成时间同步。

20、进一步的,所述报文交互单元还用于:

21、所述主芯片向所述从芯片发送sync报文,并记录发送时的第一时间,其中,所述第一时间为所述原始时间戳;

22、所述从芯片接收所述sync报文,并记录接收时的第二时间;

23、所述从芯片向所述主芯片发送sync_resp报文,并记录发送时的第三时间;

24、所述主芯片接收所述sync_resp报文,并记录接收时的第四时间;

25、所述主芯片向所述从芯片发送follow-up报文,其中,所述follow-up报文中携带有所述第一时间和所述第四时间;

26、所述从芯片接收所述follow-up报文,记录接收时的第五时间。

27、进一步的,所述计算单元还用于:

28、根据全局时间计算算式t=t0+t5-t1+[(t3-t0)-(t2-t1)]/2计算所述全局时间,其中,t表示所述全局时间,t0表示所述第一时间,t5表示所述第五时间,t1表示所述第二时间,t3表示所述第四时间,t2表示所述第三时间。

29、第三方面,本发明实施例还提供了一种电子设备,包括存储器、处理器及存储在所述存储器上并可在所述处理器上运行的计算机程序,所述处理器执行所述计算机程序时实现上述第一方面任一项所述的方法的步骤。

30、第四方面,本发明实施例还提供了一种计算机可读存储介质,所述计算机可读存储介质存储有机器可运行指令,所述机器可运行指令在被处理器调用和运行时,所述机器可运行指令促使所述处理器运行上述第一方面任一项所述的方法。

31、在本发明实施例中,提供了一种时间同步的方法,应用于autosar规范中的ethtsyn模块,其中,在autosar规范中,ethtsynmessagecompliance模式不开启,ethtsyn模块中的ethtsynmessageefficientmode模式开启,该方法包括:主芯片和从芯片之间通过以太网的方式进行报文交互,其中,主芯片向从芯片发送的最后一次报文中携带有原始时间戳和用于计算pdelay值的时间;从芯片根据记录的接收主芯片发送的报文时的时间、以及从芯片向主芯片发送报文时的时间、原始时间戳和用于计算pdelay值的时间进行全局时间计算,进而完成时间同步。通过上述描述可知,本发明的时间同步的方法中,在主芯片和从芯片的最后一次报文交互中,携带有原始时间戳和用于计算pdelay值的时间,也就是将计算pdelay值的过程合并至时间同步的过程中了,二者是一起进行的,并非是分开进行的,也就是说,每次时间同步所使用的pdelay值都是其本次真正的pdelay值,不会因为sync流程发生网络拥塞时带来的使用上一次的pdelay值的情况发生,最终全局时间计算的准确性好,也就是能够实现准确的时间同步,缓解了现有技术无法进行准确的时间同步的技术问题。

- 还没有人留言评论。精彩留言会获得点赞!