一种信号处理电路、放大电路及射频前端模组的制作方法

本申请涉及集成电路,尤其涉及一种信号处理电路、放大电路及射频前端模组。

背景技术:

1、随着5g时代的到来,通信频段增多,通信协议越来越复杂,单个通信终端中射频前端模组数目也逐渐增多。基于这些情况,对射频前端模组(包括增益、噪声、线性、功耗、尺寸等)提出了更高的要求。

技术实现思路

1、有鉴于此,本申请实施例提供一种信号处理电路、放大电路及射频前端模组。

2、为达到上述目的,本申请的技术方案是这样实现的:

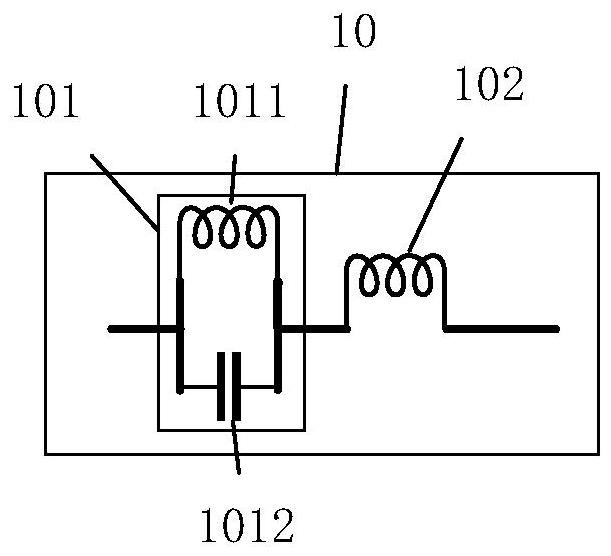

3、一方面,本申请实施例提供一种信号处理电路,包括:滤波电路,具有第一电感和与所述第一电感并联的电容,用于对接收的射频信号进行带外干扰抑制;

4、第二电感,与所述滤波电路中的所述第一电感串联,用于进行阻抗匹配,所述第二电感与所述第一电感相互耦合,耦合电感使所述第一电感和所述第二电感的等效电感值增大。

5、在上述方案中,所述第一电感和第二电感的缠绕方向相同。

6、在上述方案中,所述第二电感为可调节电感,所述第一电感与所述第二电感的所述耦合电感随所述第二电感变化,所述滤波电路的带外抑制频段不变。

7、在上述方案中,所述第二电感通过调整所述第二电感包含的连接点的连接方式进行调节。

8、在上述方案中,所述第一电感为可调电感,及/或所述电容为可调电容,

9、所述滤波电路的带外抑制频段随所述第一电感及/或所述电容变化。

10、在上述方案中,所述第一电感和所述第二电感并列设置在同一层电路印制板pcb;或,所述第一电感和第二电感层叠设置在不同层pcb上。

11、在上述方案中,所述滤波电路为多个,且每一个滤波电路具有不同的带外抑制频段。

12、另一方面,本申请实施例还提供一种放大电路,至少包括:前述任一项所述的信号处理电路;及放大器,与所述信号处理电路相连接。

13、在上述方案中,所述放大器为低噪声放大器,所述第二电感用于输入匹配。

14、又一方面,本申请实施例提供的一种射频前端模组,包括:至少包括:滤波器、输入匹配器及低噪声放大器,其中,

15、所述滤波器,与天线连接,用于对从所述天线接收的射频信号进行带外干扰,且包括第一电感和与所述第一电感并联的电容;

16、所述输入匹配器包含第二电感,用于进行输入阻抗匹配,其中,所述第二电感与所述第一电感相互耦合,耦合电感使所述第一电感和所述第二电感的等效电感值增大;

17、所述低噪声放大器,与所述第二电感连接,用于对经所述滤波器及所述输入匹配器处理后的所述射频信号进行放大及噪声抑制。

18、本申请实施例提供一种信号处理电路、放大电路及射频前端模组。其中,该信号处理电路,包括:滤波电路,具有第一电感和与所述第一电感并联的电容,用于对接收的射频信号进行带外干扰抑制;第二电感,与所述滤波电路中的所述第一电感串联,用于进行阻抗匹配,所述第二电感与所述第一电感相互耦合,耦合电感使所述第一电感和所述第二电感的等效电感值增大。在本申请实施例提供的信号处理电路工作时,第一电感和第二电感的耦合电感将第一电感和第二电感的等效电感值增大。这样设计,工作时第一电感和第二电感的等效电感值大于其真实设计电感值,可以将第一电感和第二电感设计的较小些,使得信号处理电路不仅能够满足对射频信号的处理性能且还能使得第一电感和第二电感本身的尺寸小些,以节省在信号处理电路所占据的面积。

技术特征:

1.一种信号处理电路,其特征在于,包括:

2.根据权利要求1所述的电路,其特征在于,所述第一电感和所述第二电感的缠绕方向相同。

3.根据权利要求1所述的电路,其特征在于,所述第二电感为可调节电感,所述第一电感与所述第二电感的所述耦合电感随所述第二电感变化,所述滤波电路的带外抑制频段不变。

4.根据权利要求3所述的电路,其特征在于,所述第二电感通过调整所述第二电感包含的连接点的连接方式进行调节。

5.根据权利要求1所述的电路,其特征在于,所述第一电感为可调电感,及/或所述电容为可调电容,

6.根据权利要求1或2所述的电路,其特征在于,所述第一电感和所述第二电感并列设置在同一层电路印制板pcb;或,所述第一电感和第二电感层叠设置在不同层pcb上。

7.根据权利要求1所述的电路,其特征在于,所述滤波电路为多个,且每一个滤波电路具有不同的带外抑制频段。

8.一种放大电路,其特征在于,至少包括:

9.根据权利要求8所述的放大电路,其特征在于,所述放大器为低噪声放大器,所述第二电感用于输入匹配。

10.一种射频前端模组,其特征在于,至少包括:滤波器、输入匹配器及低噪声放大器,其中,

技术总结

本申请实施例公开一种信号处理电路、放大电路及射频前端模组。其中,该信号处理电路包括:滤波电路,具有第一电感和与所述第一电感并联的电容,用于对接收的射频信号进行带外干扰抑制;第二电感,与所述滤波电路中的所述第一电感串联,用于进行阻抗匹配,所述第二电感与所述第一电感相互耦合,耦合电感使所述第一电感和所述第二电感的等效电感值增大。

技术研发人员:龚仁杰,彭晓雨,姚顺奇,苏强

受保护的技术使用者:广州慧智微电子股份有限公司

技术研发日:

技术公布日:2024/4/7

- 还没有人留言评论。精彩留言会获得点赞!