一种DB9母头转换板

一种db9母头转换板

技术领域

1.本实用新型涉及通讯协议的硬件技术领域,具体的说是一种db9母头转换板。

背景技术:

2.目前,在工程实践中多采用uart的通信协议,其中常用到rs-232和rs-485,这两种通信协议在db9中已对收发针脚以及地线有明确的定义;rs-232是pc机与通信工业中应用最广泛的一种串行接口,rs-232被定义为一种在低速率串行通讯中增加通讯距离的单端标准,rs-232采取不平衡传输方式,即所谓单端通讯;rs-485是美国电子工业协会(eia)在1983年批准了一个新的平衡传输标准(balanced transmission standard),eia一开始将rs(recommendedstandard)作为标准的前缀,不过后来为了便于识别标准的来源,已将rs改为eia/tia;目前标准名称为tia-485,但工程师及应用指南仍继续使用rs-485来称呼此标准。

3.在现有设备通信使用db9接口时,需要在设计硬件电路时提前安排好引脚以实现上位机与下位机的正常通信,当设备设计完成但需要改进通讯方式时,上位机的通讯协议更改较为方便,但下位机的电路已经无法更改,这时候就需要一种串口转换设备,实现通讯协议针脚的兼容。

4.为此,本实用新型提出一种db9母头转换板。

技术实现要素:

5.为了弥补现有技术的不足,以解决背景技术中上位机和下位机通讯协议针脚不兼容,且不能够实现db9针脚之间交错连接的技术问题,本实用新型提出了一种db9母头转换板。

6.本实用新型通过以下技术方案实现:一种db9母头转换板,包括。

7.db9接口,所述db9接口用于连接外部数据接口。

8.针脚设计模块,所述针脚设计模块用于实现所述db9接口的引脚转换。

9.指示模块,所述指示模块用于显示所述db9接口的针脚转换。

10.控制模块,所述控制模块与所述db9接口、所述针脚设计模块及所述指示模块连接,以实现所述db9接口的针脚转换,接受所述针脚设计模块的输入信号,并向所述指示模块发送输出信号。

11.电源系统,所述电源系统与所述db9接口、所述针脚设计模块、所述指示模块及所述控制模块间通过pcb板中的金属丝连接并为之供电。

12.优选地,所述控制模块包括fpga芯片,fpga芯片选择ep4ce6e22c8n,通过fpga芯片内部硬件编码实现对所述db9接口、所述针脚设计模块及所述指示模块的控制。

13.优选地,所述针脚设计模块包括一个3

×

3的矩阵键盘及相匹配的电阻一、一个拨码开关及相匹配的电阻二、一个按钮及相匹配的电阻三;所述电阻一的阻值为(33

±

5%)ω,所述电阻二的阻值为(10k

±

5%)ω,所述电阻三的阻值为(33

±

5%)ω。

14.优选地,所述指示模块包括九组七段的数码管、九个led指示灯及与之匹配的电阻四,电阻四的阻值为(510

±

5%)ω,且每一组所述数码管均有一个所述led指示灯用于显示当前针脚的配置状态。

15.优选地,所述电源系统包括外部电源和三片型号为ams1117-adj的低压差线性稳压器芯片u3-u5。

16.本实用新型的有益效果是。

17.本实用新型通过针脚设计模块、指示模块及控制模块间的相互配合,以实现串口数据传输时数据的接收与发送,与现有技术相比可实现db9接口的9个针脚中任意一个针脚的转换,使得上下位机之间的兼容性更强,适应项目测试中多种设备之间的串口通讯方式。

附图说明

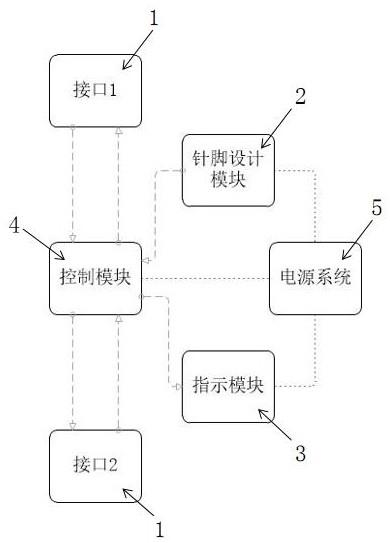

18.图1是本实用新型的系统示意图。

19.图2是本实用新型的示意图。

20.图3是本实用新型控制模块的原理图。

21.图4是本实用新型针脚设计模块的原理图。

22.图5是本实用新型指示模块的原理图。

23.图中。

24.1、db9接口;2、针脚设计模块;3、指示模块;4、控制模块;5、电源系统。

具体实施方式

25.下面结合附图和具体的实施例对本实用新型技术方案作进一步的详细描述,以使本领域的技术人员可以更好的理解本实用新型并能予以实施,但所举实施例不作为对本实用新型的限定,另外,实施例中出现具体的重量、型号、数量等限定仅作为优选实施例。

26.如下图1-5所示。

27.一种db9母头转换板,包括。

28.db9接口1,所述db9接口1用于连接外部数据接口。

29.针脚设计模块2,所述针脚设计模块2用于实现所述db9接口1的引脚转换。

30.指示模块3,所述指示模块3用于显示所述db9接口1的针脚转换。

31.控制模块4,所述控制模块4与所述db9接口1、所述针脚设计模块2及所述指示模块3连接,以实现所述db9接口1的针脚转换,接受所述针脚设计模块2的输入信号,并向所述指示模块3发送输出信号。

32.电源系统5,所述电源系统5与所述db9接口1、所述针脚设计模块2、所述指示模块3及所述控制模块4间通过pcb板中的金属丝连接并为之供电。

33.作为本实用新型的一种具体实施方式,如图3所示,所述控制模块4包括fpga芯片,fpga芯片选择ep4ce6e22c8n,通过fpga芯片内部硬件编码实现对所述db9接口1、所述针脚设计模块2及所述指示模块3的控制。

34.通过fpga芯片内部verilog hdl硬件编码完成对db9接口1的针脚的转换,接收针脚设计模块2共8位的输入信号并实现按键消抖,向指示模块3发出9位的并行信号实现片选和8位的并行信号实现数码管的点亮。

35.作为本实用新型的一种具体实施方式,如图4所示,所述针脚设计模块2包括一个3

×

3的矩阵键盘及相匹配的电阻一、一个拨码开关及相匹配的电阻二、一个按钮(确认键)及相匹配的电阻三;所述电阻一的阻值为(33

±

5%)ω,所述电阻二的阻值为(10k

±

5%)ω,所述电阻三的阻值为(33

±

5%)ω。

36.所述矩阵键盘实现9个针脚的选择,且输出分为2组,每组3根信号线(3.1-3.3;3.4-3.6),2组信号线均在串联匹配电阻一(阻值为33欧姆,允许误差为5%)后连接至fpga芯片。

37.3.1-3.3为fpga的输入信号,3.4-3.6为fpga的输出信号。

38.若fpga芯片输出的行信号为高电平时,无论是否有按键被按下,列信号输入到fpga芯片的电平始终为高电平,这是无法实现任何的矩阵按键值采集的。

39.若fpga芯片输出的行信号为低电平时,没有按键按下,那么列信号会保持高电平(因为有上拉),有键按下时,则由于按键将行、列信号短接,那么列信号的电平会由于行信号而被拉低,通过这种方式可以确认键值;所述确认键一端连接3.3v电平,另一端串联匹配电阻三(阻值为33欧姆,允许误差为5%)后连接至fpga芯片。

40.所述拨码开关三个引脚上下两个引脚分别接3.3v和地,中间的引脚在串联匹配电阻二(阻值为10k欧姆,允许误差为5%)后连接至fpga芯片。

41.匹配的所述电阻一、电阻二及电阻三的作用相同,均用于减少高频噪声以及边沿过冲。

42.作为本实用新型的一种具体实施方式,如图5所示,所述指示模块3包括九组七段的数码管、九个led指示灯及与之匹配的电阻四,电阻四的阻值为(510

±

5%)ω,且每一组所述数码管均有一个所述led指示灯用于显示当前针脚的配置状态。

43.通过针脚4.1-4.9为fpga芯片的输出信号用于片选数码管。

44.当该组针脚中某一针脚拉低时,针脚所对应的数码管则亮起。

45.通过针脚5.1-5.8为fpga芯片的输出信号用于控制数码显示的数字。

46.通过针脚6.1-6.9为fpga芯片的输出信号用于点亮led指示灯,当fpga芯片输出低电平时,相应针脚的led指示灯被点亮。

47.作为本实用新型的一种具体实施方式,所述电源系统5包括外部电源和三片型号为ams1117-adj的低压差线性稳压器芯片u3-u5。

48.通过ams1117-adj的低压差线性稳压器芯片将外部的直流电源输入的+7.5v、+12v转换位可供转换板上芯片和元件需要使用的+1.2v、+2.5v以及+3.3v直流电。

49.工作原理如下。

50.系统上电后,接口1和接口2针脚一一对应,9组数码管上显示接口1侧针脚连接到接口2侧的针脚号。

51.接口1的db9接口的9个针脚用电路板上丝印层印的9个数字代表;当拨码开关处于开状态下,按下矩阵键盘(键盘上数字为1-9)通过键盘扫描以选择主机侧的针脚,按下键盘后通过控制模块相应接口1侧数字上的led灯会亮起,代表当前接口1侧该针脚处于可配置状态;然后将拨码开关调整为关状态,按下矩阵键盘以选择接口2侧的针脚,按下键盘后当前亮起的led灯上方的数码管会显示为当前按下按键代表的数值,及接口2侧连接的针脚;以上步骤完成后按下确认键,控制模块实现针脚的转换。

52.另外,当针脚转换出现错误时,接口1相应针脚上的led灯会进入频闪状态,长按确认键5秒,系统重置,针脚复原。

53.以上仅为本实用新型的优选实施例,并非因此限制本实用新型的专利范围,凡是利用本实用新型说明书及附图内容所作的等效结构或者等效流程变换,或者直接或间接运用在其他相关的技术领域,均同理包括在本实用新型的专利保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1