16APSK的解映射电路的制作方法

本技术涉及解映射硬件电路领域,特别是涉及一种16apsk的解映射电路。

背景技术:

1、apsk是另一种幅度相位调制方式,与传统方型星座qam(如16qam、64qam)相比,在卫星信道中使用高阶调制方式,显然也意味着在抗噪声接收方面的技术进步。apsk分布呈中心向外沿半径发散,所以又名星型qam。与qam相比,在卫星信道中使用高阶调制方式,apsk便于实现变速率调制,因而很适合目前根据信道及业务需要分级传输的情况。当然,16apsk、32apsk也是apsk的一种。

2、常规的16apsk解映射的方法使用的是基于幅度和相位的解映射算法,该算法要进行反三角计算,运算量还是比较大,运算时间较长,不适合在实时性要求比较高的嵌入式或者fpga的硬件上实现。

技术实现思路

1、本实用新型的目的在于克服现有技术的缺点,提供一种16apsk的解映射电路。

2、本实用新型的目的通过以下技术方案来实现:

3、本实用新型提供一种16apsk的解映射电路,包括:

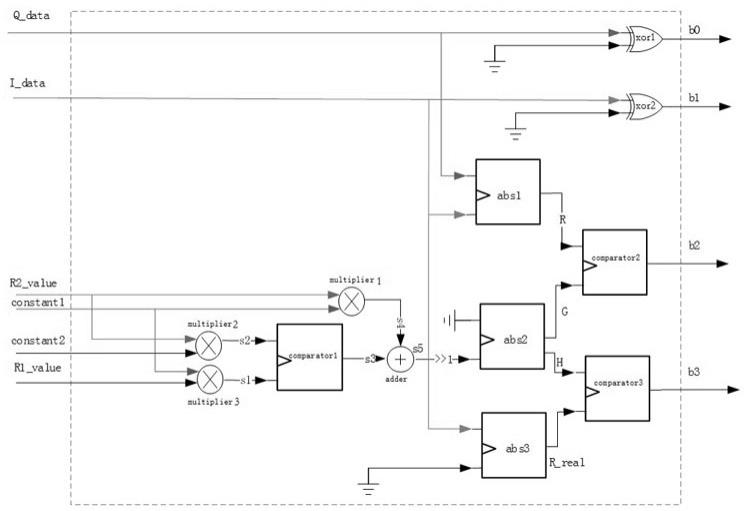

4、第一支路,所述第一支路用于对待解映射基带数据的虚部信号进行处理以解析出该基带数据星座点信号对应二进制编码的最低位;

5、第二支路,所述第二支路用于对待解映射的基带数据实部信号进行处理以解析出该基带数据星座点信号对应二进制编码的次低位;

6、第三支路,所述第三支路用于对待解映射的基带数据实部信号和虚部信号、第一常量信号、第二常量信号、所述基带数据星座点的内圆半径信号和外圆半径信号进行处理以解析出所述基带数据星座点信号对应二进制编码的次高位和最高位,所述第一常量信号为cos(π/4),所述第二常量信号为cos(5π/12)。

7、在一种可能的设计中,所述第一支路包括第一异或电路,所述第一异或电路包括用于接收待解映射基带数据的虚部信号的第一输入端和接地的第二输入端。

8、在一种可能的设计中,所述第二支路包括第二异或电路,所述第二异或电路包括用于接收待解映射基带数据的实部信号的第三输入端和接地的第四输入端。

9、在一种可能的设计中,所述第三支路包括:

10、用于对基带数据星座点的外圆半径信号和第一常量信号进行乘积运算的第一乘法器;

11、用于对基带数据星座点的外圆半径信号和第二常量信号进行乘积运算的第二乘法器;

12、用于对第二常量信号和基带数据星座点的内圆半径信号进行乘积运算的第三乘法器;

13、用于对第二乘法器和第三乘法器输出信号进行比较的第一比较器;

14、用于对所述第一比较器和所述第一乘法器输出信号进行相加处理的加法器;

15、用于对所述加法器的输出信号进行移位处理使所述加法器的输出信号右移一位的移位寄存器;

16、用于对所述移位寄存器输出信号和零位信号进行取模处理的第二取模电路;

17、用于对所述解映射的基带数据实部信号和零位信号进行取模处理的第三取模电路;

18、用于对待解映射的基带数据实部信号和虚部信号进行取模处理的第一取模电路;

19、用于对所述第一取模电路和第二取模电路的输出信号进行比较以解析出所述基带数据星座点信号对应二进制编码的次高位的第二比较器;

20、用于对所述第二取模电路和所述第三取模电路的输出信号进行比较以解析出所述基带数据星座点信号对应二进制编码的最高位的第三比较器。

21、本实用新型至少具有以下优点:

22、本方案通过三条支路分别解映射出基带数据星座点信号对应二进制编码的最低位、次低位、次高位和最高位,便于fpga等嵌入式硬件的实现,有利于实时信号的收发端同步处理。

技术特征:

1.16apsk的解映射电路,其特征在于,包括:

2.根据权利要求1所述的16apsk的解映射电路,其特征在于:所述第一支路包括第一异或电路,所述第一异或电路包括用于接收待解映射基带数据的虚部信号的第一输入端和接地的第二输入端。

3.根据权利要求1所述的16apsk的解映射电路,其特征在于:所述第二支路包括第二异或电路,所述第二异或电路包括用于接收待解映射基带数据的实部信号的第三输入端和接地的第四输入端。

4.根据权利要求1所述的16apsk的解映射电路,其特征在于,所述第三支路包括:

技术总结

本技术公开了一种16APSK的解映射电路,包括:第一支路,所述第一支路用于对待解映射基带数据的虚部信号进行处理以解析出该基带数据星座点信号对应二进制编码的最低位;第二支路,所述第二支路用于对待解映射的基带数据实部信号进行处理以解析出该基带数据星座点信号对应二进制编码的次低位;第三支路,所述第三支路用于对待解映射的基带数据实部信号和虚部信号、第一常量信号、第二常量信号、所述基带数据星座点的内圆半径信号和外圆半径信号进行处理以解析出所述基带数据星座点信号对应二进制编码的次高位和最高位。采用上述硬件电路,便于FPGA等嵌入式硬件的实现,有利于实时信号的收发端同步处理。

技术研发人员:姜淼,刘畅

受保护的技术使用者:成都威频科技有限公司

技术研发日:20230117

技术公布日:2024/1/11

- 还没有人留言评论。精彩留言会获得点赞!