时间同步方法及图像信号发生装置与流程

本技术属于图像数据传输领域,更具体地,涉及一种时间同步方法及图像信号发生装置。

背景技术:

1、目前随着显示技术的发展,显示设备的分辨率和刷新率越来越高,2k(25601440)和4k(38402160)已成为目前的主流分辨率,在一些大屏显示设备上,已支持8k(76804320)甚至16k(153608640)的超高分辨率。而在将图像数据传输给如此超高分辨率的屏幕时,一些传统多线点屏接口如v-by-one等,单一接口的带宽已经无法满足,因此则需要多个接口协同输出信号进行点屏。

2、而多个接口往往分布在图像信号发生装置的多片芯片上;多片芯片可以是多片现场可编程门阵列(field programmable gate array,fpga)上,其中1片fpga作为主端(master),另外几片fpga作为从端(slave)。主端用于生成图像信号,多个从端用于将图像信号协同发送给显示装置。当多个从端协同向显示装置发送图像信号时,需要它们之间协同工作,且对同步性有很高的要求。因此图像数据与控制信号在多片fpga之间如何稳定同步传输非常关键。

3、目前已有的常用通信接口有集成电路总线(inter-integrated circuit,iic)和串行外围设备接口(serial peripheral interface,spi)等,这两种接口只有在传输数据时才会有随路时钟信号,即不能给下游提供一个稳定的用于进行时钟同步的时钟。此外,还有一些高速接口例如高速串行计算机扩展总线标准(peripheral componentinterconnect express,pcie)和高速串行通信的协议(serial rapidio,srio)等,但其实现复杂,且会占用fpga中的大量逻辑资源。

4、因此,现有图像信号发生装置无法保证图像数据与控制信号在多片芯片之间稳定同步传输至显示装置。

技术实现思路

1、针对现有技术的缺陷,本技术的目的在于提供一种时间同步方法及图像信号发生装置,旨在解决现有图像信号发生装置无法保证图像数据与控制信号在多片芯片之间稳定同步传输至显示装置的问题。

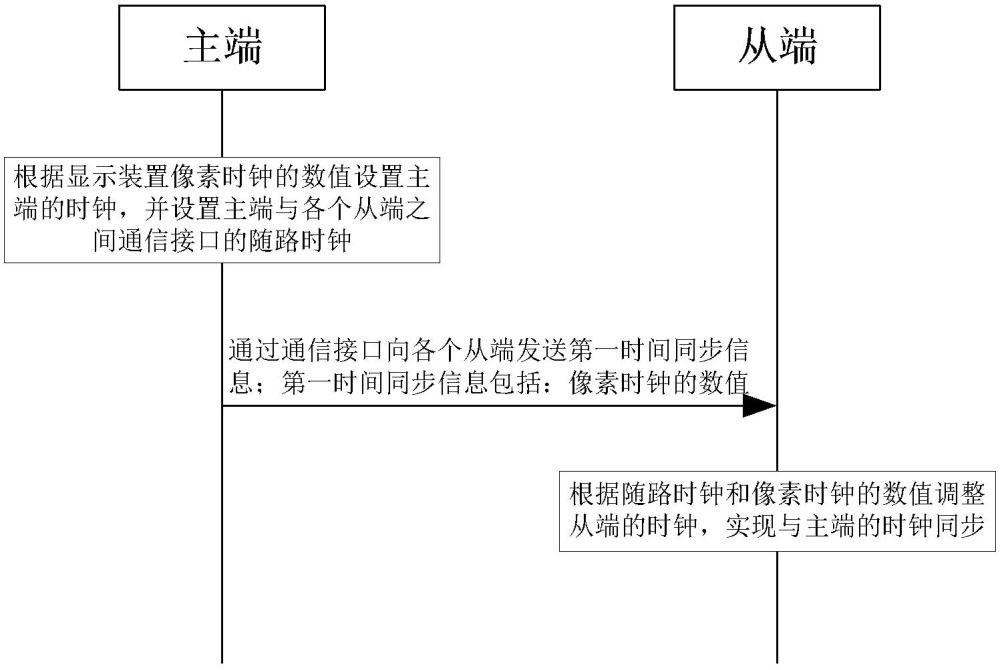

2、为实现上述目的,第一方面,本技术提供了一种时间同步方法,应用于图像信号发生装置,所述图像信号发生装置包括一个主端和多个从端,所述主端用于生成图像信号,所述多个从端用于将所述图像信号协同发送给显示装置;方法包括:

3、所述主端根据显示装置像素时钟的数值设置主端的时钟,并设置主端与各个从端之间通信接口的随路时钟;

4、所述主端通过所述通信接口向各个从端发送第一时间同步信息;所述第一时间同步信息包括:所述像素时钟的数值;

5、所述各个从端根据所述随路时钟和像素时钟的数值调整从端的时钟,实现与主端的时钟同步。

6、需要说明的是,本技术通过主端向从端发送随路时钟,以将随路时钟作为从端的时钟源,便于从端根据随路时钟和像素时钟的数值调整从端的时钟,实现从端与主端的时钟同步。

7、在一种可能的实现方式中,所述从端以所述随路时钟作为时钟源;

8、所述主端与从端之间的连接被启动的时间段内,所述主端通过通信接口持续向从端发送所述随路时钟。

9、进一步地,本技术中主端与从端的连接被启动的时间段内,主端持续向从端发送随路时钟,以便从端随时能够根据随路时钟调整从端的时钟,实现从端与主端的时钟在主端与从端存在连接的时间段内一直保持一致。

10、在一种可能的实现方式中,所述第一时间同步信息还包括:所述主端侧发送第一时间同步信息的时间;

11、所述方法还包括:

12、所述各个从端通过所述通信接口向主端发送第二时间同步信息;所述第二时间同步信息包括:所述各个从端侧发送第二时间同步信息的时间和所述各个从端侧接收到第一时间同步信息的时间;

13、所述主端和各个从端参考上述第一时间同步信息和第二时间同步信息的发送方式循环往返发送时间同步信息;

14、所述各个从端和/或主端根据从端侧接收到第一时间同步信息的时间、主端侧接收到第二时间同步信息的时间、主端侧发送第一时间同步信息的时间以及从端侧发送第二时间同步信息的时间确认主端和从端之间的时间计数差,并根据所述时间计数差调整对应端的时间,实现主端和从端的时间同步。

15、可以理解的是,主端和从端之间相互持续循环发送相关的时间同步信息,以便主端和从端实时调整时间计数值,时刻保持主端和从端的时间同步。

16、在一种可能的实现方式中,所述时间计数差通过如下步骤确定:

17、将从端侧接收到第一时间同步信息的时间与从端侧发送第二时间同步信息的时间累加得到第一时间和;

18、将主端侧发送第一时间同步信息的时间与主端侧接收到第二时间同步信息的时间累加得到第二时间和;

19、将两个时间和的差值乘以二分之一得到所述时间计数差。

20、在一种可能的实现方式中,所述主端根据显示装置的像素时钟设置主端与从端之间通信接口的随路时钟,包括:

21、所述主端根据预设的像素时钟的数值、随路时钟的数值和主端时钟的数值的关系,设置所述随路时钟;其中,每一组随路时钟的数值和像素时钟数值的组合,对应一个倍频系数,以便所述各个从端根据所述随路时钟和对应的倍频系数确定从端的时钟,使得各个从端的时钟与主端的时钟同步。

22、具体地,本技术通过预设像素时钟数值范围、随路时钟数值范围以及主端高频时钟数值范围与对应倍频系数的数值范围相对应,以便从端能够根据收到的随路时钟和像素时钟的数值确定对应倍频系数后,基于随时时钟还原确定从端的高频时钟。

23、在一种可能的实现方式中,所述主端时钟的数值为所述像素时钟数值的偶数倍,以便所述随路时钟与像素时钟具有固定的相位关系。

24、需要说明的是,时间计数器工作在像素时钟下,而用于携带时间戳的脉冲信号产生于高频时钟下,为了提高时间同步的精度,就不能受到跨时钟域采样的影响,所以高频时钟应该是像素时钟的偶数倍,这样在fpga内部认为他们其实是同步时钟,以能保证随路时钟和像素时钟有固定的相位关系。

25、在一种可能的实现方式中,所述从端根据所述随路时钟和对应的倍频系数设置从端的时钟。

26、第二方面,本技术提供了一种图像信号发生装置,包括:主端和多个从端;

27、所述主端,用于获取显示装置的像素时钟,并根据显示装置像素时钟的数值设置主端的时钟,并设置主端与各个从端之间通信接口的随路时钟;

28、所述主端,用于通过所述通信接口向各个从端发送第一时间同步信息;所述第一时间同步信息包括:所述像素时钟的数值;

29、所述各个从端,用于根据所述随路时钟和像素时钟的数值调整从端的时钟,实现与主端的时钟同步;

30、所述主端,用于生成显示装置的图像信号,并将所述图像信号分发给各个从端;

31、所述各个从端,用于将各自接收的图像信号协同发送给显示装置。

32、在一种可能的实现方式中,所述第一时间同步信息还包括:所述主端侧发送第一时间同步信息的时间;

33、所述各个从端,用于通过所述通信接口向主端发送第二时间同步信息;所述第二时间同步信息包括:所述各个从端侧发送第二时间同步信息的时间和所述各个从端侧接收到第一时间同步信息的时间;

34、所述主端和各个从端参考上述第一时间同步信息和第二时间同步信息的发送方式循环往返发送时间同步信息;

35、所述各个从端和/或主端,用于根据从端侧接收到第一时间同步信息的时间、主端侧接收到第二时间同步信息的时间、主端侧发送第一时间同步信息的时间以及从端侧发送第二时间同步信息的时间确认主端和从端之间的时间计数差,并根据所述时间计数差调整对应端的时间,实现主端和从端的时间同步。

36、在一种可能的实现方式中,所述主端,根据预设的像素时钟的数值、随路时钟的数值和主端时钟的数值的关系,设置所述随路时钟;其中,每一组随路时钟的数值和像素时钟数值的组合,对应一个倍频系数;

37、所述各个从端,根据所述随路时钟和对应的倍频系数确定从端的时钟,使得各个从端的时钟与主端的时钟同步。

38、总体而言,通过本技术所构思的以上技术方案与现有技术相比,具有以下有益效果:

39、本技术提供一种时间同步方法及图像信号发生装置,提出一种轻量级的传输数据和时钟的接口,平衡传输的开销与速率,兼顾数据传输的效率和可靠性,并且主端可以给从端提供稳定的时钟源以进行整个系统的时钟同步。主端和从端之间通信接口的随路时钟可给从端提供稳定的参考时钟源,从而实现主端和从端的时钟同步。由于本技术中主端与从端存在连接的时间段内主端持续向从端发送随路时钟,对比传统低速通信接口传输速率明显提高,且实现简单,平衡了传输的开销与速率。

- 还没有人留言评论。精彩留言会获得点赞!