一种多层结构的聚合物基复合薄膜及其制备方法

本发明属于聚合物储能,具体涉及一种多层结构的聚合物基复合薄膜及其制备方法。

背景技术:

1、随着现代科学技术的飞速发展,电力电子系统领域迫切需要性能更为卓越的介电材料。其中,包括栅介质、高储能密度电容器以及电活性材料等在内的微电子器件均要求纳米复合材料在具有高介电常数和介电强度的同时,依然拥有低介电损耗、高的击穿场强和良好的韧性。传统聚合物材料如聚酰亚胺(pi)、聚偏氟乙烯(pvdf)、环氧树脂等,具有体积小、易加工等特点,但是介电常数很低,难以满足实际使用要求。

2、为进一步提升聚合物材料的电位移和储能密度,具有高介电常数的纳米陶瓷颗粒被选为填料加入聚合物基体中,由此构成陶瓷/聚合物复合材料。通过一方面选取高介电常数陶瓷为填料可有效提高复合材料的介电常数,另一方面聚合物基体又保留了其较高的耐击穿场强,从而实现对储能密度的显著提高。目前,常用于制备pvdf基复合材料的陶瓷填料主要有钛酸钡(batio3)、二氧化钛(tio2)、锆钛酸铅(pbzrtio3)等。然而,随着陶瓷/聚合物储能复合材料的发展,研究者发现尽管陶瓷的加入可以有效提高聚合物的介电常数,但同时也会降低其击穿场强并引入较高的漏电导损耗,因此仅采用单一陶瓷与聚合物共混制备复合材料的方法已不能满足对更高储能密度的需求。

技术实现思路

1、为了克服上述现有技术的缺点,本发明的目的在于提供一种多层结构的聚合物基复合薄膜及其制备方法,以解决仅采用单一陶瓷与聚合物共混制备的复合材料储能密度不高的问题,本发明所制备的多层结构的复合薄膜具有高击穿场强和高储能密度,可以快速充放电,且具有优异的循环稳定性。

2、本发明通过以下技术方案实现:

3、一种多层结构的聚合物基复合薄膜,所述多层结构的聚合物基复合薄膜包括0.15srtio3-0.85na0.5bi0.5tio3/pvdf复合层和pvdf层,所述0.15srtio3-0.85na0.5bi0.5tio3/pvdf复合层和所述pvdf层循环交替,且最外层为pvdf层,所述0.15srtio3-0.85na0.5bi0.5tio3/pvdf复合层为晶须0.15srtio3-0.85na0.5bi0.5tio3与pvdf的复合层。

4、优选的,所述0.15srtio3-0.85na0.5bi0.5tio3/pvdf复合层中晶须0.15srtio3-0.85na0.5bi0.5tio3的体积分数为2%~10%。

5、所述的多层结构的聚合物基复合薄膜的制备方法,包括以下步骤:

6、步骤1,将na2co3和tio2进行混合,得到混合物a,混合物a与nacl熔盐进行球磨,保温、煅烧、洗涤、干燥,获得一维na2ti6o13模板;

7、步骤2,将na2ti6o13模板、na2co3、tio2、bi2o3和srco3混合,得到混合物b,混合物b与nacl熔盐搅拌混合均匀,保温、煅烧、洗涤、干燥,获得一维0.15srtio3-0.85na0.5bi0.5tio3晶须;

8、步骤3,将一维0.15srtio3-0.85na0.5bi0.5tio3晶须分散到dmf中,得到悬浊液,在悬浊液中加入pvdf粉末,分散,得到均匀共混的0.15srtio3-0.85na0.5bi0.5tio3/pvdf悬浊液;将pvdf粉末均匀分散在dmf中,得到pvdf溶液;

9、步骤4,将pvdf溶液进行一次流延,干燥成膜;将0.15srtio3-0.85na0.5bi0.5tio3/pvdf悬浊液进行二次流延,干燥成膜,交替进行流延多次,得到初步样品;将初步样品干燥,进行加热保温后,淬火,得到多层结构的聚合物基复合薄膜。

10、优选的,步骤1中,在1000~1200℃下煅烧1~3h。

11、优选的,步骤2中,na2ti6o13、na2co3、tio2、bi2o3和srco3的摩尔比为34:17:36:51:36;混合物b与熔盐的质量比为1:2。

12、优选的,步骤2中,在800~1000℃煅烧5~7h。

13、优选的,步骤3中,将一维0.15srtio3-0.85na0.5bi0.5tio3晶须分散到dmf中,具体是:将一维0.15srtio3-0.85na0.5bi0.5tio3晶须加入到dmf中,在450~600r·min-1的转速和40~80℃的温度下先搅拌1~3h,后超声25~45min,搅拌和超声交替4~8次。

14、优选的,步骤4中,流延温度为185~195℃,控制刮刀的高度为10~20μm。

15、优选的,步骤4中,在75~85℃真空干燥25~35min成膜;将初步样品在55~75℃真空干燥10~14h。

16、优选的,步骤4中,在195~205℃下加热保温7~9min后放在-3~4℃的冰水中淬火。

17、与现有技术相比,本发明具有如下的有益效果:

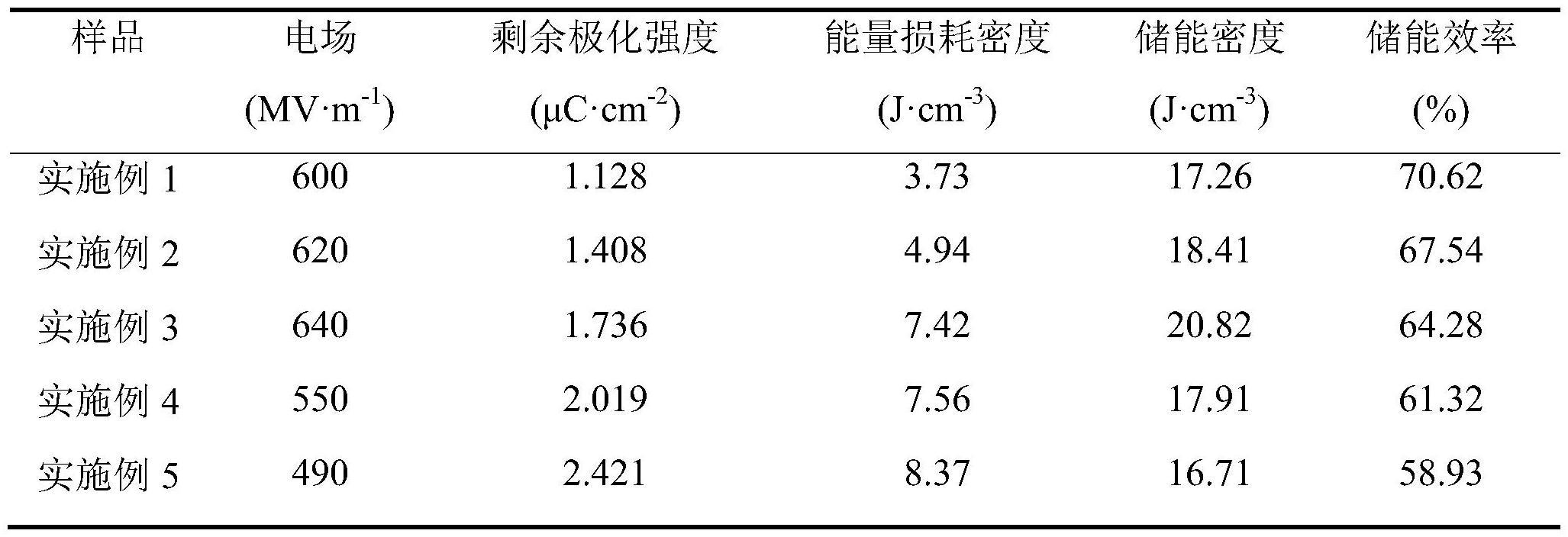

18、本发明公开的多层结构的聚合物基复合薄膜,0.15srtio3-0.85na0.5bi0.5tio3/pvdf复合层和所述pvdf层循环交替叠层,纯pvdf作为高击穿层提高击穿强度,同时将与电场方向垂直排布的0.15srtio3-0.85na0.5bi0.5tio3晶须加入0.15srtio3-0.85na0.5bi0.5tio3/pvdf复合层以提高介电常数作为高介电层。这种多层结构可以有效结合不同层各自具有的优势,同时获得了高介电常数和高击穿场强。本发明通过叠层的方式使得薄膜内部电场进行二次排布,旨在提高复合薄膜的最大击穿电场和能量储能密度,采用一维0.15srtio3-0.85na0.5bi0.5tio3(snbt)晶须作为陶瓷填料掺入聚偏氟乙烯(pvdf)聚合物中做成复合薄膜,可以解决采用单一陶瓷与聚合物共混制备的复合材料储能密度不高的问题,具有高储能密度和高储能效率,可适用于多种应用领域。本发明复合薄膜表面光滑,无明显裂纹出现,顶层和底层实现了完美的衔接,整个薄膜致密紧凑,没有明显的气孔和缺陷。

19、进一步地,0.15srtio3-0.85na0.5bi0.5tio3晶须占0.15srtio3-0.85na0.5bi0.5tio3/pvdf体积的2%~10%,调控0.15srtio3-0.85na0.5bi0.5tio3晶须的体积占比,以提高该层的介电常数,作为高介电层,可以大幅度提高储能密度。

20、本发明公开的一种多层结构的聚合物基复合薄膜的制备方法,先采用熔盐法制备一维的0.15srtio3-0.85na0.5bi0.5tio3晶须,再将其与pvdf粉末分散于有机溶剂中,得到悬浊液,同时配置pvdf溶液,之后通过流延法对悬浊液和pvdf溶液依次成膜,可初步制得复合薄膜,最后再保温淬火,可得到多层结构的聚合物基复合薄膜,本发明的制备工艺简单、稳定,适合工业化生产。

21、进一步地,洗涤用蒸馏水反复清洗至滤液无cl-离子为止,可以提高膜化学稳定性,不易造成膜的缺陷。

22、进一步地,搅拌和超声交替进行,可以使组分充分混合,原料分布均匀,减少缺陷的发生。

23、进一步地,对薄膜进行热处理,在冰水中淬火,可以提高薄膜的铁电性,减少漏电电流。

- 还没有人留言评论。精彩留言会获得点赞!