LED显示系统的制作方法

led显示系统

技术领域

1.本实用新型总体上介绍了驱动led阵列的装置。更具体地而言,本实用新型涉及led显示面板启用扩展灰度值的装置。

背景技术:

2.现代led显示面板要求更高的灰度级(即灰度值,灰度),以实现更高的颜色深度和更高的视觉刷新率,从而减少闪烁。例如,rgb led像素的16位灰度值可以使 r、g、b led分别实现16位色阶(2

16

=65536)。这样一个rgb led像素能够显示总共655363种颜色。一种常用的调节led灰度的方法是脉冲宽度调制(pwm)。简单地说,脉冲宽度调制(pwm)根据信号脉冲的宽度(即脉冲持续时间或脉冲宽度)打开或关闭 led。开启时间和关闭时间的比值决定了led的亮度。不同的比值代表不同的灰度。 led显示系统的配置和操作,包括led拓扑,电路系统,pwm方案和pwm引擎在 2011年9月21日提交的美国专利8,963,811b2中有详细解释。

3.目前市场上大多数led显示器具有16位灰度范围,不足以模拟人眼可见的全部亮度范围。例如,最先进的led显示器的亮度范围是0.1尼特到1,700尼特。希望有一种具有更宽亮度范围的显示器,例如,发出光线亮度为0.005尼特至10,000尼特的显示器。因此,需要采用相应的方法和装置来扩大led显示屏的亮度范围。

技术实现要素:

4.在一个实施例中,提供了一种动态范围增大的led显示系统。所述led显示系统包括排列成led阵列的多个led和一个为驱动所述led阵列而配置的驱动电路。 led(或led像素)可以是rgb led或单色led。驱动电路包括pwm引擎、加法器 (即加法器电路)、累加器(即寄存器电路)、乘法器(即二进制乘法器电路)和帧缓存器。帧缓存器可以包括一个发射器以及一个或多个存储器。pwm引擎从帧缓存器接收 pwm数据,并产生多个pwm脉冲(或简单的“脉冲”)来驱动led阵列。

5.在操作期间,乘法器将第一位深度的图像数据(pwm)与倍数(m)相乘,以产生具有第二位深度的输入数据(pwm_m)。倍数具有一个或多个位长度的整数部分(mi)以及一个或多个位长度的分数部分(mf)。输入数据有一个整数部分(pwm_mi)和一个小分数部分(pwm_mf)。加法器将当前输入数据的pwm_mf值与累加器中的余数值相加。驱动器电路运行以更新余数,使其等于加法的总和。驱动器电路进一步操作以从加法的和中减去整数1,并且当加法运算的和等于或大于整数1时,更新累加器中的余数以等于减法的结果,并且将整数“1”加到pwm_mi中的一个位上。pwm_mi的值被发送到帧缓存器,帧缓存器向pwm引擎提供pwm数据,从而产生pwm脉冲。

6.在一个实施例中,pwm_mi中从加法器接收整数“1”的一个位是专门为接收功能而指定的,其默认值为零。加法器用整数“1”填充该位,而不考虑该位中存储的当前值。

7.在另一个实施例中,pwm引擎以如下方式产生pwm脉冲:为pwm_mi中的每个非零位产生多个脉冲,脉冲数与非零位的指定值一致,不为pwm_mi中携带整数 0的每个位产生脉

冲,无论pwm_mf的每一位的值是多少,均不为pwm_mf中的每个位产生脉冲。

8.在另一实施例中,提供了一种增加led显示器动态范围的方法。该方法包括以下步骤:将第一位深度的图像数据(pwm)乘以倍数(m)以产生具有第二位深度的输入数据(pwm_m),其中该倍数具有一个或多个位长度的整数部分(mi)以及一个或多个位长度的分数部分(mf),其中该输入数据具有整数部分(pwm_mi)和分数部分(pwm_mf);对当前输入数据的pwm_mf的值和累加器中的余数进行加法运算,当加法运算的和小于 1时,更新余数以等于加法的和;当加法运算的和等于或大于整数1时,从加法的和中减去整数1,并更新余数以等于减法的结果,并用整数1填充pwm_mi中的一个位;并将pwm_mi的值发送到帧缓存器。帧缓存器向pwm引擎提供pwm数据,用于产生驱动led阵列的pwm脉冲。

9.在增加led显示器动态范围的方法的另一实施例中,用整数1填充pwm_mi中的位的步骤包括用整数1填充该位,而不管该位中存储的当前值大小。当加法的和等于或大于整数1时,该位被保留用于从加法操作中接收整数1,否则该位的值保持为零。

10.在用于增加led显示器动态范围的方法的另一个实施例中,pwm引擎以如下方式产生pwm脉冲:为pwm_mi中的每个非零位产生多个脉冲,其中脉冲数与非零位的指定值一致,不为pwm_mi中携带整数0的每个位产生脉冲,且无论pwm_mf的每一位的值是多少,均不为pwm_mf中的每个位产生脉冲。

附图说明

11.通过结合附图考虑以下详细说明,可以很容易理解本实用新型的教导。

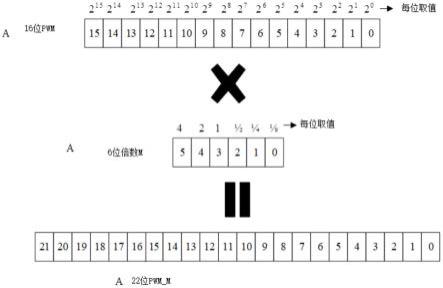

12.图1是图像数据pwm和倍数(m)以及m应用到pwm后的新图像数据 pwm_m的数据排列示意图。

13.图2是说明累加器如何为单个led进行运算的一个示例图。

14.图3是说明累加器如何为单个led进行运算的另一个示例图。

15.图4是5个led构成的阵列的运算示例图。

16.图5是说明图像数据(pwm)和倍数(m)的详细数据排列及其运算的示例图。

17.图6是pwm数据处理的示意性流程图,该流程图示出了具有动态范围扩展器的led显示系统的整体组成。

具体实施方式

18.附图和以下描述仅通过图解的方式对本实用新型的实施例进行说明。应该注意的是,从下面的讨论中,本实用新型的结构和方法的替代实施例将很容易被认为是可以采用的可行替代方案,可以在不背离所要求实用新型的原则的情况下进行使用。

19.现在将详细引用本实用新型的几个实施例,其示例在附图中进行说明。请注意,在任何可行的情况下,在附图中可以使用相似或类似的附图标记,并且可以指示相似或类似的功能。附图仅出于说明之目的描绘了本实用新型的实施例。本领域技术人员将从以下描述中容易地认识到,在不脱离本文所述实用新型内容的原理的情况下,可以采用本文示出的结构和方法的替代实施例。

20.本实用新型的实施例的一个方面如图1所示,其示出了具有16位深度和6位倍数(m)的图像数据(pwm)。在m中,位5、4和3被指定用于整数部分,而位2、1和0 被指定用于小数

部分。通过将16个pwm位乘以6个m位,乘积(pwm_m)为22位,分为19位整数部分(pwm_mi)和3位小数部分(pwm_mf)。注意,根据环境和/或需要,图像数据和倍数m的位深可以是除16或6之外的值,但也可以是其它整数位数。m 中的整数部分或分数部分可以具有更少或更多的位数,并且m中的整数部分的位数和 m中的分数部分的位数可以相同也可以不同。

21.在图1的实施例中,在整数部分添加3位将最大亮度从2

16

增加到2

19

,表示图像数据的16位深度的原始大小增加了8倍(2

19

/2

16

=23=8)。同样,3位二进制分数可以将pwm减小到图像数据原始值的1/8(2-3

)。然而,在本实用新型的实施例中,分数部分在累加器中累加,累加器可以是寄存器。一旦累加器中的值达到或超过值“1”,就从该值中减去“1”。因此,在累积分数值为“1”或更大值的帧中,由于出现一个额外的 pwm脉冲,显示器可以被点亮;而在分数部分的累积值为1或0的帧中,显示器没有额外的脉冲。

22.在不同的实施例中,如果所有图像帧中的分数是1/2(m的第2位数值是1),则每隔一帧显示一个脉冲。如果所有图像帧中的分数数值为1/4(m的第1位数值为1),则每 4帧显示一个额外的脉冲。若所有图像帧中的分数值为1/8(m的第0位数值为1),则每 8帧显示一个额外的脉冲。请注意,在图像帧中的分数部分的其他数据排列中,图像帧中的分数数值可以相同也可以不同,可以是任何分数,如1/2、1/4、1/8和1/16等。例如,如果图像帧中的分数数值为1/16,则每16帧显示一个额外的脉冲。一个脉冲在多帧之间的均匀分布增加了led阵列照所照亮图像的灰度粒度。

23.图2示出了累加器如何为led进行运算的范例。随着时间沿着时间轴所示方向推移(即,从左到右,其中帧1到8随着时间推移连续出现,每个携带其自己的分数数据201),累加器203对帧数据的分数部分进行运算。累加器的三位自下而上分别代表 1/8、1/4和1/2的值,初始值为0。帧#1有一个分数段,其值为3/4(.110,二进制格式)。在累加器203将其初始值0与由帧#1引入的分数值相加之后,由于相加的结果(3/4)小于1,所以不显示pwm脉冲。然而,3/4的分数值存储在累加器203中。

24.帧#2有一个分数段,其值为1/2(.100,二进制格式)。当分数值与存储在累加器 203中的3/4进行相加时,结果是1 1/4。因此,从累加器中减去整数“1”,使得累加器203 中的余数为1/4(二进制格式的0.010),而整数“1”作为进位输出值,用于填充 pwm_mi的整数部分中的进位输出位202。

25.帧#3有一个分数段,其值为1/2(.100,二进制格式),将其添加到累加器203中的剩余值1/4上,以在累加器203中为帧#3产生一个数值3/4(.110,二进制格式)。由于帧#4 有一个分数段,其值为0(.000,二进制格式),将分数值0加到累加器203中的剩余值不会改变累加器203中的剩余值。因此,当帧#4被处理时,累加器203中的剩余值保持为3/4(.110,二进制格式)。

26.帧#5有一个分数段,其值为7/8(.111二进制格式),将该分数值与累加器203中的剩余值-3/4相加(0.110,二进制格式),产生一个15/8的数值。因此,从累加器中减去整数“1”,使得累加器中的余数变为5/8(0.101,二进制格式),而整数“1”作为进位输出值来填充pwm_mi的整数段中的进位输出位202。

27.帧#6有一个分数段,其值为1/8(.001,二进制格式),将其与累加器中的剩余值

‑ꢀ

5/8(.101,二进制格式)相加,以产生一个3/4的数值(.110,二进制格式)。帧#7有一个分数段,其值为1/2,(.100,二进制格式),将该分数值与累加器中的剩余值-3/4相加(.110,二进

制格式),得出一个数值1 1/4。因此,从累加器203中减去整数“1”,使得累加器中的余数为1/4(0.01,二进制格式),整数“1”作为进位输出值,用于填充pwm_mi的整数段中的进位输出位202。由于帧#8有一个分数段,其值为0(0.000,二进制格式),将分数值0加到累加器203中的剩余值,不会使累加器203中的剩余值发生任何改变。

28.如以上描述和图2所示,每个新帧更新累加器203中的值。如果该值达到1或更大,则从累加器203中减去1,余数留在累加器203中。

29.与图2类似,图3示出了累加器303沿所示时间轴所做的相同运算(即,从左至右,其中帧1至8随着时间的推移连续显示,每个帧带有其自己的分数数值301)。在这种情况下,由于帧#2到#6都具有分数值0,所以在累加器将帧#1引入的值1/2与帧#7 引入的值1/2相加之后,只有帧#8接收到一个额外的pwm脉冲,这导致进位输出位整数“1”被存储在pwm_mi的进位输出位302中,并且存储在pwm_mi进位输出位302 中的值“1”促使pwm引擎产生一个额外的脉冲。

30.值得注意的是,尽管图2和图3都示出了各帧的图像数据的分数值达到“1/8"粒度(而不是更细粒度的分数值,如“1/16”或“1/32”,或更粗粒度的分数值,如“1/4”或“1/2”),但是帧的图像数据的分数值可以是任何实际粒度值。还应注意的是,尽管图2和图3都示出了累加器的小数部分中的三个位从底部到顶部分别表示位值“1/8”,“1/4”和“1/2”,但是也可以使用其他可运算的排列,例如累加器的小数部分具有更少或更多的位数,或者累加器的小数部分的每个位表示与图2和图3所示不同的数值。

31.图4示出了根据本实施例对5个led像素操作的运算。它们都有一个相应的累加器,通过将新帧的分数值添加到存储在累加器中的分数值来累加(或相加)分数值。当累加器的输出等于或大于“1”时,“1”被“输出”并用来填充图像数据的一个整数部分(即pwm_mi)。在pwm引擎对pwm数据进行处理后,根据图像数据整数部分数位填充的值“1”,向led发送了一个额外的pwm脉冲。

32.具体而言,图4示出了新帧的5个led像素,每个像素具有其自己的分数部分 (分别为401、402、403、404和405)。在led#1的分数部分401中,它具有三个单独的位401_0、401_1和401_2,每个位分别表示数值“1/8”,“1/4”“和”“1/2”。同样,分数部分 402、403、404和405都有与分数部分401相同的排列。如上所述,位数和各位的指定值不限于图4所示的内容。此外,分数部分可以有彼此相同或不同的数据排列。

33.除了新帧的五个分数段之外,图4示出了五个累加器,每个累加器存储五个发光二极管的当前帧数据的分数部分的数值。在累加器406中,有三个位406_0、406_1 和406_2,每个位分别具有指定值“1/8”、“1/4”和“1/2”。同样,累加器407、408、409和 410都具有与累加器406相同的排列。406、407、408、409和410的排列可以彼此相同也可以彼此不同。然而,为了在累加器部分的led所使用的特定led的新帧数据的分数部分数值之间进行加法运算,每个累加器的排列必须与特定led的新帧数据的相应分数相匹配(就其中的位数和每个位的指定值而言)。也就是说,累加器406的排列必须匹配led#1新帧数据的分数部分401;累加器407的排列必须匹配led#2新帧数据的分数部分402;累加器408的排列必须匹配led#3新帧数据的分数部分403;累加器409的排列必须匹配led#4新帧数据的分数部分404;并且累加器410的排列必须匹配led#5的新帧数据的分数部分405。

34.图4还示出了五个进位输出位411、412、413、414和415,其中每一个都是图像数据

的pwm_mi的一部分,分别对应于led#1、led#2、led#3、led#4和 led#5。当特定led的新帧数据的分数部分和对应于该led的累加器中的当前值所进行的加法运算产生数值“1”或更大的数值时,这五个进位输出位被专门保留用来存储数值“1”。在进位输出位被数值“1”填充的情况下,当处理新计算的图像数据时,pwm 引擎会产生附加脉冲即是进位输出位获得数值“1”的期望效应。在进位输出位填充数值“0”(默认值)的情况下,当处理新计算的图像数据时,pwm引擎不会产生额外的脉冲,这也是进位输出位获得填充值“0”的期望效应。一旦进位输出位中的值“1”被pwm引擎读取并产生一个额外的脉冲,进位输出位中的值就会恢复到默认值“0”。换而言之,进位输出位就是一个占位符,持有一个“开/关”标志(对应于“1”或“0”),以通知pwm引擎在读取新计算的帧数据时产生或不产生附加脉冲。每次pwm引擎使用该位时,它的值都会恢复为“0”,因此该位对从一帧到后续帧的数据没有累积效应。

35.以对存储在401和406中的数据进行加法运算(用421表示)为例,在对应于 led#1的累加器406中进行加法运算,产生(用422表示)一个数值3/8(“.011”,二进制格式)(3/8+0=3/8).该值以二进制格式表示为.011,并用于替换416中的值.000(注意,现在416反映了加法运算之后累加器的状态),并且相应的进位输出位411不接收进位输出值“1”,因此保持为“0”。类似地,对存储在402和407中的数据的加法运算以及对存储在405和410中的数据的加法运算产生小于“1”的数值。这样,即使累加器407和 410位分别用新计算的分数值“5/8”(“.101”,二进制格式)、(“.110”,二进制格式)进行更新,它们相应的进位输出位412和415分别不接收进位输出值“1”,因此仍然保持它们的默认值“0”。

36.对存储在403和408中的数据进行加法运算,以此为另一个示例,在对应于 led#3的累加器408中进行的加法运算产生一个数值1 3/8(1.101,二进制格式)(7/8+3/4 =1 3/8),从所得值中减去值“1”后(该值进位到进位输出位413),剩余的值以二进制格式表示为“.101”,并用于替换408中的“.110”。因此,相应的进位输出位413接收进位输出值“1”。类似地,对存储在404和409中的数据的加法运算产生“1.001”,一个大于“1”的值,导致相应的进位输出位414接收进位输出值“1”,并用“.001”来更新新帧数据 419的分数部分(加法运算的结果减去“1”后的剩余值)。

37.由t0、t1和t2表征的上述事件的时序表明,在t0时刻,累加器406、407、 408、409和410各自保持其当前值(分别为“.000”、“0.001”、“0.110”、“0.011”和“.101”)。在t1时刻,五个发光二极管(401、402、403、404和405)的图像数据的五个分数部分数值变得可用,并且在t2时刻生成加法运算的结果。

38.图5更全面地示出了一个关于数据排列的实施例,这些数据包括存储在存储装置501中的倍数(m)、存储在存储装置502中的图像数据(pwm)和存储在存储装置503 中的扩展图像数据(pwm_m)。存储装置501、502或503可以是寄存器或存储器。在该实施例中,存储m数据的501有6位,其中3位被分配给整数部分mi(整数),另外3 位被分配给小数部分mf(小数)。存储输入pwm数据的存储装置502有16位,而存储 pwm_m数据的503有22位。pwm和m的乘积pwm_m有22位(#0位至#21位)。存储在存储装置505中的pwm_mi的整数部分的范围是从#3位到#21位;而存储在存储装置504中的分数部分pwm_mf的范围从#0位到#2位。累加器506有3位,与 pwm_mf中的位数相匹配。

39.如图4所述,当pwm_mf的值与累加器的值相叠加时,其和用于更新累加器的数值,并在和的数值等于或大于1时,将整数“1”填入进位输出位。在图5中,进位输出位507可以用

和的进位部分(即,整数“1”)进行填充,并且506的数值用余数更新为508。此外,存储pwm_mi数据的505中的数据阵列与进位输出位507进行连接,以形成pwm_mi的扩展阵列存储器511。如505所示,得到的pwm_mi被扩展为20位,而不是其原始大小19位。

40.作为帧缓存器512的两个独立且协作的部分,面板509和510是表征led的图像数据阵列的两个示意图,其中,每个led具有3位长的累加器和19位长的pwm_mi。注意,在该实施例中,对于每个led,其pwm_mf并不存储在509或510中的pwm存储器中,而是累积存储在led的累加器中。如图5所示,存储在504中的数据没有被pwm引擎读取来产生脉冲(该引擎仅读取pwm_mi中的数据来确定要产生多少脉冲)。然而,将存储在504中的一个led的新分数数据与特定led的累加器506的当前值进行相加(通过一项加法运算513)来生成总和。在总和等于或超过“1”的情况下,整数“1”被输出并填充led的进位输出位507,并且在减去“1”之后总和的余数被存储在508中。换句话说,尽管进位输出位507与pwm存储器(其仅存储pwm_mi的值)的整数部分相加(经由运算507,即“二进制加法”)并生成扩展的pwm_mi511,其被写入帧缓存器512(特别是pong存储器中的pwm存储器),但它在数学意义上表示pwm引擎可用的所有帧的分数部分的累积值。这种数据排列有效地增加了led显示器图像的灰度范围,易于实现,并且内存使用量的增加并不明显。

41.在一个实施例中,帧缓存器512被一分为二地排列在ping存储器509和pong存储器510中。ping存储器509存储一个20位长的pwm_mi数据的阵列(每个数据服务于一个led)和一个3位长的累加器数据的阵列(每个数据也只服务于一个led)。同样地,在数据排列方面,pong存储器510存储一个20位长的pwm_mi数据的阵列(每个数据服务于一个led),以及一个3位长的累加器数据的阵列(每一个数据也只为一个led服务)。事实上,ping存储器509和pong存储器510的功能是不同的。在一个特定的帧时间中,ping存储器509中的pwm存储器用于触发相应led的显示。同时,pong存储器510正在接收更新的数据。此外,ping存储器509在pwm_mf504(其是新的倍数(m)501和新的pwm502相乘结果的小数部分)上向加法运算513提供诸如506的累加器数据阵列,以产生存储在507中的进位输出值(如有)和存储在508中的剩余分数值。然后,存储在累加器508中的值用于对pong存储器510中的相应累加器进行更新,并且进位输出位507中的值(或者“0”或者“1”)与pwm_mi505相加(即,二进制加法)(运算514)以生成扩展的pwm_mi511,然后将其写入pong存储器510中相应的pwm存储器中。

42.在当前帧完成显示且所有新帧数据完成传输并存储在帧缓存器中时,帧变化信号v

sync

515切换,pong存储器510和ping存储器509的角色发生反转。在角色发生反转时,pong存储器510的pwm存储器用于触发相应的发光二极管的显示,而ping存储器509用于接收即将到来的帧的更新数据。换句话说,pong存储器510向pwm_mf504上的加法运算513提供诸如506的累加器数据阵列,该加法运算513产生存储在507中的进位输出值(如有)和存储在508中的剩余分数值。508用于更新ping存储器509中的相应累加器。存储在505中的新pwm_mi与来自运算513的进位输出位507进行相加(运算514)。加法运算(514)的结果通过511检验并被写入ping存储器509的相应pwm存储器中。当帧改变信号v

sync

515再次切换时,ping存储器509和pong存储器510的角色再次发生反转。本领域的技术人员将会理解,上述ping-pong存储器排列可能有一些变体,它们运用最小内存足迹原则,以有效地实现通过使用记忆来达到的目的。

43.图6示意性地说明了具有动态范围扩展器电路的示例性led显示系统中的 pwm数据处理流程图。新的pwm数据601和倍数(m)值602被输入到二进制乘法器603中。603的乘积被分成整数部分604和分数部分605。分数部分605和累加器 607的内容被输入到二进制加法器606,输出进位608以及求和609。来自606中的求和609存储在累加器607中。进位608被发送到第二个二进制加法器610中,进而与来自乘法器603的整数部分604进行相加。然后,求和611被存储在帧缓存器/pwm存储器(pwm_memory)612中。pwm引擎(pwm_engine)613基于帧缓存器/pwm_memory 612中的pwm数据产生pwm脉冲。来自pwm_engine 613的pwm脉冲对led阵列614进行驱动。

44.值得注意的是,仅当分数的累积值等于或超过1时,才使用分数来点亮led,这也适用于pwm和倍数(m)之间没有乘法的情况。例如,一个脉冲可以均等地处理成八个帧,使得每个帧接收1/8脉冲。将1/8脉冲放入一帧的传统方法需要8倍的时钟速度。相比之下,将一个脉冲放入8帧也只需要1倍的clk速度。

45.受益于前述说明和相关附图中的教义,本领域技术人员将会考虑到本实用新型的许多修改和其他实施例。例如,图像数据(pwm)、倍数(m)和扩展图像数据 (pwm_m)的容量可以扩展或收缩以适应需要和/或环境要求,pwm、pwm_m和m中每个位的指定值可以进行变化以适应个人的偏好,pwm、m和pwm_m的整数部分和分数部分之间的位分配可以根据技术考虑进行调整,用于对pwm_mi中存储值和累加器中存储值之和进行进位调节的阈值可以调整(在所示实施例中,阈值是“1”)为更细微的值(例如“1 1/8”、“1”、“7/8”)以满足技术环境要求,累加器的实现并不是用本说明中指出的寄存器来完成的。这种变化在本实用新型的范围之内。应当理解为本实用新型不限于所披露的具体实施例,并且这些修改和实施例旨在包括在从属权利要求的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1