一种硅光子芯片光耦合结构及其制造方法与流程

1.本发明涉及光学器件技术领域,尤其是涉及一种硅光子芯片光耦合结构 及其制造方法。

背景技术:

2.硅光子技术是基于与微电子集成技术一样的材料,即硅材料,利用现有 与cmos兼容的工艺进行光子器件的开发和集成的新技术,同时也可与电子器 件集成在一起,实现光电子器件集成,综合微电子技术的超大规模集成等优 势和硅光子技术的超高速率、超低功耗等优势,是目前研究和开发的热点之 一。硅光子技术的应用除电信通信和数据通信之外,还包括生物传感、非线 性光学、激光雷达系统、光学陀螺仪,射频集成光电子学,集成无线电收发 器、新型光源、激光降噪、气体传感器、高速微波信号处理等。

3.在硅光子器件的应用过程中不可避免的要实现硅光子芯片与单模光纤的 对准耦合。目前常用的硅光子芯片光耦合方法和结构主要有垂直光栅耦合和 端面耦合。垂直光栅耦合基于布拉格光栅,实现硅光子芯片与光纤近乎90

°ꢀ

耦合;端面耦合则是在硅光子芯片耦合处制作模斑适配器以实现两者的光耦 合。垂直耦合光损耗至少在3db左右,进一步减小光损耗,技术难度很大, 且垂直耦合所需空间结构较大,且是偏振敏感的。垂直光栅耦合无论是光纤 垂直还是水平放置,或者是反射垂直光栅耦合,光耦合效率很难提升到50% 以上,且对光刻精度要求很高。端面耦合,分立式光学镜组耦合,耦合效率 相对较高,但封装体积较大,不便于光芯片集成,且可靠性降低;采用异质 材料做模斑适配器,需要制作尖端光波导,对光刻精度要求较高,且耦合效 率难以提高;多层脊波导或者3d波导,可以提高耦合效率,但目前已有的结 构均是通过大面积刻蚀所形成,该大面积几乎占据晶圆99%的区域,制造时间 久,且刻蚀后的表面和侧壁粗糙度难以控制,导致光传输损耗较大。如中国 专利申请号为2009801361983,名称为用于在硅光子芯片与光纤有效耦合的方 法和设备,即为3d波导结构。

技术实现要素:

4.本发明的目的是提供一种硅光子芯片光耦合结构及其制造方法,解决现 有光耦合结构制造成本高,光传输损耗大的问题。

5.本发明解决其技术问题所采用的技术方案是:本发明解决其技术问题所 采用的技术方案是:一种硅光子芯片光耦合结构,用于传输连续光,包括硅 衬底;所述硅衬底的器件层上设置有硅光子芯片功能结构区域,所述硅光子 芯片功能结构区域上设置有光波导区域和光耦合区;所述光耦合区上设置有 倒脊形沟槽,光耦合区从硅衬底的端面向光波导区域延伸;沿所述倒脊形沟 槽内壁设置有一层隔离层,所述倒脊形沟槽内且位于隔离层的上方设置有倒 脊形光波导层,所述倒脊形光波导层的端面与光纤对接用于接收光波导,另 一端与器件层光波导区域对接用于传输光波导。

6.优选的,所述隔离层的材料为低应力氧化硅,所述倒脊形光波导层的材 料为多晶

硅。

7.具体的,所述倒脊形沟槽从硅衬底的表面向下至少设置有两层沟槽,从 上到下依次为第一沟槽和第二沟槽,所述第一沟槽和第二沟槽的端面宽度不 小于光纤的芯径,所述第一沟槽的另一端与器件层光波导区域对接,与器件 层光波导区域连接处的宽度等于器件层光波导的宽度;所述第二沟槽的长度 不大于第一沟槽的长度,第二沟槽靠近器件层光波导区域一端的宽度大于第 一沟槽靠近光波导区域一端的宽度。

8.优选的,所述倒脊形沟槽从硅衬底的表面向下设置有三层以上沟槽,从 上到下依次为第一沟槽、第二沟槽

……

第n沟槽,其中下一层沟槽的长度不 大于上一层沟槽的长度,从第二沟槽至第n沟槽靠近器件层光波导区域一端 的宽度逐层递增。

9.进一步的,所述倒脊形沟槽为光纤的芯径的1-1.5倍。

10.所述硅衬底上还设置有覆盖在倒脊形光波导层及硅光子芯片功能结构区 域表面的上包层,上下包层的作用是为了将光波局限在倒脊形波导层内传播。

11.优选的,所述上包层的材料为低应力氧化硅。

12.优选的,所述倒脊形沟槽的宽度从硅衬底的端面向器件层光波导区域逐 渐变窄。

13.本发明还公开了一种硅光子芯片光耦合结构的制造方法,包括以下步骤:

14.1)通过干法氧化在硅衬底上形成一层氧化硅层;

15.2)通过等离子体化学气相沉积法在步骤1)的氧化硅层上沉积一层低应 力氧化硅层;

16.3)通过掩膜光刻定义光耦合区的倒脊形光波导的上层脊形区形状,然后 通过干法等离子体刻蚀工艺向下刻蚀并形成倒脊形光波导的第一沟槽;

17.4)通过掩膜光刻,定义光耦合区的倒脊形光波导的第二层脊形区形状, 然后通过干法等离子体刻蚀工艺向下刻蚀并形成倒脊形光波导的第二沟槽; 以与第二沟槽相同的方法刻蚀第三沟槽至第n沟槽;

18.5)干法氧化以平整和光滑上述工艺形成的倒脊形沟槽;然后通过等离子 体沉积法硅衬底表面和倒脊形沟槽内沉积一层低应力氧化硅层;

19.6)通过掩膜光刻去除第一沟槽台阶与器件层光波导区域对接位置处的低 应力氧化硅层;

20.7)在硅衬底表面通过外延工艺生长多晶硅,直到填满整个倒脊形沟槽;

21.8)高温退火,调整外延多晶硅的性质,降低缺陷以达到低传输损耗;

22.9)通过化学机械抛光(cmp)平整硅衬底,cmp后露出洁净的器件层;

23.10)制造硅光功能结构,在光耦合区最终形成多层倒脊形光耦合结构, 并在其上通过等离子体沉积法在硅光子芯片功能结构区域表面上沉积一层低 应力氧化硅层,以形成上包层。

24.为提高倒脊形沟槽侧壁的光滑度,所述步骤5)还包括在干法氧化后,通 过稀释后的氢氟酸hf去掉沟槽的干法氧化层,然后再干法氧化,直到所形成 的倒脊形沟槽侧壁光滑。

25.为提高晶圆表面平整度,所述步骤9)可先通过掩模光刻,以保护光耦合 区的外延多晶硅,然后通过各向同性化学腐蚀多晶硅,实现晶圆表面各区域 高度一致,再通过cmp平整硅衬底。

26.本发明的有益效果:本发明的光耦合结构采用倒脊形结构设计,然后通 过氧化和等离子体沉积一层氧化硅作为隔离层,然后在多层倒脊形沟槽内外 延生长多晶硅进行填充,以作为与硅光子芯片对准耦合的模斑适配结构,可 实现硅光子芯片与单模光纤或激光器芯片的低损耗、无畸变高效率耦合,且 传输损耗低。

27.以下将结合附图和实施例,对本发明进行较为详细的说明。

附图说明

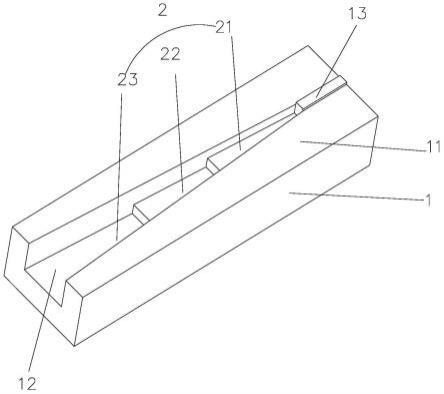

28.图1为本发明采用两层沟槽的立体结构示意图。

29.图2为本发明采用三层沟槽的立体结构示意图。

30.图3为本发明具有三层沟槽的局部纵向剖视图。

31.图4为图3中a-a的剖视图。

32.图5为图3中b-b的剖视图。

33.图6为图3中c-c的剖视图。

34.图7为图3中d-d的剖视图。

35.图8为本发明中在硅衬底上形成氧化硅层的结构示意图。

36.图9为本发明途8氧化硅层上沉积低应力氧化硅层的结构示意图。

37.图10为在低应力氧化硅层上涂布光刻胶的结构示意图。

38.图11为在低应力氧化硅层上形成光刻胶掩膜的结构示意图。

39.图12为通过掩膜光刻工艺形成氧化硅硬掩膜的结构示意图。

40.图13为除去光刻胶后的结构示意图。

41.图14为形成第一沟槽的结构示意图。

42.图15为在第一沟槽和硅光子芯片功能结构区域上沉积低应力氧化硅层的 结构示意图。

43.图16为在低应力氧化硅层上涂布光刻胶的结构示意图。

44.图17为在低应力氧化硅层上形成光刻胶掩膜的结构示意图。

45.图18为形成氧化硅硬掩膜的结构示意图。

46.图19为除去光刻胶的结构示意图。

47.图20为形成第二沟槽的结构示意图。

48.图21为在硅衬底表面和倒脊形沟槽内形成氧化硅层的结构示意图。

49.图22为在氧化硅层上形成一层低应力氧化硅层的结构示意图。

50.图23为去除第一沟槽台阶与器件层光波导区域对接位置处的氧化硅层的 结构示意图。

51.图24为在硅衬底表面生长多晶硅的结构示意图。

52.图25为在光耦合区形成两层结构的倒脊形光波导层的结构示意图。

53.图26为形成上包层的结构示意图。

54.图27为形成第三沟槽的结构示意图。

55.图28为在硅衬底表面和倒脊形沟槽内沉积氧化硅层的结构示意图。

56.图29为去除第一沟槽台阶与器件层光波导区域对接位置处的氧化硅层的 结构示意图。

57.图30为在硅衬底表面生长多晶硅的结构示意图。

58.图31为在光耦合区形成倒脊形光波导层的结构示意图。

具体实施方式

59.实施例1,如图1所示,一种硅光子芯片光耦合结构,用于传输连续光, 包括硅衬底1,所述硅衬底1的器件层上设置有硅光子芯片功能结构区域11, 所述硅光子芯片功能结构区域11上设置有光波导区域13和光耦合区12。所 述光耦合区12上设置有倒脊形沟槽2,光耦合区12从硅衬底1的端面向光波 导区域13延伸;沿所述倒脊形沟槽2内壁设置有一层用于隔离外延多晶硅和 衬底晶圆的硅的隔离层3,所述倒脊形沟槽2内且位于隔离层3的上方设置有 倒脊形光波导层4,所述倒脊形光波导层4的端面与光纤对接用于接收光波导, 另一端与器件层光波导区域13对接用于传输光波导。所述硅衬底1上还设置 有覆盖在倒脊形光波导层4及硅光子芯片功能结构区域11表面的上包层5。 所述上包层5的材料优选采用低应力氧化硅,所述隔离层3的材料优选采用 氧化硅,用于隔离外延多晶硅和衬底晶圆的硅,同时也作为倒脊形波导层4 的下包层,所述倒脊形光波导层4的材料优选采用多晶硅。

60.本实施例的硅衬底以器件层厚度一定的绝缘衬上硅(soi)为例,器件层 厚度可以选用目前常见的220nm、340nm和3μm。并与光纤耦合为例,所述 耦合用光纤均是指标准单模光纤,即芯径为8-9μm的光纤,且端面为平切或 斜8

°

处理。

61.所述倒脊形沟槽2从硅衬底1的表面向下设置有两层沟槽,从上到下依 次为第一沟槽21和第二沟槽22,所述第一沟槽21和第二沟槽22的端面宽度 不小于光纤的芯径,即不小于9μm,所述第一沟槽21的另一端与器件层光波 导区域11对接,与器件层光波导区域11连接处的宽度等于器件层光波导的 宽度;对于220nm的薄器件层,o波段(光波波长1260nm-1360nm)常见的 宽度是500nm,c波段(光波波长1530nm-1565nm)常见的宽度为450nm; 对于3μm的厚器件层,宽度为3μm;所述倒脊形沟槽2的宽度从硅衬底1 的端面向器件层光波导区域11逐渐变窄。所述第一沟槽21的长度不小于1000 μm,所述第二沟槽22的长度不大于第一沟槽21的长度,第二沟槽22靠近 器件层光波导区域11一端的宽度大于第一沟槽21靠近光波导区域13一端的 宽度。所述倒脊形沟槽2的深度不小于9μm,不超过15μm,其中第一沟槽 21的深度不小于3μm,不超过6μm。

62.上述硅光子芯片光耦合结构的制造方法,包括以下步骤:

63.1)通过干法氧化在硅衬底1的器件层上形成一层厚度不超过100nm的氧 化硅层100,如图8所示;

64.2)通过等离子体化学气相沉积法在步骤1)的氧化硅层100上沉积氧化 硅从而形成一层厚度不超过500nm的低应力氧化硅层200,如图9所示;所 述低应力氧化硅层200中的氧化硅是通过等离子体化学气相沉积法制备的, 因此,相比较与干法氧化获得的氧化硅,沉积获得的氧化硅层内应力小,因 此,称之为低应力氧化硅层。该低应力氧化硅层在光耦合区的作用是作为刻 蚀硬掩膜;在其他区域是保护器件层不受后续外延多晶硅的影响。

65.3)在低应力氧化硅层200上涂布一层光刻胶300作为掩膜,光刻胶300 的厚度1.2um-1.3um,如图10所示,然后通过曝光显影形成光刻胶掩膜,如 图11所示;所述光刻胶300可以是正性光刻胶,也可以选用反性光刻胶,根 据不同的光刻胶选择不同形状的掩膜板即可,此处为常规工艺,在此不做详 述说明。

66.通过掩膜光刻工艺以光刻胶为掩膜去除暴露在掩膜外的低应力氧化硅层 200和氧化硅层100,以定义光耦合区的倒脊形光波导的上层脊形区形状400, 如图12所示;利用spm(硫酸和双氧水)去除表面的光刻胶300,如图13 所示;再通过干法等离子体刻蚀工艺并以低应力氧化硅层200为掩膜向下刻 蚀形成倒脊形光波导的第一沟槽21,如图14所示;

67.4)通过等离子体化学气相沉积法在第一沟槽上沉积一层厚度不超过 500nm的低应力氧化硅层200,如图15所示;然后在低应力氧化硅层200上 涂覆一层光刻胶300,如图16所示,通过曝光显影工艺形成光刻胶掩膜,如 图17所示,再通过掩膜光刻工艺去除暴露在掩膜外的低应力氧化硅层200和 氧化硅层100,以定义光耦合区的倒脊形光波导的第二层脊形区500的形状, 如图18所示;然后利用spm(硫酸和双氧水)去除表面的光刻胶,如图19 所示,再通过干法等离子体刻蚀工艺并以低应力氧化硅层200为掩膜向下刻 蚀形成倒脊形光波导的第二沟槽22,如图20所示;

68.5)通过干法氧化以平整和光滑上述工艺形成的倒脊形沟槽2,若通过一 次干法氧化,倒脊形沟槽的表面不够平整光滑,可以先通过稀释后的氢氟酸 hf去掉倒脊形沟槽内的干法氧化层,然后再干法氧化,再次通过稀释后的氢 氟酸hf去掉倒脊形沟槽内的干法氧化层,再次干法氧化,直到所形成的脊形 沟槽1侧壁光滑,如图21所示,所述稀释后的氢氟酸hf浓度为30%-50%; 再通过等离子体沉积法硅衬底表面和倒脊形沟槽内沉积一层厚度不超过 500nm的低应力氧化硅层200,如图22所示;在上述刻蚀形成的脊形沟槽的 作用是作为下包层,以隔离后续外延多晶硅和衬底晶圆的硅。其他区域是保 护器件层不受后续外延多晶硅的影响,同时也作为后续外延多晶硅的去除截 止层。

69.6)通过掩膜光刻去除第一沟槽21台阶与器件层光波导区域对接位置处 的氧化硅层100,如图23所示;所述掩膜光刻可参考步骤3)。

70.7)在硅衬底表面通过外延工艺生长多晶硅600,直到填满整个倒脊形沟 槽,如图24所示;

71.8)高温退火,调整外延多晶硅的性质,降低缺陷以达到低传输损耗;具 体可参考中国专利申请号为cn201710254026.2,名称为一种提高多晶硅锭成 晶率的退火工艺中提及的退火条件参数。

72.9)通过化学机械抛光(cmp)平整硅衬底,cmp后露出洁净的器件层, 在光耦合区12最终形成倒脊形光波导层4,如图25所示;或通过掩模光刻, 以掩膜保护光耦合区的外延多晶硅,然后通过各向同性化学腐蚀多晶硅,实 现晶圆表面各区域高度一致,再通过cmp平整硅衬底。

73.10)在器件层上制造硅光功能结构,并通过等离子体沉积法在硅光子芯 片功能结构区域表面沉积一层厚度不超过500nm的低应力氧化硅层200,以 形成上包层5,如图26所示。如果有电极引出,则需刻蚀出电极窗口区域, 具体工艺非本发明专利的核心,参照半导体制造工艺即可。

74.实施例2:一种硅光子芯片光耦合结构,用于传输连续光,包括硅衬底1, 所述硅衬底1的器件层上设置有硅光子芯片功能结构区域11,所述硅光子芯 片功能结构区域11上设置有光波导区域13和光耦合区12。所述光耦合区12 上设置有倒脊形沟槽2,光耦合区12从硅衬底1的端面向光波导区域13延伸; 沿所述倒脊形沟槽2内壁设置有一层用于隔离外延多晶硅和衬底晶圆的硅的 隔离层3,同时也作为倒脊形波导层4的下包层,所述倒脊形沟槽

2内且位于 隔离层3的上方设置有倒脊形光波导层4,所述倒脊形光波导层4的端面与光 纤对接,另一端与器件层光波导区域13对接。所述硅衬底1上还设置有覆盖 在倒脊形光波导层4及硅光子芯片功能结构区域11表面的上包层5。

75.所述倒脊形沟槽2从硅衬底1的表面向下设置有三层沟槽,从上到下依 次为第一沟槽21、第二沟槽22和第三沟槽23,所述第一沟槽21、第二沟槽 22和第三沟槽23的端面宽度不小于光纤的芯径,即不小于9μm,所述第一沟 槽21的另一端与器件层光波导区域11对接,与器件层光波导区域11连接处 的宽度等于器件层光波导区域13的宽度;所述第一沟槽21的长度不小于1000 μm,所述第二沟槽22的长度不大于第一沟槽21的长度,第三沟槽23的长 度不大于第二沟槽22的长度,第二沟槽22靠近器件层光波导区域11一端的 宽度大于第一沟槽21靠近光波导区域13一端的宽度;第三沟槽23靠近器件 层光波导区域11一端的宽度大于第二沟槽22靠近光波导区域13一端的宽度。 所述倒脊形沟槽2的深度不小于9μm,不超过15μm,其中第一沟槽21的 深度不小于3μm,不超过5μm,第二沟槽22的深度不小于3μm,不超过5 μm。

76.上述硅光子芯片光耦合结构的制造方法,包括以下步骤:

77.1)通过干法氧化在硅衬底1的器件层上形成一层厚度不超过100nm的氧 化硅层100,如图8所示;

78.2)通过等离子体化学气相沉积法在步骤1)的氧化硅层100上沉积一层 厚度不超过500nm的低应力氧化硅层200,如图9所示;

79.3)在低应力氧化硅层200上涂布一层光刻胶300作为掩膜,如图10所 示,然后通过曝光显影工艺形成光刻胶掩膜,如图11所示;

80.通过掩膜光刻工艺以光刻胶为掩膜去除暴露在掩膜外的低应力氧化硅层 200和氧化硅层100,以定义光耦合区的倒脊形光波导的上层脊形区形状400, 如图12所示;使用spm(硫酸和双氧水)去除表面的光刻胶300,如图13 所示;再通过干法等离子体刻蚀工艺并以低应力氧化硅层200为掩膜向下刻 蚀形成倒脊形光波导的第一沟槽21,如图14所示;

81.4)通过等离子体化学气相沉积法在第一沟槽上沉积一层厚度不超过 500nm的低应力氧化硅层200,如图15所示;然后在低应力氧化硅层200上 涂覆一层光刻胶300,如图16所示,通过曝光显影工艺形成光刻胶掩膜,如 图17所示,再通过掩膜光刻工艺去除暴露在掩膜外的低应力氧化硅层200和 氧化硅层100,以定义光耦合区的倒脊形光波导的第二层脊形区500的形状, 如图18所示;然后使用spm(硫酸和双氧水)去除表面的光刻胶,如图19 所示,再通过干法等离子体刻蚀工艺并以低应力氧化硅层200为掩膜向下刻 蚀形成倒脊形光波导的第二沟槽22,如图20所示;以第二沟槽22相同的工 艺进行刻蚀在第二沟槽22的下方形成第三沟槽23,如图27所示;

82.5)干法氧化以平整和光滑上述工艺形成的倒脊形沟槽2;再通过等离子 体沉积法于倒脊形沟槽内沉积一层厚度不超过500nm的低应力氧化硅层200, 如图28所示;

83.6)通过掩膜光刻去除第一沟槽21台阶与器件层光波导区域对接位置处 的氧化硅层100和低应力氧化硅层200,如图29所示;

84.7)在硅衬底表面通过外延工艺生长多晶硅600,直到填满整个倒脊形沟 槽,如图30所示;

85.8)高温退火,调整外延多晶硅的性质,降低缺陷以达到低传输损耗;

86.9)通过化学机械抛光(cmp)平整硅衬底,cmp后露出洁净的器件层, 在光耦合区12最终形成倒脊形光波导层4,如图31所示;

87.10)在器件层上制造硅光功能结构,并通过等离子体沉积法在硅光子芯 片功能结构区域表面沉积一层厚度不超过500nm的低应力氧化硅层200,以 形成上包层5,如图3所示。其他同实施例1。

88.以上结合附图对本发明进行了示例性描述。显然,本发明具体实现并不受 上述方式的限制。只要是采用了本发明的方法构思和技术方案进行的各种非 实质性的改进;或未经改进,将本发明的上述构思和技术方案直接应用于其 它场合的,均在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1