一种抛物线型波导高效光栅耦合器及其设计方法

1.本发明属于集成光电子技术领域,具体涉及一种抛物线型波导高效光栅耦合,还涉及该光栅耦合器的设计方法。

背景技术:

2.随着光通信领域科学技术的进步,对集成化程度的要求逐渐提高,集成光波导器件以其体积小、高性能、低成本的独特优势成为光通信产业的研究热点。目前,常见的集成光波导器件主要有光栅耦合器、光分路器、星型耦合器等。波导器件在与光纤系统进行光路互联时,两者之间较大的模场失配将产生较大的损耗,严重影响通信效率和通信链路的可靠性。

3.解决模场失配问题使用较多的方法有端面直接耦合、波导光栅耦合等,端面耦合对准难度较大,对光刻技术的精度要求极高,并且只能制作在波导芯层边缘,无法实现其他位置光的耦合。而光栅耦合器被刻蚀在光波导上,具有有效接收面积大、对准容差大、可进行片上测试等优点,已经成为解决光纤与波导耦合模场失配问题最主要的方案之一。

4.传统矩形光栅耦合器存在着耦合效率低、工作带宽窄、偏振敏感等问题,目前解决这些问题的主要方案有:通过引入变迹光栅或啁啾光栅打破传统结构的对称性进而提高耦合效率;引入亚波长结构改变光栅的有效折射率从而增大光栅带宽;采用二维光栅耦合器实现偏振分离的功能等,但是这些结构的耦合器大多制备起来较为复杂且耦合效率较低,因此对于提升光栅耦合器的性能还有待研究。

技术实现要素:

5.本发明的目的在于提供一种抛物线型波导高效光栅耦合器,解决了现有光栅耦合器耦合效率低的问题。

6.本发明的目的还在于提供一种抛物线型波导高效光栅耦合器的设计方法。

7.本发明所采用的第一种技术方案是:一种抛物线型波导高效光栅耦合器,包括依次从下往上的硅衬底、理想电导体pec、绝缘层和顶硅层,绝缘层为二氧化硅,顶硅层为波导区域,波导区域中的光栅区域中刻蚀有周期性的抛物线型波导结构。

8.绝缘层厚度为2.5μm;理想电导体pec厚度为0.5μm;顶硅层的波导区域的高度h为0.32μm,光栅区域刻蚀深度e为0.08μm。

9.抛物线型波导的开口宽度为x,高度为y,si的占空比x/p=0.66,p是周期。

10.本发明的特点还在于,

11.本发明所采用的第二种技术方案是:一种抛物线型波导高效光栅耦合器的设计方法,具体操作步骤如下:

12.步骤s1:建立光栅耦合器结构模型,所述光栅耦合器结构模型从下往上依次为硅衬底、理想电导体pec、二氧化硅绝缘层和顶硅层,其中顶硅层作为波导区域;

13.步骤s2:在顶硅层的光栅区域刻蚀抛物线型波导,得到抛物线型波导光栅耦合器;

14.步骤s3:调整波导区域的高度和光栅区域的周期、刻蚀深度,确定光栅耦合器的最优结构参数。

15.本发明的特点还在于,

16.步骤s1中,采用时域有限差分法建立光栅耦合器结构模型,所述波导区域的高度为0.32μm,绝缘层厚度为2.5μm,理想电导体pec厚度为0.5μm。

17.步骤s2中,所述抛物线型波导光栅耦合器的光源从波导左端激发,采用te偏振入射光。

18.步骤s3中,在光源处及光栅上方1.1μm处设置功率监视器,用来收集输入与输出波导光栅的功率,耦合器的耦合效率为输出功率与输入功率之比。

19.步骤s3中的最优结构参数为:抛物线型波导的开口宽度为x,高度为y,si的占空比x/p=0.66,p是光栅区域的周期。

20.本发明的有益效果是,

21.本发明提供了一种抛物线型波导高效光栅耦合器的设计方法,该方法将光栅区域设计为抛物线型,使光栅表面的折射率发生渐变,在一定程度上改变光的传输方向。在二氧化硅与硅衬底之间加入理想电导体材料,形成反射镜结构,从而增加底部的反射率。在此基础上,通过调整波导区域高度与光栅区域的刻蚀深度,提高光栅耦合器的耦合效率。最后对光栅占空比进一步优化,得到在1550nm波长附近,耦合效率最大为85.1%。

附图说明

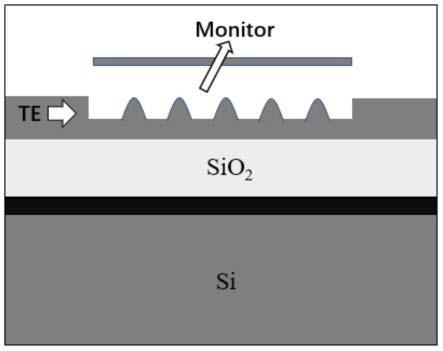

22.图1是本发明实施例中抛物线型光栅耦合器的结构示意图;

23.图2(a)是本发明实施例中对应波导区域的高度为0.32μm,光栅区域不同刻蚀深度对耦合性能的影响示意图;

24.图2(b)是本发明实施例中对应波导区域的高度为0.34μm,光栅区域不同刻蚀深度对耦合性能的影响示意图;

25.图2(c)是本发明实施例中对应波导区域的高度为0.36μm,光栅区域不同刻蚀深度对耦合性能的影响示意图;

26.图3是本发明实施例中光栅周期对光栅耦合效率的影响示意图;

27.图4是本发明实施例中不同硅占空比对光栅耦合效率的影响示意图。

具体实施方式

28.为了使本发明的目的、技术方案更加清楚明白,以下结合附图及实施例,对本发明进一步详细说明。

29.本发明的理想电导体pec可以将向下衍射的光反射回光栅结构,提高反射面的反射率,进而增大光栅耦合器的耦合效率。

30.本发明的抛物线型光栅结构构成了一种折射率渐变的结构,提高了耦合效率。本发明的一种抛物线型波导高效光栅耦合器,如图1所示,包括依次从下往上的硅衬底、理想电导体pec、绝缘层和顶硅层,绝缘层为二氧化硅,顶硅层为波导区域,波导区域中的光栅区域中刻蚀有周期性的抛物线型波导结构。

31.绝缘层厚度为2.5μm;理想电导体pec厚度为0.5μm;顶硅层的波导区域的高度h为

0.32μm,光栅区域刻蚀深度e为0.08μm。

32.抛物线型波导的开口宽度为x,高度为y,si的占空比x/p=0.66,p是周期。

33.本发明提供了一种新型抛物线波导高效光栅耦合器设计方法,具体包括以下步骤:

34.步骤s1:利用时域有限差分(fdtd)方法建立光栅耦合器结构模型,光栅耦合器结构模型基于硅-绝缘层-硅三明治型的soi结构进行设计,选择合适的硅衬底厚度、光栅周期、刻蚀宽度、刻蚀深度,光源的模式、入射方向、光源与光栅的距离等参数,设计一种用于波导和光纤之间的输入输出耦合器。在1500nm波长的入射光下,si材料的折射率为3.476,sio2的折射率为1.444,空气的折射率设为1。

35.在本实施例中,入射光采用波长为1500nm-1600nm的te模式偏振光,绝缘层为2.5μm厚度的sio2材料,理想电导体(pec)厚度为0.5μm,波导区域的高度h为0.32μm,光栅区域刻蚀深度e为0.08μm。

36.步骤s2:在顶硅层的光栅区域中刻蚀抛物线结构,如图1所示,光栅区域由周期性的抛物线型波导结构组成,其周期p为0.58μm,抛物线型波导的开口宽度为x,高度为y,si的占空比x/p=0.71。

37.步骤s3:将波导区域的高度分别调整为0.32μm、0.34μm、0.36μm,分析1500nm-1600nm波长下不同光栅刻蚀深度对整体耦合效率的影响。如图2所示,(a)、(b)、(c)分别对应波导区域的高度为0.32μm、0.34μm、0.36μm。

38.在图2(a)中,当光栅区域刻蚀深度为0.08μm时,在1560nm波长附近,最大耦合效率为85.49%。在图2(b)中,当光栅区域刻蚀深度为0.1μm时,在1550nm-1580nm波长范围内,耦合效率均高于82%,并且在1570nm波长附近达到最大耦合效率为84.9%。在图2(c)中,当光栅区域刻蚀深度为0.12μm时,在1570nm波长附近达到最大耦合效率为84.4%。

39.进一步,在波导区域高度为0.32μm,光栅区域刻蚀深度为0.08μm时,分析光栅周期从0.5μm变化至0.6μm,以0.01μm为步长均匀变化时,光栅耦合效率的变化情况,结果如图3所示,从图中可以看出,当光栅周期在0.55μm-0.59μm之间时,耦合效率均高于80%,并且当周期为0.57μm时,耦合效率最大为84.2%。

40.最后,基于前面所述最大耦合效率的结构,对光栅区域的占空比进行优化,如图4所示,分别为0.66、0.68、0.7三个占空比,在1500nm-1600nm波长下耦合效率的变化。可以看出,当占空比为0.66时,在1550nm波长附近,最大耦合效率为85.1%。

41.综上所述,本发明提出了一种新型抛物线波导高效光栅耦合器设计方法,针对目前光纤与波导耦合效率较低的问题,设计了一种抛物线型波导光栅耦合器,提高了波导芯片的耦合效率,且该结构灵活性和适用性更强,应用前景广阔。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1