一种砷化镓基LED芯片透明导电层测试点的制备方法与流程

一种砷化镓基led芯片透明导电层测试点的制备方法

技术领域

1.本发明涉及一种砷化镓基led芯片透明导电层测试点的制备方法,属于半导体加工技术领域。

背景技术:

2.砷化镓基led管芯结构一般是由衬底、外延层、透明导电层(tcl)、电极层组成,整个制作过程较为繁杂。使用砷化镓衬底进行led管芯电极的制作时,因为制作整个工艺的复杂性、制作工步繁琐性以及人员操作的不可控性等因素,总会避免不了产生一些wafer参数异常、晶片表面异常、区域性污染等异常晶片,尤其是wafer参数异常较为常见,该种异常大多数是由tcl膜层导电异常导致。这样我们就需要在tcl膜层制作后及时的知道该膜层是否合格成为降低管芯损失的关键。较为常见的方式是tcl膜层制作完成后,通过在光刻板上制作的特殊测试点,然后在tcl膜层上通过光刻胶进行掩膜图形的保护,将测试点图形腐蚀出来,这样tcl膜层制作后电极制作前就能通过度测试点的测试而验证处tcl膜层以及tcl膜层与外延层之间的接触情况,以此来判断该段时间内或者同炉次制作的tcl膜层的质量水平,进而避免不必要的损失。

3.从该作业方式来看,在现有的tcl膜层制备过程中必须进行一次额外的光刻作业,在此次额外的光刻作业中需要使用酸性溶液去除测试点处的tcl膜层,且腐蚀过程中容易对周围区域的tcl膜层产生侧蚀,这样不仅增大了的作业风险,而且大大增加了制作成本,降低了作业效率。另外,也有通过剥离tcl膜层的方法制作测试点,即在tcl膜层蒸镀(溅射前)首先将测试点区域制作上光刻胶,然后通过低温制作tcl膜层后,再使用有机溶剂通过剥离方式将测试点剥离出来,同样需要一次光刻和一次去胶,但不需要进行额外腐蚀,安全性上占优势,但是工步同样繁琐和效率低下,成本较高。

4.中国专利文件cn106711305a公开了一种led芯片sputter-ito腐蚀工艺,其具体步骤为:(1)选取外延片,清洗后进行p-sio2制程,光刻出所需图形;(2)通过浸泡boe溶液化学湿法腐蚀sio2,去除光刻胶再进行酸洗、甩干;(3)进行sputter-ito溅镀,然后进行黄光光刻所需图形;(4)化学湿法蚀刻后,清洗完成后甩干,进行icp刻蚀,去除光刻胶后清洗、甩干;(5)再进行rta高温退火融合;(6)然后进行钝化sio2层的沉积、pn黄光光刻,金属蒸镀后去除光刻胶,再金属融合,最后完成点测。该发明方法可以降低ito过腐蚀的风险,在完成ito膜层后先进行黄光光刻,再固定ito的腐蚀时间,这样就避免了ito膜过腐蚀的所造成的的腐蚀过现象。该方法为常见的tcl腐蚀作业方法,不仅对常规图形可以制作同样可以适用于测试点图形的制作,不过需要提前再光刻板上设计出测试点并且进行单独一次腐蚀方可制作完成。

5.根据以上分析,鉴于目前tcl膜层上测试点制作的弊端,有必要研究一种基于tcl膜层的不进行腐蚀的测试点的制作的工艺方法,以此提高产品质量,降低异常风险。

技术实现要素:

6.针对现有砷化镓基led管芯制作中透明导电层上测试点制作方法的弊端,本发明提供了一种砷化镓基led芯片透明导电层测试点的制备方法。

7.本发明的技术方案如下:

8.一种砷化镓基led芯片透明导电层测试点的制备方法,包括步骤如下:

9.(1)取在砷化镓衬底上生长有外延结构的晶片,备用;

10.(2)取设置有镂空测试点图形的遮挡膜,将遮挡膜粘附在步骤(1)中的晶片上;

11.(3)将步骤(2)中的晶片进行透明导电层的制备,透明导电层的制备完成后去除遮挡膜,即得带有透明导电层测试点的砷化镓基led芯片。

12.根据本发明优选的,步骤(1)中所述外延结构是生长在砷化镓衬底上的膜层,从衬底到上依次为,砷化镓衬底、n型砷化镓欧姆接触层、n型砷化镓限制层、量子阱有源层、p型限制层、p型砷化镓欧姆接触层、p型磷化镓窗口层。

13.根据本发明优选的,步骤(2)中所述镂空测试点图形的个数为2~4个。

14.根据本发明优选的,步骤(2)中所述镂空测试点图形包括但不限于圆形、矩形或菱形。可以根据实际需求进行调整。

15.根据本发明优选的,步骤(2)中所述遮挡膜为耐高温粘性膜,材质为聚酰亚胺硅胶,耐温温度在400℃以上。

16.根据本发明优选的,步骤(2)中所述遮挡膜的厚度为1~3mm。

17.根据本发明优选的,步骤(3)中所述透明导电层按照电子束蒸发或溅射蒸镀的方法制备。

18.根据本发明优选的,步骤(3)中所述透明导电层的材料为ito、izo、igzo、azo或其他氧化物透明导电膜材料。

19.本发明有益效果:

20.1、本发明通过在制作透明导电层前,使用设置有镂空测试点图形的遮挡膜贴附于晶片的表面,以此来获得合适大小的测试点图形,这样就避免了透明导电层制作过程中的正面膜层的产生,不需要进行额外的腐蚀,就得到了所需要的测试点,透明导电层制作完成后可以直接进行测试点的测试,方法简便,同时达到了测试点的制作效果。该放方法与光刻板制作掩膜的方式类似,但存在本质上的差异,首先光刻板无法直接用于透明导电层的镀膜设备上,另外使用光刻板必须使用腐蚀的方法,而本发明方法既不需要额外测试点的制作也不需要腐蚀,使测试点的制作变得更为简便,且根据晶片尺寸以及外延结构的需求可以及时更换遮挡膜的图形以及大小,成本几乎可以忽略。

21.2、本发明中,遮挡膜材料的选择较为重要,因为要使用在透明导电层的制作上,因为制作设备的特殊性,那么常规的磁性材料、非耐高温、易挥发、易氧化材料等均不合适,经过本发明人通过对大量材料的选择,最后确认耐高温的粘性膜是最合适的,且成本低,容易更换,和图形的设计。

22.3、本发明的制作方法,操作步骤简便,原理简单易懂,测试的i-v曲线与最终管芯wafer光电参数vf1(正向电压)能够完全对应,可以应用于所有led表面tcl膜层的测试点的制作。

附图说明

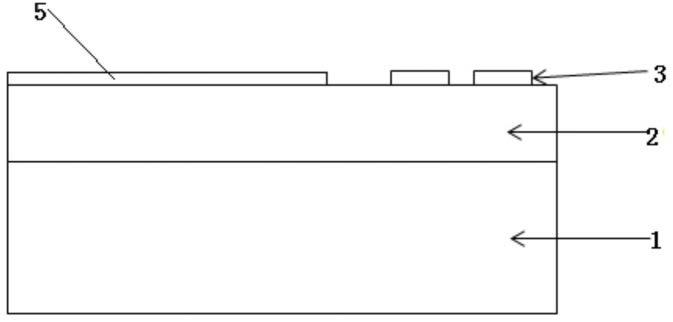

23.图1为砷化镓基led芯片透明导电层测试点制备完成后的晶片剖面图;

24.图2为本发明中遮挡膜俯视图;

25.图3本发明中砷化镓基led芯片透明导电层粘附遮挡膜的晶片俯视图;

26.图4为实施例中砷化镓基led芯片透明导电层测试点制备完成后的晶片的i-v曲线图。

27.横坐标为电压,纵坐标为电流。

28.图中:1、砷化镓衬底;2、外延结构;3、测试点;4、遮挡膜;5、透明导电层。

具体实施方式

29.以下说明中使用的为光电参数测试仪器为台湾惠特科技生产的光电参数测试台,型号为ipt6000。

30.下面结合实施例和附图对本发明做进一步说明,但不限于此。

31.实施例1

32.一种砷化镓基led芯片透明导电层测试点的制备方法,包括步骤如下:

33.(1)取在砷化镓衬底上生长有外延结构的晶片,备用;

34.(2)取设置有两个圆形镂空测试点图形的遮挡膜,将遮挡膜粘附在步骤(1)中的晶片上;

35.(3)将步骤(2)中的晶片按照电子束蒸发法进行透明导电层的制备,透明导电层的制备完成后去除遮挡膜,即得带有透明导电层测试点的砷化镓基led芯片。

36.步骤(1)中所述外延结构是生长在砷化镓衬底上的膜层,从衬底到上依次为,砷化镓衬底、n型砷化镓欧姆接触层、n型砷化镓限制层、量子阱有源层、p型限制层、p型砷化镓欧姆接触层、p型磷化镓窗口层。

37.步骤(2)中所述遮挡膜为聚酰亚胺硅胶带,厚度为1mm。

38.步骤(3)中所述透明导电层的材料为ito。

39.本实施例制备的砷化镓基led芯片透明导电层测试点制备完成后的晶片剖面图,如图1所示;遮挡膜俯视图,如图2所示;砷化镓基led芯片透明导电层测试点制备完成后的俯视图,如图3所示。

40.实施例2

41.一种砷化镓基led芯片透明导电层测试点的制备方法,包括步骤如下:

42.(1)取在砷化镓衬底上生长有外延结构的晶片,备用;

43.(2)取设置有四个圆形镂空测试点图形的遮挡膜,将遮挡膜粘附在步骤(1)中的晶片上;

44.(3)将步骤(2)中的晶片按照电子束蒸发法进行透明导电层的制备,透明导电层的制备完成后去除遮挡膜,即得带有透明导电层测试点的砷化镓基led芯片。

45.步骤(1)中所述外延结构同实施例1。

46.步骤(2)中所述遮挡膜为聚酰亚胺硅胶带,厚度为3mm。

47.步骤(3)中所述透明导电层的材料为ito。

48.实施例3

49.一种砷化镓基led芯片透明导电层测试点的制备方法,包括步骤如下:

50.(1)选取在砷化镓衬底上生长有外延结构的晶片,备用;

51.(2)取设置有两个正方形镂空测试点图形的遮挡膜,将遮挡膜粘附在步骤(1)中的晶片上;

52.(3)将步骤(2)中的晶片按照溅射蒸镀法制备进行透明导电层的制备,透明导电层的制备完成后去除遮挡膜,即得带有透明导电层测试点的砷化镓基led芯片。

53.步骤(1)中所述外延结构同实施例1。

54.步骤(2)中所述遮挡膜为聚酰亚胺硅胶带,厚度为2mm。

55.步骤(3)中所述透明导电层的材料为izo。

56.对比例

57.一种砷化镓基led芯片透明导电层测试点的制备方法,步骤同实施例1,不同之处在于,步骤(2)中所述遮挡膜材质为普通塑料胶带,材质为聚丙烯。

58.在本对比例蒸镀透明导电层过程中发生有机物挥发,蒸镀处的透明导电层杂质较多,使得透明导电层电阻较高,透过率低,影响性能。

59.试验例

60.对实施例1中砷化镓基led芯片透明导电层测试点制备完成后的晶片进行欧姆接触测试。使用的仪器为ipt6000光电参数测试台。

61.具体方法如下:扎测两个测试点间的i-v曲线。测试时,电压从-1v到1v,限制电流100ma测试结果如图4所示。

62.由图4可知,实施例1中砷化镓基led芯片透明导电层测试点制备完成后的晶片的i-v曲线为直线,说明接触良好,无异常。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1