基于差值比较法的芯片ESD二极管工艺缺陷检测方法与流程

基于差值比较法的芯片esd二极管工艺缺陷检测方法

技术领域

[0001]

本发明属于芯片性能测试技术领域,具体涉及一种基于差值比较法的芯片esd二极管工艺缺陷检测方法的设计。

背景技术:

[0002]

静电放电(electro-static discharge,esd)是造成大多数电子元器件、芯片或集成电路性能失效的主要原因。因为静电产生的瞬间电压通常可达到几千伏甚至更高,高电压对于芯片等器件的损伤是永久性的、不可恢复的,会直接导致芯片里面电路结构烧毁。基于此原因,芯片制造厂商推出esd保护二极管模型,用于对静电的泄放,起到保护内部电路的作用。芯片设计师只需要在相应的端口加入esd保护二极管就能够防止静电对芯片的损伤。

[0003]

由于各个芯片制造厂商的工艺以及能力参差不齐,在esd二极管制造过程中,会存在一些技术缺陷,使得esd二极管实测导通电压或击穿电压出现一定概率的偏低而导致器件失效,这种性能异常的esd二极管会降低对芯片电路的保护能力,增加芯片被静电损伤的风险,如果此类芯片用于系统,会造成系统抗风险能力的降低,且发生故障时不易定位。

[0004]

目前常规的芯片性能测试,比如开路短路测试,只能测试芯片端口存在开路或者短路的异常情况,无法筛测正向esd保护二极管导通电压偏低或反向esd保护二极管击穿电压偏低的芯片;同时如果采用典型的单点电压电流(iv)判定方法,因为采用单点测试,受到芯片量产测试的正常波动值的影响较大,判别精度较差,因此容易造成误判。

技术实现要素:

[0005]

本发明的目的是为了解决现有芯片性能测试方法不能将二极管导通电压或击穿电压异常芯片完全筛选出来的问题,提出了一种基于差值比较法的芯片esd二极管工艺缺陷检测方法,以筛选出esd二极管导通电压或击穿电压异常的芯片。

[0006]

本发明的技术方案为:基于差值比较法的芯片esd二极管工艺缺陷检测方法,包括以下步骤:

[0007]

s1、在待测芯片的vdd端口内部连接一个反向esd二极管m1以及5个正向esd二极管m2-m6。

[0008]

s2、在待测芯片的vdd端口接入电压v

d1

,保持待测芯片的其余端口开路,电源限流i

limit

。

[0009]

s3、判断待测芯片电流是否超过电源限流值i

limit

,若是则记录芯片电流值i

d1m

并进入步骤s5,否则进入步骤s4。

[0010]

s4、将芯片电流超过电源限流值i

limit

的待测芯片归入失效芯片集合bin3。

[0011]

s5、在待测芯片的vdd端口接入电压v

d2

,并记录芯片电流值i

d2m

。

[0012]

s6、根据芯片电流值i

d1m

和i

d2m

计算电流差值δi

d

。

[0013]

s7、判断电流差值δi

d

是否在预设标准值范围内,若是则进入步骤s8,否则进入步

骤s9。

[0014]

s8、将电流差值δi

d

在预设标准值范围内的待测芯片归入合格芯片集合bin1。

[0015]

s9、将电流差值δi

d

不在预设标准值范围内的待测芯片归入失效芯片集合bin2。

[0016]

进一步地,步骤s1中正向esd二极管m2-m6按照阴极-阳极的形式依次串联,正向esd二极管m2的阳极以及反向esd二极管m1的阴极均与待测芯片的vdd端口连接,正向esd二极管m6的阴极以及反向esd二极管m1的阳极均接地。

[0017]

进一步地,步骤s6中电流差值δi

d

的计算公式为:

[0018]

δi

d

=δi

d2-δi

d1

=(i

d2a-i

d2m

)-(i

d1a-i

d1m

)

[0019]

其中δi

d1

表示第一中间电流差值,δi

d2

表示第二中间电流差值,i

d1a

表示系统设置的芯片标准件在电压v

d1

时的测试值,i

d2a

表示系统设置的芯片标准件在电压v

d2

时的测试值。

[0020]

进一步地,步骤s7中电流差值δi

d

的预设标准值范围为:i

low

<δi

d

<i

high

,其中i

low

表示预设的卡控门限最小值,i

high

表示预设的卡控门限最大值。

[0021]

进一步地,合格芯片集合bin1为esd二极管导通电压或击穿电压在正常范围内的芯片集合,失效芯片集合bin2为esd二极管导通电压或击穿电压低于或高于标准值的芯片集合,失效芯片集合bin3为端口特性异常的芯片集合。

[0022]

本发明的有益效果是:

[0023]

(1)本发明采用的差值法可以显著遏制芯片量产测试的正常波动对于量产测试的干扰作用,有效拦截了esd二极管导通电压或击穿电压异常的芯片。

[0024]

(2)本发明采用两点iv的测试方法,测试速度快,测试环境简单。

附图说明

[0025]

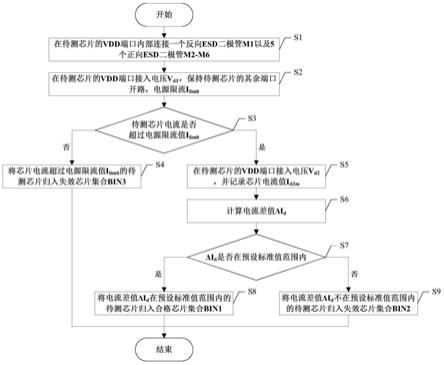

图1所示为本发明实施例提供的基于差值比较法的芯片esd二极管工艺缺陷检测方法流程图。

[0026]

图2所示为本发明实施例提供的待测芯片端口示意图。

[0027]

图3所示为本发明实施例提供的性能正常与异常的esd二极管iv曲线示意图。

具体实施方式

[0028]

现在将参考附图来详细描述本发明的示例性实施方式。应当理解,附图中示出和描述的实施方式仅仅是示例性的,意在阐释本发明的原理和精神,而并非限制本发明的范围。

[0029]

本发明实施例提供了一种基于差值比较法的芯片esd二极管工艺缺陷检测方法,如图1所示,包括以下步骤s1~s9:

[0030]

s1、在待测芯片的vdd端口内部连接一个反向esd二极管m1以及5个正向esd二极管m2-m6。

[0031]

本发明实施例中,待测芯片以图2所示的芯片为例,共有12个管脚,其中pin2管脚作为输入端口rfin,pin8管脚作为输出端口rfout,pin11管脚作为vdd端口。将vdd端口作为待测端口,在其内部连接一个反向esd二极管m1以及5个正向esd二极管m2-m6。

[0032]

本发明实施例中,如图2所示,正向esd二极管m2-m6按照阴极-阳极的形式依次串

联,正向esd二极管m2的阳极以及反向esd二极管m1的阴极均与待测芯片的vdd端口连接,正向esd二极管m6的阴极以及反向esd二极管m1的阳极均接地。

[0033]

当待测端口加上不同的电压时,由于esd二极管工艺缺陷会导致其导通电压或击穿电压降低,造成二极管提前开启或者击穿,会得到如图3所示的iv曲线图,基于此原理即可筛选出esd二极管性能异常的芯片。

[0034]

s2、在待测芯片的vdd端口接入电压v

d1

,保持待测芯片的其余端口开路,电源限流i

limit

。

[0035]

s3、判断待测芯片电流是否超过电源限流值i

limit

,若是则记录芯片电流值i

d1m

并进入步骤s5,否则进入步骤s4。

[0036]

s4、将芯片电流超过电源限流值i

limit

的待测芯片归入失效芯片集合bin3。

[0037]

s5、在待测芯片的vdd端口接入电压v

d2

,并记录芯片电流值i

d2m

。

[0038]

s6、根据芯片电流值i

d1m

和i

d2m

计算电流差值δi

d

。

[0039]

如图3所示,电流差值δi

d

的计算公式为:

[0040]

δi

d

=δi

d2-δi

d1

=(i

d2a-i

d2m

)-(i

d1a-i

d1m

)

[0041]

其中δi

d1

表示第一中间电流差值,δi

d2

表示第二中间电流差值,i

d1a

表示系统设置的芯片标准件在电压v

d1

时的测试值,i

d2a

表示系统设置的芯片标准件在电压v

d2

时的测试值。

[0042]

s7、判断电流差值δi

d

是否在预设标准值范围内,若是则进入步骤s8,否则进入步骤s9。

[0043]

本发明实施例中,电流差值δi

d

的预设标准值范围为:i

low

<δi

d

<i

high

,其中i

low

表示预设的卡控门限最小值,i

high

表示预设的卡控门限最大值。

[0044]

s8、将电流差值δi

d

在预设标准值范围内的待测芯片归入合格芯片集合bin1。

[0045]

s9、将电流差值δi

d

不在预设标准值范围内的待测芯片归入失效芯片集合bin2。

[0046]

本发明实施例中,合格芯片集合bin1为esd二极管导通电压或击穿电压在正常范围内的芯片集合,失效芯片集合bin2为esd二极管导通电压或击穿电压低于或高于标准值的芯片集合,失效芯片集合bin3为端口特性异常的芯片集合。

[0047]

本领域的普通技术人员将会意识到,这里所述的实施例是为了帮助读者理解本发明的原理,应被理解为本发明的保护范围并不局限于这样的特别陈述和实施例。本领域的普通技术人员可以根据本发明公开的这些技术启示做出各种不脱离本发明实质的其它各种具体变形和组合,这些变形和组合仍然在本发明的保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1