一种参差脉冲波形产生的方法及系统与流程

[0001]

本发明涉及雷达信号发射领域的波形产生技术。更具体地,涉及一种参差脉冲波形产生方法及系统。

背景技术:

[0002]

伴随战场环境日益复杂,雷达技术突飞猛进,雷达发射信号在实际应用中也逐渐呈现多样化、复杂化,一方面复杂的雷达发射信号能够满足更多的应用场景,在较为复杂的场景中发挥更高的效用;另一方面复杂的雷达发射信号在实际应用中不易受到干扰,同时具有更好的保密效果。

[0003]

现有的雷达发射信号技术往往有以下几个缺陷:一是波形种类单一,同一个驻留周期内往往只有一种类型的波形,一般以单载频和线性调频居多;二是同一驻留周期内一般以单脉冲或者等prt周期的脉冲串居多,脉冲参差的波形并不多见,尤其对于不同波形种类,不同波形参数的参差波形更是很少见,但是伴随后续应用的多样化,对于同驻留周期内参差脉冲波形的研究是十分必要的。

技术实现要素:

[0004]

本发明的一个目的在于提供解决上述问题至少之一的一种参差脉冲波形产生方法及系统。

[0005]

为达到上述目的,本发明采用下述技术方案:

[0006]

一方面,本发明提供一种参差脉冲波形产生方法。

[0007]

该方法包括:

[0008]

s1:信号源和时钟分发芯片用于时钟分发,为fpga芯片和dac芯片提供基础时钟;

[0009]

s2:上位机通过单模光纤发布控制信息至所述fpga芯片;

[0010]

s3:所述fpga芯片接收所述控制信息,根据所述控制信息中包含的时序信息和波形信息输出基带波形信号;

[0011]

s4:所述dac芯片接收所述基带波形信号,将其转换为模拟信号;

[0012]

所述fpga芯片包括gtx接口模块、控制字解析模块、时序同步信号产生模块、波形参数管理模块、波形产生模块、dac接口模块和时钟分配和监测模块。

[0013]

所述gtx接口模块用于接收所述控制信息,完成数据的串并转换,输出基准脉冲和控制参数。

[0014]

所述控制字解析模块解析所述控制参数,输出解析得到的时序参数和波形参数。

[0015]

所述时序同步信号产生模块根据所述时序参数以及基准脉冲产生具体的时序脉冲信号

[0016]

所述波形参数管理模块根据所述时序脉冲信号,在对应时间段根据所述时序脉冲信号输出对应的波形参数。

[0017]

所述波形产生模块根据所述波形参数输出具体的基带波形信号。

[0018]

所述dac接口模块将基带波形信号传输至所述dac芯片,由所述dac芯片将数字信号转换为模拟信号,并根据波形参数的上变频频率在dac芯片内部完成上变频操作,将基带波形信号上变频至中频信号输出。

[0019]

所述时钟分配和监测模块接收所述信号源提供的时钟信号,为fpga芯片提供基础时钟。

[0020]

另一方面,本发明公开了一种参差脉冲波形产生的系统,所述系统包括:

[0021]

控制单元,用于下发控制信息,所述控制信息包括时序信息和波形信息;

[0022]

信号产生单元,用于根据所述控制信息输出基带波形信号;

[0023]

数模转换单元,接收所述基带波形信号并将其转换为模拟信号;

[0024]

基准单元,用于为所述信号产生单元和所述数模转换单元提供基准信号。

[0025]

所述信号产生单元包括:

[0026]

gtx接口模块、控制字解析模块、波形参数管理模块、时序同步信号产生模块、波形产生模块和dac接口模块;

[0027]

所述基准单元包括信号源、时钟分发芯片以及时钟分配和监测模块。

[0028]

本发明提出了一种参差脉冲波形产生方法及系统,解决了现有雷达发射信号同驻留周期内波形种类单一,脉冲间波形不可调的缺陷。

附图说明

[0029]

为了更清楚地说明本发明实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

[0030]

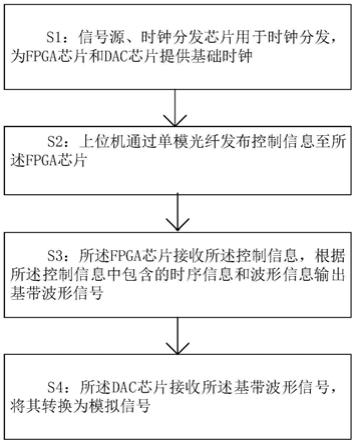

图1示出一种参差脉冲波形产生的方法的示意图;

[0031]

图2使出一种参差脉冲波形产生的方法的具体模板示意图;

[0032]

图3示出一种参差脉冲波形产生的系统的示意图。

具体实施方式

[0033]

为使本发明的、技术方案和优点更加清楚,下面将结合附图对本发明实施方式作进一步地详细描述。

[0034]

需要说明的是附图中相似的部件以相同的附图标记进行表示。本领域技术人员应当理解,下面所具体描述的内容是说明性的而非限制性的,不应以此限制本发明的保护范围。

[0035]

一方面,本发明的一个实施例提供了一种参差脉冲波产生的方法。

[0036]

根据本发明的示例性实施例,如图1所示,包括

[0037]

s1:信号源、时钟分发芯片用于时钟分发,为fpga芯片和dac芯片提供基础时钟;

[0038]

s2:上位机通过单模光纤发布控制信息至所述fpga芯片;

[0039]

s3:所述fpga芯片接收所述控制信息,根据所述控制信息中包含的时序信息和波形信息输出基带波形信号;

[0040]

s4:所述dac芯片接收所述基带波形信号,将其转换为模拟信号,并完成上变频操

作后输出中频信号;

[0041]

详细的,如图2所示:

[0042]

所述s1具体包括:信号源输入120mhz、240mhz同源时钟,120m作为fpga的系统时钟,240m作为dac芯片的采样时钟。

[0043]

所述120mhz系统时钟通过sma形式的连接器输入给时钟分发芯片,由时钟分发芯片为fpga芯片的时钟分配和监测模块提供所需时钟,所述时钟分配和监测模块用于时钟分发,为fpga芯片提供120mhz系统时钟。

[0044]

上位机通过单模光纤下发系统控制信息,系统的控制信息主要包括时序信息和波形信息。

[0045]

s3具体包括,

[0046]

fpga芯片模块包括gtx接口模块、控制字解析模块、时序同步信号产生模块、波形参数管理模块、波形产生模块、dac接口模块和时钟分配和监测模块。

[0047]

gtx接口模块接收上位机下发的控制信息,输出同步基准脉冲和控制参数,所述基准脉冲作为驻留周期起始输入到所述时序同步信号产生模块;

[0048]

所述控制参数由控制字解析模块进行参数解析后得到时序参数和波形参数,所述时序同步信号产生模块根据所述时序参数产生参差波形的触发脉冲(trig_da1、trig_da2

……

),所述波形参数管理模块接收所述波形参数和所述触发脉冲(trig_da1、trig_da2

……

),根据触发脉冲(trig_da1、trig_da2

……

)输出对应的波形参数,所述波形产生模块接收所述输出波形对应的波形参数产生基带波形信号并输出给所述dac接口模块。

[0049]

所述dac接口模块将基带波形数据传输至dac芯片,由dac芯片将数字信号转换为模拟信号,并根据所述波形参数的上变频频率在dac芯片内部完成上变频操作,将基带波形信号上变频至中频信号输出,所述中频信号输入至示波器查看输出信号。

[0050]

所述时钟分配和监测模块接收所述时钟分发芯片发出的120mhz系统时钟,为系统提供基准时钟。

[0051]

另一方面,本发明实现了一种参差脉冲波产生的系统。

[0052]

如图3所示,所述系统具体包括:

[0053]

基准单元,用于为所述信号产生单元和所述数模转换单元提供基准信号;

[0054]

控制单元,用于下发控制信息,所述控制信息包括时序信息和波形信息;

[0055]

信号产生单元,用于根据所述控制信息输出基带波形信号;

[0056]

数模转换单元,接收所述基带波形信号并将其转换为模拟信号。

[0057]

具体的,

[0058]

所述基准单元包括信号源、时钟分发芯片和时钟分配和监测模块,所述信号源输入120mhz和240mhz同源时钟,120m作为fpga的系统时钟;240m作为dac芯片的采样时钟。

[0059]

所述控制单元包括上位机,用于下发控制信息,所述控制信息包括时序信息和波形信息;

[0060]

所述信号产生单元包括gtx接口模块、控制字解析模块、时序同步信号产生模块、波形产生模块和dac接口模块。

[0061]

gtx接口模块接收所述控制信息并输出同步基准脉冲和控制参数,所述基准脉冲作为驻留周期起始输入到所述时序同步信号产生模块;

[0062]

所述控制参数由控制字解析模块进行参数解析后得到时序参数和波形参数,所述时序同步信号产生模块根据所述时序参数产生参差波形的触发脉冲(trig_da1、trig_da2

……

),所述波形参数管理模块接收所述波形参数和所述触发脉冲(trig_da1、trig_da2

……

),根据触发脉冲(trig_da1、trig_da2

……

)输出对应的波形参数,所述波形产生模块接收所述输出波形对应的波形参数后产生基带波形信号并输出给所述dac接口模块。

[0063]

数模转换单元包括dac芯片,所述dac接口模块接收到基带波形信号并将其发送给dac芯片,dac芯片完成数模转换并根据所述波形参数的上变频频率在dac芯片内部完成上变频操作,将基带波形信号上变频至中频信号输出。

[0064]

显然,本发明的上述实施例仅仅是为清楚地说明本发明所作的举例,而并非是对本发明的实施方式的限定,对于所属领域的普通技术人员来说,在上述说明的基础上还可以做出其它不同形式的变化或变动,这里无法对所有的实施方式予以穷举,凡是属于本发明的技术方案所引伸出的显而易见的变化或变动仍处于本发明的保护范围之列。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1